Вычислительное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в электронных вычислительных машинах. С целью повыиения быстродействия вычислительное устройство,, включающее арифметико-логический блок 1, сдвигатель 2, буферные регистры 3,8,9, коммутатор 4, блок 5 адресуе мых регистров и регистр 6 результата, дополнительно содержит регистр 7 информации с соответствующими связями. 2 ил,

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (g1) g G 06 F //38

О ИКАНИЕ ИЗОБРЕТЕНИЯ

К ASTOPGHOIVIY СВИДЕТЕЛЬСТВУ

18

Ю

12

13

26

27

29

28

29

ФигЛ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4090698/24-24 (22) 05.05.86 (46) 23. 06. 88. Бюл. У 23 (72) А.Е. Саркисян, В. Н. Газиян, P.К.Бзнуни и Г.С.Гаспарян (53) 681.325 (088.8) (56) Авторское свидетельство СССР

М 885993, кл. G 06 F 7/38, 1980.

Микропроцессорные комплекты интегральных схем. Состав и структура./

Под ред. А.А.Васенкова, В.А.Шахнова.—

М.: Радио и связь, 1982, с. 143, рис.9.1.

„„SU„„ I 405047 А 1 (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и может быть использовано в электронных вычислительных машинах. С целью IIQBblllpHHH быстро. действия вычислительное устройство, включающее арифметико-логический блок

1, сдвигатель 2, буферные регистры

3,8,9, коммутатор 4, блок 5 адресуемых регистров и регистр 6 результата, дополнительно содержит регистр 7 информации с соответствующими связями.

2 ил.

1405047

Изобретение относится к вычислительной технике и может быть использовано в 3BN.

Цель изобретения — повышение быст- 5 родействия.

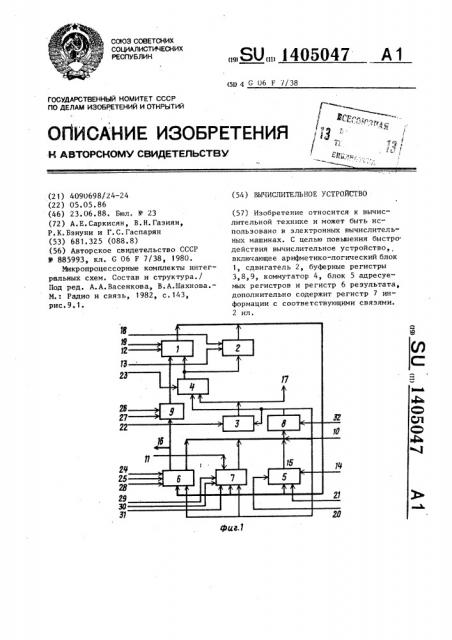

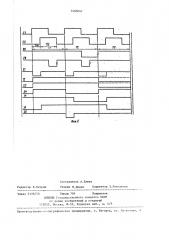

На фиг. 1 представлена схема вычислительнога устройства; на фиг.2 временная диаграмма работы вычислительного устройства. 10

Вычислительное устройство содержит арифметика-логический блок 1, сдвигатель 2, буферный регистр 3, коммутатор 4, блок 5 адресуемых регистров, регистр 6 результата, регистр 7 ин- tl5 формации, буферные регистры 8 и 9, информационные входы 10 и 11 устройства, вход 12 задания вида операции устройства, вход 13 задания величины сдвига устройства, адресный вход 14 20 устройства, выход 15 блока 5, выход

16 результата устройства, выход 17 адреса устройства, тактовые входы 1832 устройства. Регистры, использованные в устройстве, реализованы на мно-25 гафункциональнам элементе К155хЛ1.

На фиг.2 приведены временные диаграммы поступления основных управляющих сигналов в соответствии с синхросигналами С1 и С2 (входы синхронизации 30 на фиг. 1 не показаны), нумерация соответствует нумерации блоков и входов устройства.

Устройство работает следующим образом.

При выполнении двухадресных операций, когда оба операнда (источник и приемник) н аходя тся в адресуемых регистрах (блок 5), получается выигрыш во времени за счет сокращения 40 количества машинных тактов, Например, при выполнении операции сложения. содержимого регистра R2 с содержимым регистра R1 в первом такте (Т1) содержимое из регистра R2 поступает в 45 регистр 8 и передается из него в регистр 6. Во втором машинном такте (Т2) содержимое регистра К1 считывается на регистр 8, а первый операнд из регистра 6 — на регистр 9, на вы- 50 ходе блока 1 появляется результат операции, который записывается в регистре 6 и в блок 5 по адресу приемника (R1). Временная диаграмма выполнения двух адресных команд типа регистр-регистр приведена на фиг.2.

Двухсторонняя связь регистра 7 информации с входом 11 позволяет во время одного цикла обращения к oneративной памяти прочитать два операнда (адрес или данные). Младший операнд с входа 10 устройства поступает в регистр 8, где запоминается. Старший операнд поступает с входа 11 устройства в регистр 7. После этого младший операнд можно записать в регистр

6 или в буферный регистр 3 или сразу использовать его как первый операнд для выполнения операции. Ьазможно совмещение выполнения операций над операндами, хранящимися в регистрах

8 и 9, с приемом операндов в регистры

Зи7.

Если один из операндов находится в оперативной памяти, а второй — в одном из адресуемых регистров блока

5, та операнд, находящийся в блоке 5, считывается в регистр 8 и принимается в регистр б,второй операнд считывается из оперативной памяти па адресу содержимого регистра 3 в регистр 8 с одновременной выдачей первого операнда в регистр 9 и выполняется операция. Коммутатор 4 при этом посылает на вход блока 1 и сдвигателя 2 информацию, которая хранится в регистре 8.

Формула изобретения

Вычислительное устройство, содержащее арифметика-логический блок, сдвигатель, коммутатор, три буферных регистра, блок адресуемых регистров и регистр результата, причем выход арифметика-логического блока объединен с выходом сдвигателя и соединен с информационным входом блока адресуемых .регистров и с первым информационным входом регистра результата, пер1 вый выход которого является выходом результата устройства, входы задани вида операции и величины сдвига которого соединены соответственно с входом вида операции арифметика-логического блока и входом величины сдвига сдвигателя, входы разрешения выдачи арифметика-логического блока и сдвигателя соединены соответственно с первым и вторым тактовыми входами устройства, адресный вход катарога соединен с входом адреса блока адресуемых регистров, входы разрешения записи и разрешения выдачи катарага соединены соответственно с третьим и четвертым тактовыми входами устранства пятый тактовый вход которого

В соединен с входам разрешения записи

1405047 первого буферного регистра, выход которого является выходом адреса устройства, первый информационный вход которого объединен с выходом блока адресуемых регистров, с вторым выходом регистра результата и соединен с информационным входом второго буферного регистра, управляющий вход коммутатора соединен с шестым тактовым входом устройства, седьмой и восьмой тактовые входы которого соединены соответственно с первым и вторым входами разрешения выдачи регистра результата, выход третьего буферного регистра соединен с первым информационным входом арифметико-логического блока, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит регистр информации, причем выход первого буферного регистра соединен с первьи информационным входом коммутатора, выход которого соединен с вторым информационньм входом арифметико-логического блока и с информационным входом сдвигателя, первые информационные входы регистров результата и информации объединены, выход второго бу= ферного регистра соединен с информационным входом первого буферного регистра, с вторым информационным входом коммутатора, с объединенными вторыми информационными входами регистров результата и информации, первый выход регистра информации соединен с информационным входом второго буферного регистра, второй выход и третий информационный вход регистра информации объединены и соединены с вторым информационным входом устройства, первый выход регистра результата соединен с информационным входом третьего буферного регистра, входы разрешения записи и установки в "0" которого соединены соответственно с девятым и десятым тактовыми входами устройства, !

20 вход направления приема регистра результата, первый и второй входы разрешения выдачи регистра информации, вход направления приема регистра информации, вход установки в "0" вто25 рого буферного регистра соединены соответственно с тактовыми входами с одиннадцатого по пятнадцатый устройства.

1405047

Составитель А.Клюев

Текред М.Дидык

Корректор Э.Лончакова

Редактор В.Петраш

Заказ 3106/53

Тираж 704 Подписное

ВПИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Нраизводственнс -н >лиграфическое предприятие, г. Ужгород, уп. Проектная, 4