Устройство для измерения частот появления групп команд

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для оптимизации системы команд ЭВМ с целью сокращения обьема занимаемой памяти и времени выполнения программ Целью изобретения является расширение области применения устройства за счет измерения частоты поя вления одного сочетания следующих одна за другой команд для последующего определения целесообразности создания одной команды, способной заменить эту группу команд. Устройство для измерения частот появления команд содержит счетчик 1 адреса,три элемента ИЛИ 2, 3 и 4, элемент И 10 и триггер 7, блок 8 буферной памяти и блок 9 формирования.групп команд для формирования групп команд заданного размера и выдачи этой информации в блок буферной памяти, 2 ил. i (Л СП О О) tN9

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУбЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОбРЕТЕНИЙ И ОТКРЫТИЙ (2) ) 4170418/24-24 (22} 30,1 2,86 (46) 23.06.88. Бюл, ¹ 23 (72) С.В.Трунков, В.А.Батраков, А.В.Мурин, С.В.Назаров и М.Т.Акуленок (53) 681.3 (088.8) (56) Авторское свидетельство СССР № 980096, кл. С 06 У 11/28, 1982.

Авторское свидетельство СССР № 1357963, кл. G 06 F 11/26, 1986. (54) УСТРОЙСТВО ДНЯ ИЗИЕРЕНИЯ ЧАСТОТ

ПОЯВЛЕНИЯ ГРУПП КОМАНД (57) Изобретение относится к вычислительной технике и может быть использовано для оптимизации системы команд ЭВМ с целью сокращения объема

„„SU„„1405062 А1 (51)4 G 06 F 1 I/28 занимаемой памяти и времени выполнения программ. Целью изобретения является расширение области применения устройства за счет измерения частоты появления одного сочетания следующих одна sa другой команд для последующего определения целесообразности создания одной команды, способной заменить эту группу команд. Устройство для измерения частот появления команд содержит счетчик 1 адреса три элемента ИЛИ 2, 3 и 4, элемент И 10 и триггер 7, блок 8 буферной памяти и блок 9 формирования. групп команд для формирования групп команд заданного размера и выдачи этой информа" ции в блок буферной памяти. 2 ил.

1405062

Изобретение относится к вычислительной технике и может быть использовано для оптимизации системы команд ЭВМ с целью сокращения объема занимаемой памяти и времени выполнения программ.

Цель изобретения — расширение области применения устройства путем обеспечения возможности измерения частоты появления одного и того же сочетания следующих одна за другой команд для последующего определения целесообразности создания одной команды, способной заменить эту 15 группу (последовательность ) .

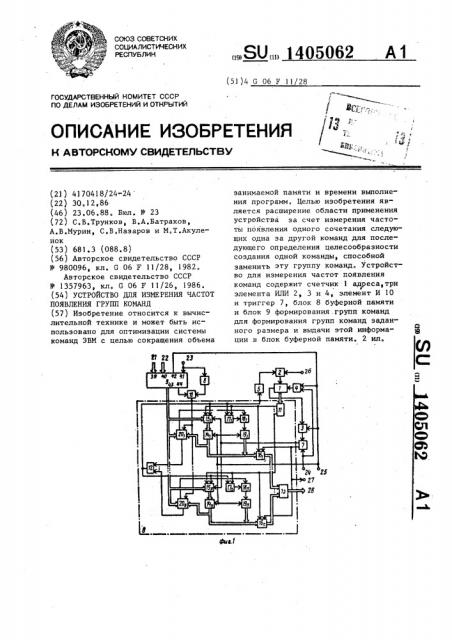

На фиг. 1 и 2 приведена структурная схема устройства для измерения частот групп команд.

Устройство содержит счетчик 1 ад" реса, элементы ИЛИ 2-- 4, элементы

5 и 6 задержки„.триггер 7, блок 8 буферной памяти, блок 9 формирования группы команд и элемент 1И 10.

Блок 8 буферной памяти содержит 25 дешифратор 11, элемент И 12, группу элементов ИЛИ 13, 1V запоминающих ячеек (где Н - количество анализируемых групп команд), каждая иэ которых включает регистр 14, группы элементов

И 15 и 16, элемент И 17, элемент

ИЛИ 18, счетчик 19 импульсов.и схему

20 сравнения.

Кроме того, устройство содержит входы 21 и 22, тактовый вход 23, вход

Зэ

24 чтения, вход 25 начальной установ-ки, вход 26 признака конца считывания, выход 27 готовности и выход 28 результата.

Блок 9 формирования группы команд (фиг.2) содержит регистр 29, счетчик

30, дешифратор 31, схему 32 сравнения, элемент И 33, элемент 34 задержки, М ячеек кодов команд (где М вЂ” количество команд, входящих в анализируемую группу), каждая иэ которых ,включает (кроме М-й ячейки) регистр . 35 команды, группу элементов ИЛИ 36, группы элементов И 37 и 38, N-я ячейка содержит регистр 35 команды и группу элементов И 37, информационные входы 39 и 40, тактовый вход 41, вход 42 начальной установки, информационный выход 43 и выход 44.

Устройство работает следующим об) разом.

Первоначально на вход 25 устройства поступает сигнал, который обнуля-ет содержимое регистров 14 и счетчиков 19 всех ячеек блока 8, через элемент ИЛИ 4 обнуляет счетчик l адреса, через элемент ИЛИ 3 сбрасывает триггер 7 и через вход 42 блока 9 обнуляет содержимое счетчика 30 и регистров 35 команд всех ячеек блока 9. На единичном выходе триггера 7 устанавливается низкий потенциал, который через выход 27 устройства сигнализирует ЭВМ о готовности устройства к анализу команд программы, Высокий потенциал с инверсного выхода триггера 7 поступает на входы элементов И 15 группы каждой ячейки, разрешая запись информации в блок 8.

Код, установленный на группе выходов счетчика 1 адреса (нулевой), поступает на дешифратор ll блока 8, на соответствующем выходе которого (первом) устанавливается высокий потенциал, который поступает на входы элементов И !5 группы соответствующей ячейки (первой) блока 8, разрешая тем самым запись в данную ячейку, С информационного входа 22 устройства в регистр 29 блока 9 поступает код количества команд, образующих исследуемую группу команд, программы (группа, в общем случае, состоит иэ одной и более команд). Этот код поступает на вход дешифратора

31, на соответствующем выходе которого устанавливается высокий потенциал, который поступает на первые входы элементов И 37 группы соответствующей ячейки блока 9, разрешая запись очередного кода команды в данную ячейку. В случае неравенства кодов,,находящихся на регистре 29 и счетчи,ке 30 блока 9 (а в начале так и ! будет), низкий потенциал с первого .выхода схемы 32 сравнения запрещает прохождение тактовых сигналов через элемент И 10 устройства в блок 8, а высокий потенциал с второго выхода схемы 32 сравнения блока 9 разрешает поступление этих сигналов через элемент И 33 на счетный вход счетчика 30 блока 9.

Устройство готово к работе. Работа устройства в режиме анализа, ко-. манд программы и записи этой информации в блок 8 состоит из двух этапов. На первом этапе осуществляется формирование первой иэ возможных комбинаций (групп) команд. Это происходит следующим образом. На вход 21

1405062 устройства поступают коды команд исследуемой программы, которые сопровождаются тактовыми сигналами, поступающими на вход 23 устройства. По первому тактовому сигналу (для всех

i-х- ячеек, i = 2, М) осуществляется перепись информации, содержащейся в регистре 35 команды i-й ячейки через группу элементов И 38 и группу элементов ИЛИ 36 в регистр 35 команды (i-l)-й ячейки (аналогичные дейст" вия выполняются при поступлении последующих тактовых сигналов).

Одновременно тактовый сигнал через открытый элемент И 33 поступает на счетный вход счетчика 30 и увеличивает его содержимое на единицу.

Через время, достаточное для переписи информации из i-х в (i-1)-е регистры 35 команд (i=2,М), . с выхода элемента 34 задержки поступает сигнал, по которому очередной код команды через соответствующую группу элементов И 37 (предварительно открытую высоким потенциалом с соответ" ствующего. выхода дешифратора 31) и группу элементов ИЛИ 36 заносится в соответствующий регистр 35 команды (аналогичные действия выполняются при поступлении последующих тактовых сигналов). На данном этапе (такте) информация с группы информационных выходов 43 блока 9 присутствует на информационном входе блока 8, но в ячейки памяти блока 8 не записываЙтся, так как тактовый сигнал, появляющийся на выходе элемента 6 задержки через время, достаточное для занесения информации в соответствующую ячейку кода команд блока,9, не подается на тактовый вход блока 8, .поскольку элемент И 10 закрыт.

Описанные действия повторяются до тех пор, пока код, сформированный в счетчике 30 блока 9. при поступлении тактовых сигналов, не станет равным коду, хранящемуся в регистре 29 блока 9, При этом низким потенциалом с второго выхода схемы 32 сравнения блокируется изменение состояния счетчика 30, и высоким потенциалом с первого выхода разрешается поступление тактовых сигналов на тактовый вход блока 8.

На втором этапе работы .устройства в режиме анализа команд программы осуществляется запись этой инфор20

25 И 15 первой группы всех ячеек блока

8. По этому сигналу информация с ин50

5

45 мации в блок 8. Это.происходит следующим образом.

На первую группу информационных входов схемы 20 сравнения каждой ячейки поступает код с информационного выхода блока 9, на вторую группу информационных входов схемы 20 сравнения каждой ячейки блока 8 поступает код, хранящийся в данный момент времени на регистре 14 соответ.— ствующей ячейки блока 8. Возможны два случая.

В случае, если ни в одном регистре 14 ячеек блока 8 не содержится кода, соответствующего коду группы команд (а при первой записи так и будет), все схемы 20 сравнения при поступлении управляющего сигнала вырабатывают на втором выходе сигнал несравнения. Тогда на выходе элемента

И 12 блока 8 формируется сигнал, который поступает на второй вход элемента И 17 и третьи входы элементов формационного выхода блока 9 через соответствующую первую группу элементов И 15 переписывается в регистр 14 ячейки блока 8, в которую дешифратором 11 блока 8 разрешена запись (в начале работы в первую ячейку).

Этот же сигнал, пройдя через соответствующие элемент И 17 и элемент

ИЛИ 18, заносит в счетчик 19 данной ячейки (первой) блока 8 единицу. Сигнал с выхода элемента И 12 блока 8 поступает на вход первого, элемента

5 задержки, Сигнал, формируемый на. выходе первого элемента 5 задержки, пройдя через элемент. ИЛИ..2, увеличивает содержимое счетчика 1 адреса на единицу. Тем самым определяется смежная ячейка блока 8 для записи инфор-. мации при возникновении ситуации, аналогичной описанной.

В случае, если в регистре 14 одной из ячеек блока 8 к моменту выдачи сигнала с выхода элемента И 10 хранится код группы команд, записанный ранее, то с приходом сигнала на тактовый вход схем 20 сравнения только соответствующая схема 20 сравнения выработает на первом выходе сигнал сравнения, который через соответствующий элемент ИЛИ 18 увеличит содержимое соответствующего счетчика 19 на единицу.

1405062

В момент окончания работы по анализу исследуемой программы в блоке

8 будет храниться информация, содержащая коды групп команд и частоты их использования в программе.

Считывание содержимого блока 8 осуществляется следующим образом.

ЭВМ вырабатывает сигнал, который поступает на вход 24 устройства. Этот сигнал устанавливает в единичное состояние триггер 7, на единичном выходе которого устанавливается высокий потенциал, который через выход

27 устройства выдается в ЭВМ, сигна" лизируя о готовности устройства к работе в режиме чтения. Высокий потенциал с единичного триггера 7 поступает на вторые входы элементов И 16 второй группы всех ячеек блока 8,разрешая тем самым считывание информации из блока 8, Одновременно управляющий сигнал, поступающий на вход

24 устройства, через третий элемент

ИЛИ 4 устанавливает в нулевое состоя.ние счетчик 1 адреса. Появляющийся высокий потенциал на соответствующем выходе дешифратора 11 блока 8 {первом)„ поступая на первые входы эле" ментов И 16 второй группы соответствующей ячейки блока 8 (первой}, раз" решает считывание информации, хранящейся в данной ячейке {содержимого регистра 14 и счетчика 19) блока 8.

Эта информация через группу 13 элементов ИЛИ блока 8 поступает на группу информационных выходов 28 устройства. На вход 26 устройства из ЭВМ начинают поступать сигналы с частотой, обеспечивающей считывание информации из одной ячейки блока 8. Каждый такой сигнал через элемент ИЛИ 3 увеличивает содержимое счетчика 1 адреса, тем самым разрешая считывание информации из смежной ячейки блока 8. После считывания информации из последней ячейки блока 8 очередной сигнал, поступивший на вход 26 устройства, обнуляет счетчик 1 адреса, и импульс сквозного переноса поступает с выхода переполнения счетчика 1 адреса через элемент. ИЛИ 2 на вход установки в нулевое состояние триггера 7. На единичном выходе триггера 7 появляется нулевой потенциал, который запрещает считывание информации.

Одновременно он поступает через выход 27 устройства в ЭВМ, сигнализируя об окончании режима чтения.

При необходимости изменения количества команд в группе, соответствующей код количества команд заносится в регистр 29 блока 9. После начальной установки работа устройства происходит описанным образом.

Формула и з о б р е т е н и я

Устройство для измерения частот появления групп команд, содержащее счетчик адреса, три элемента ИЛИ, два элемента задержки, триггер и блок буферной памяти, причем выход признака наличия информации блока буферной памяти через первый элемент задержки соединен с первым входам первого элемента ИЛИ, выход которого соединен со счетным входом счетчика адреса, информационный выход счетчика адреса соединен с адресным входом блока буферной памяти, информационный выход которого является выходом результата работы устройства, вход чтения устройства соединен с еднничным входом триггера и с первым входом второго элемента ИЛИ, вход начальной установки устройства соединен с вторым входом второго элемента ИЛИ, с первым входом третьего элемента ИЛИ и с входом сброса блока буферной памяти, вьгход второго элемента ИЛИ соединен с входом начальной установки счетчика адреса, выход переполнения которого соединен с вторым входом третьего элемента ИЛИ, выход третьего элемента ИЛИ соединен с нулевым входом триггера, инверсный выход которого соединен с входом записи блока буферной памяти, единичный выход триггера является выходом готовности устройства и соединен с. входом чтения блока буферной памяти, вход признака конца считывания устройства соединен с вторым входом первого элемента ИЛИ, тактовый вход устройства соединен с входом второго элемента задержки, о т— л и ч а ю щ е е с я тем, что, с целью расширения области применения устройства путем обеспечения возможности измерения частоты появления одних и тех же сочетаний групп команд, в него введены элемент И и блок формирования группы команд, содержащий дешифратор, счетчик, схему сравнения, элемент И, элемент задержки, регистр, M ячеек команд (где М вЂ” максимальное количество команд, входя1 05062 б с в

5 в

7 щих в анализируемую группу), а каждая ячейка, кроме M-й, содержит регистр команд, группу элементов ИЛИ, две группы элементов И, М-я ячейка содержит регистр команд и группу элементов И, причем информационный вход кода команд устройства соединен с первыми входами элементов И первой группы каждой ячейки команд блока 10 формирования группы команд, тактовый вход устройства соединен с первым входом элемента И блока формирования группы команд, с первыми входами элементов.й второй группы г-й ячейки 1Б команд, где х -й1, (М-1), блока формирования группы команд и через элемент задержки — с вторыми входами элементов И первой группы каждой ячейки команд. блока формирования 20 группы команд, выход второго элемента задержки соединен с первым входом элемента И, информационный вход устройства соединен с информационным входом регистра блока формирования 25 группы команд, вход начальной установки устройства соединен с входами обнуления счетчика и регистров команд всех ячеек команд блока формирования группы команд, информационный gp выход регистра соединен с входом дешифратора и первым входом схемы сравнения блока формирования группы команд, информационный выход счетчика соединен с вторым входом схемы срав" нения блока формирования группы ко" манд, выходы равенства и неравенства схемы сравнения соединены соответственно с вторым входом элемента И

8 лака формирования группы команд и вторым входом элемента И устройста, выход которого соединен с тактоым входом блока буферной памяти,выход элемента И блока формирования группы команд соединен со счетным входом счетчика блока формирования группы команд, К-й выход дешифратора, где К - 1,М, соединен с третьими входами элементов И первой группы

i-й ячейки команд блока формирования группы команд, выходы элементов И первой группы i-й ячейки команд соединены с первыми входами элементов

ИЛИ группы i-й ячейки блока формирования группы команд, информационный выход регистра команд -й ячейки команд, где j - 2,М, блока формирования группы команд соединен с информационным входом блока буферной памяти и с вторыми входами элементов И второй группы (j-1)-й ячейки команд блока формирования группы команд, информационный выход регистра первой ячейки, соединен с информационным входом блока буферной памяти, выходы элементов И второй группы i-й ячейки команд соединены с вторыми входами элементов:

ИЛИ группы i-й ячейки команд, выходы элементов ИЛИ группы i-й ячейки команд соединены с информационными входами регистра команд i-й ячейки команд блока формирования группы команд, выходы элементов И группы М-й ячейки команд соединены с информационными входами регистра команд М-й ячейки команд блока формирования группы команд.

1405062

Составитель И. Сигалов

Техред N.ÄHäûê Корректор Г Решетник

Редактор А.Шандор

Эаказ 3107/54

Тираж 704 Подписное

В11ИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4