Устройство приема и передачи информации в эвм

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к организации каналов приема и передачи информации между процессорами (ЭВМ) и внешними устройствами по единому унифицированному каналу связи.Цель изобретения - сокращение аппаратурных затрат при организации канапов обмена информацией между несколькими процессорами и внешними устройствами . Устройство приема и передачи информации в ЭВМ содержит две груп-- пы приемопередатчиков 1 - 4 и имитатор 5 внешних устройств Имитатор 5 выполнен в виде дешифратора адресов регистров имитируемых периферийных устройств. 2 ил. с

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (511 4 G Об F 15/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ г

Е! к

3>

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21 ) 4121615! 24-24 (22} 18,09,86 (46) 23.06.88.Бюл. У 23 (72) В.Л.Варго, А.А.Дворников, А,М,Ткаченко и А.Ф.Лазарчук (53) 681.325 (088.8) (56) Авторское свидетельство СССР

У 634260, кл. G 06 F 13/00, 1978.

Простой разветвитель интерфейса для микроЭВМ "Электроника 60-М", Приборы и техника эксперимента, 1983;

М 2, с. 63..(54) УСТРОЙСТВО ПРИЕМА И ПЕРЕДАЧИ

ИНФОРМАЦИИ В ЭВМ (57) Изобретение относится к вычисли"

ÄÄSUÄÄ 1405068 А1 тельной технике, в частности к организации каналов приема и передачи информации между процессорами (ЭВМ) и внешними устройствами по единому унифицированному каналу связи. Цель изобретения — сокращение аппаратурных затрат при организации каналов обмена информацией между несколькими процессорами и внешними -устройствами. Устройство приема и передачи информации в ЭВМ содержит две груп-. пы приемопередатчиков 1 — 4 и имитатор 5 внешних устройств. Имитатор

5 выполнен в виде дешифратора адресов регистров имитируемых периферий- ! ных устройств. 2 ил.

1405068!

Изобретение относится к вычислиельной технике, и может быть использовано преимущественно при oprанизасии кайалов приема и передачи инфорации между процессорами (ЭВМ) и доliолнительными устройствами по единому унифицированному каналу связи.

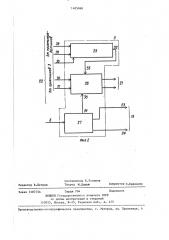

Цель изобретения — сокращение ап1 аратурных затрат при организации 10 аналов обмена информацией между нес" олькими процессорами и внешними устойствами.На фиг.1 изображена блок-схема стройства приема и передачи информа- 15 и в 3BN; на фиг. 2 — функциональая схема имитаторов внешних устойств.

Устройство приема и передачи инормации в ЭВМ содержит приемопере- 20 атчик 1 и. 2 первой группы приемопеедатчиков, приемник 3 и передатчик второй группы приемопередатчиков, итатор 5 внешних устройств, входы"

ыходы 6 — 22 блоков. 25

Имитатор 5 содержит (фиг.2} выхоМ 23 и 24 схемы включения=выключе" ия канальных передатчиков, дешифраор.25 адресов имитируемых регистов, схему 26 формирования сигналов 30

OTBL и NAD07L схему 27 включенияыключения канальных передатчиков, 1 ходы-выходы 28 — 36 блоков.

Устройство работает следующим образом. 35

При подаче на вход 6 выбора режима работы имитатора 5 низкого уровня напряжения схема 27 формирует на выходе 23 низкий уровень сигнала, кото рый поступает на входы 13 и 14 разре- 40

| шения приемопередатчиков первой груп пы. На выходе 24 схема 27 формирует высокий уровень напряжения, который поступает на входы lá приемопередатчиков второй группы. При этом пере- 45 датчики приемопередатчиков 1 и 2 и передатчики 4 открываются. На выходе 34 схема 27 формирует пассивный уровень сигнала, закрывающий по входу 35 передатчики выходного каскада 50 схемы 26. Активным считается высокий уровень сигнала, а пассивным — низкий. Процессор (не показан) в данном режиме проводит обмен сигналами с внешними устройствами (не показаны), 55 получая от внешних устройств необходимые для нормальной работы процессора сигналы NOTBL и MAD07L. При этом сигналы NOTBL и MAD07L, формируемые схемой 26, через закрытые передатчики этой схемы в канал процессора не передаются и не влияют на работу процессора.

При подаче на вход б выбора режима работы имитатора 5 высокого уровня напряжения схема 27 формирует на.выходе 23 высокий уровень сигнала, закрывающий по входам 13 и 14 передатчики приемопередатчиков 1 и

2, на выходе 24 низкий уровень сигнала, закрывающий по входам 16 передатчики 4, и на выходе 34 активный уровень сигнала, открывающий передатчики выходного каскада схемы 26. При этом процессор не имеет возможности обмениваться сигналами с внешними устройствами. Процессор периодически организует в канале цикл обращения

"Ввод" к регистру внешнего устройства с фиксированным адресом. При этом на входы 28 и 36 дешифратора 25 поступают сигналы AD01H — АЭ11Н и ВУН (соответствующие фиксированному адресу) от приемников приемопередатчиков 1 и от приемников 3 соответственно. Логической "1" каждого сигнала соответствует высокий уровень. Дешифратор 25 формирует на выходе 32 активный уровень сигнала, После этого процессор формирует в канале сигнал

NOBN, который передается через приемник 3 на вход 29 дешифратора 25 высоким уровнем (ОБМН). По приходу сигнала ОБМН дешифратор 25 фиксирует. на выходе 32 активный уровень сигна. ла на весь канальный цикл обращения

"Ввод", после этого процессор формирует в канале сигнал TL который передается через приемник 3 на вход

31 схемы 26 высоким уровнем (ДЧТН);

По приходу на вход 31 сигнала ДЧТН при наличии на входе 33 активного уровня сигнала схема 26 формирует и передает через свои передатчики выходного каскада в канал процессора сигналы NOTBL и NAD07Lq Процессор, получив из канала эти сигналы, заканчивает цикл "Ввод", снимая в канале сигнал NOSML, который через передатчики 3 снимает на входе 29 дешифратора 25 сигнал ОБМН.

Дешифратор 25 на выходе 32 формирует -пассивный уровень сигнала, который формирует на выходах 21 схемы

26 пассивные уровни сигналов NOTBL и МАЭ07Ь. Процессор, получив в цикле

"Ввод" от схемы 26 сигналы MOTBL u

MAD07L, организует в канале процессора цикл вывода по фиксированному адресу. При этом на входы 28 и 36 дешифратора 25 через приемники приемопередатчиков 1 и приемник 3 поступают сигналы AD01H — ADllH ВУН, соответствующие адресу 177566. Дешифратор 25 формирует на выходе 32 активный уровень сигнала. Далее процессор формирует в канале сигнал MOSML, который через приемник 3 передается на вход 29 дешифратора 25 и фиксирует на его выходе 32 активный уровень сигнала на весь канальный цикл "Вывод". После этого процессор формирует в канале сигнал МДЗПЬ, который через приемник 3 поступает на вход

30 схемы 26 (ДЗПН), по приходу которого и при наличии на входе 33 активного уровня сигнала схема 26 формирует на выходе 21 сигнал MOTBL. Процессор по получении сигнала MOTBL заканчивает цикл обращения "Вывод", снимая в канале сигналы MOSML u

МДЗПЬ, которые, в свою очередь, че" рез приемники 3 снимают сигналы

ОБМН и ДЗПН на входе 29 дешифратора

25 и .на входе 30 схемы 26 соответственноь Схема 26 формирует на выходе

21 пассивный высокий уровень сигнала

MOTBL. Далее процессор выполняет программу до вывода следующей информации на внешние устройства. При этом процессор снова организует цикл

"Ввод" по фиксированному адресу, анализирует полученный сигнал MAD07L и организует цикл "Вывод" по этому

5068 адресу в указанной выше последовательности. Тем самым имитатор 5 обеспечивает непрерывную работу процессора, отключенного передатчиками 1 "-3 от канала внешних устройств, Формула изобретения

Устройство приема и передачи ин10 формации в ЭВМ, содержащее первую и вторую группы приемопередатчиков, причем первый и второй информационные входы-выходы приемопередатчиков первой группы являются первым и вторым

15 информационными входами-выходами уст" ройства,соответственно, управляющий вход приемопередатчиков второй группы является управляющим входом устройства, управляющий выход приемопере20 датчиков второй группы является уп» равляющим выходом устройствй, о т— л и ч а ю щ е е с я тем, что, с целью сокращения аппаратурных затрат при > организации каналов обмена информацией между несколькими процессорами и внешними устройствами, введен имитатор внешних устройств, управляющий вход которого является входом задания режима работы устройства, управ30 ляющий выход имитатора внешних устройств соединен с входами разрешения приемопередатчиков первой и второй групп, выход адреса имитатора внешних устройств является адресным вьг ходом устройства, информационный вход имитатора внешних устройств соединен с информационными выходами приемопередатчиков первой и второй групп

1405068

Составитель Е.Устинов

Техред M.Дидык

Корректор O,Kðàâöoâà

Редактор В.Петраш

Тираж 704

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 3107/54

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4