Устройство для решения системы линейных алгебраических уравнений

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для решения систем линейных алгебраических уравнений. Цель изобретения - повышение быстродейст ВИЯ устройства. Поставленная цель достигается тем, что устройство соблок 1 памяти, первый сумма-. тор 2, регистр 3, блок 4 управления, второй сумматор 5, р мультиплексоров 6, где р - разрядность представления информации, р сдвигающих регистров 7, р групп по N блоков 8 памяти, где N - порядок системы уравнений, группу из р сумматоров 9. 1 з.п. флы, 5 йл., 2 табл.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (5D 4 G 06 F 15/324

ОПИСАНИК ИЗОВРКткНия

Н А BTOPCH0MV СВИДЕТЕЛЬСТВУ

4ь ,4Р

Сп

Ю

° ь )

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21 ) 4089036/24-24 (22) 14.07.86 (46) 23,06.88. Бюл. У 23 (71) Институт кибернетики им. В.M.Ãëóøêîâà (72) В.П.Деркач, А.А.Мержвинский, В.И.Панчук, Л.В.Старикова и А.П.Голо.ватый

В (53) 681.325(088.8) (56) Авторское свидетельство СССР

У 922762, кл . G 06 F 15/324, 1979.

Авторское свидетельство СССР

У 813445, кл. G 06 F 15/324, 1978. (54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМЫ

ЛИНЕЙНЫХ. АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ

„„SU„„1405073 A i (57) Изобретение относится к вычислительной технике и может быть испальзовано для решения систем линейных алгебраических уравнений. Цель изобретения — повышение быстродейст" вия устройства. Поставленная цель достигается тем, что устройство содержит блок 1 памяти, первый сумма-. тор 2, регистр 3, блок 4 управления, второй сумматор 5, р мультиплексоров 6, где р — разрядность представления информации, р сдвигашщих регистров 7, р групп по И блоков 8 памяти, где N — порядок системы уравнений, группу из р сумматоров 9. 1 з,п. флы, 5 ил., 2 табл.

1405073 2

Изобретение относится к вычислительной технике и может быть исполь зовано для решения систем линейных алгебраических уравнений

A(t) ° %=y{t); (А(С}(фО;

te l0,Òl, (1) где A(t}-(n7n} — матрица типа теплицевых, составленная из численно опреде- 10 ляемых коэффициентов а о(1 ) а 1(t )... а1 „{ 1 ) а1()ао(t) à ь().

° а е а e ° е ° ° ° a e

„„(t) -(t) ° 0,(t) А(t)= llà; jll „= (2) у (t ) — вектор-столбец с з аданными компонентами

Z (t):(У,(t), 20 у2() р ° фур()д р

x(t) — вектор неизвестных

x(t) =(х „(», х,(1),...,xh(t)1 .

Предполагается, что .а; и у;(1) 25 изменяюгся во времени дискретно, через некоторые промежутки времени 41д и 4С р причем Qt г ((41+

Цель изобретения — довышение быстродействия устройства.

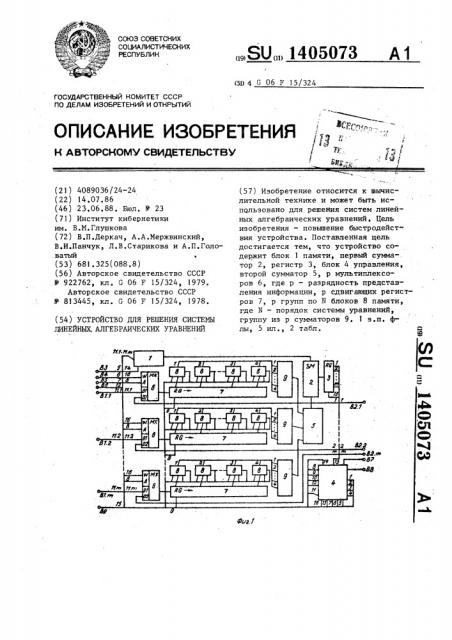

3Р .На фиг, 1 приведена функциональная схема устройства; на фиг. 2 и 3— схема блока управления1 на фиг. 4— состояние сдвигающих регистров в процессе вычисления; на фнг. 5 — алгоритм работы устройства.

Устройство содержит блок 1 памяти, первый сумматор 2, регистр 3, блок 4 управления, второй сумматор 5, р мультиплексоров б, р .сдвигающих ре- 40 гистров 7, р групп по И блоков 8 памяти, группу из р сумматоров 9. Блок, 4 управления содержит первый регистр

10, первый 11 и второй 12 счетчики, второй регистр 13, триггер 14, первый 15 и второй 16 дешифраторы, сумматор 17, третий дешифратор 18, первый 19, второй 20, третий 21, четвер тый 22, пятый 23, шестой 24, седьмой

25, восьмой 2б и девятый 27 элементы

И, первый 28, второй 29, третий 30 и четвертый 31 элементы НЕ, элемент 32 задержки, группа из И элементов И 33, элемент ЧИ-ИЛИ 34.

Блок 1 памяти имеет разрядность р и емкость И слов, необходимую для

55 хранения заданного массива значений у, Сумматор 2 служит для формирования результата вычислений неизвестных х, (Ю

-х -у, 1 1 где ь (3) порядковый номер компоненты вектора х (он же порядковый номер уравнения в системе); индекс суммирования; число уравнений в системе, совпадающее с. размерностью вектора х. как разности между значением у и суммами слагаемых выражений.

Регистр 3 представляет р-разрядный регистр для хранения текущего результата вычислений х,.

Сумматор 5 суммирует числа, представляющие суммы коэффициентов, вычисленные в каждом канале обработки информации.

Регистр 7 предназначен для хранения и сдвига вычисляемых и вычисленных ранее компонент вектора и имеет количество разрядов, не меньшее числа коэффициентов а;

Блоки 8 памяти предназначены для хранения сумм слагаемых. Его разрядность определяется требуемой точностью вычислений и может быть различной в зависимости от границ области значений коэффициентов а; .. Адрес ячейки, к которой происходит обращение, определяется кодом, находящимся в соответствующих триггерах регистра 7.

Сумматор 9 предназначен для суммирования чисел, считываемых с блоков 8 памяти суммы коэффициентов.

Регистр 10 хранит код выполняемой микрооперации. Счетчик 11 формирует . код адреса того блока, в который осуществляется запись сумм коэффициентов. Регистр 13 хранит код требуемого числа циклов вычислений. Триггер

14 формирует признак занятости устройства. Дешифратор 15 формирует сигнал выполняемой микрооперации. Де1 шифратор 16 формирует сигнал амбара: блоков 8 памяти при вводе суммы ко фидиентон. Суааяатор 17 определяет количество невыполненных циклов итераций. Дешифратор 18 формирует признак равенства кодов, хранящихся в счетчике циклов и регистре циклов.

Решение системы уравнений (1) основано на итерационном методе Гаусса-Зейделя

1-1 и (17+11 (ql 7 Г с — Иай ,„. " — „

1405073

С учетом характера матрицы (2) процесс (3) можно представить в виде

1-1 )) а ), 1j j .. 1j х =х

1 1 х -у ) (1))

1 или (4) 10 и 1-1. (4+1) (1)) ) У ), r (1)+1) х, =х; + — - — -- а. х. + и

+ E. а;;х("1, 1а1 (5) 15 х (=1,:N) в двоичном коде имеет вид в

Ф-) 1 х =. х 2, (б) 20 где р — разрядность двоичных чисел; х; — значение разрядов в двоич1б ном представлении.

Обозначив а х ") и)

=q ао (7) 30 имеют х =х(+ " -, 2 (. ц

Я ) к

-4+1 Л

)),М х(1") =1 — - 2 .Е. Я +х )), ао )=0 (9) Слагаемые каждой из двух еумм, находящихся в (8), могут быть сгруппированы по Д членов (значение Ы определяется количеством адресных входов 40 в блоках памяти). Общее число таких групп равно Nl/2, где N. число коэффициентов а (Я 4 2N-1). С учетом того, что переменные с)) принимают значение 0 при х =0 и .а; /а1 при 45 х =1 может быть вычислена сумма ..) слагаемых для любого из 2 возможных кодов в группе. Вычисления всех 2 сумм в каждой группе производится вне устройства (например, на универ- сальной 3BM), а результаты вычислений для всех возможных кодов вводить в блоки 8 памяти сумм коэффициентов.

В этом случае х; можно вычислить как где зо( )е. (10)

j (-)) 11

Вычисление х; по формуле (9) реализуется путем считывания кодов Q, из соответствующих ячеек блоков 8 памяти, определяемых кодом текущего при" ближения в сдвигающих регистрах 7, формирования с помощью сумматора 9 сумм Ц5 в каждом разряде, суммирования в сумматорах 5 значений, полученных в сумматорах 9, считывания вели чин ó; /а, и х 1) с соответствующих блоков памяти и формирования результатов вычисления с помощью сумматора 2, В результате выполнения требуемого количества тактов вычислений, определяемого числом разрядов в регистр

7, в последних записаны результаты вычислений неизвестных х» на ()+1)-й. итерации. После выполнения необходи-:. мого числа итераций, определяемого загруженными в блок 4 управления дан-ными, в регистрах 7 сформирован рее;:" зультат решения системы уравнений, Таким образом, в устройстве вычисления неизвестных могут быть выполнены в одном такте с помощью та- ких действий, как загрузка, сдвиг выборка по адресу и суммирование, Реализация конкретного алгоритма вычислений основана. на выполнении определенных операций, представленных в табл. 1, и анализе формируемых в устройстве логических условий, приведенных в табл, 2.

Таблица 1

Ход операции

Операции, Мнемоническое обозначе ние операции

000

СБР

Сброс

НОП

ВКВ

Ожидание 001

Ввод признака окончания вычислений 010

Ввод начального при-" ближения 100

ВНП

Запись коэффициентов 101

ЗКФ

405073 6

"Ввод начального приближения" . В результате н регистры 7 записывается информация об адресах ячеек блоков 8

5 памяти суммы коэффициентов. При поступлении на входы ВЗ, В4 и В5 кода

101 (код операции "Запись коэффициентов") и на вход В9 импульса занесения код операции записывается в устройство (блок 4) и производится дешифрация кода операции 101. Соответственно выбирается в каждом канале только один блок 8 памяти суммы коэффициентов. При поступлении на вход Вб импульса тактовой частоты информация о записываемой сумме коэффициентов с входов Bl.l-В.1.m заносится в один из выбранных блоков 8 памяти суммы коэффициентов. После

20 записи информации в выбранную ячеику блоком 4 управления активизируется другая цепь и информация с входов

Bl.l-Bl.m записывается по тому же адресу, определяемому соответствующим

25 кодом регистра 7, но в другой блок 8 памяти суммы коэффициентов. Для за.писи суммы коэффициентов в другую ячейку снова выполняется операция

"Ввод начального приближения", в ре30 зультате которой в регистрах 7 записан адрес новой ячейки.

"Ввод правой части", Операция состоит в записи данных в блок 1 памяти, которые поступают на его первый вход. Для этого блок 4 управления формирует стробирующие импульсы, поступающие на вход чтения блока 1 памяти, 1

"Счет". Выполнению операции обыч40 но предшествует выполнение операций

"Запись коэффициентов", "Зались начального приближения" и "Ввод правой части". При поступлении кода опера" ции "Счет" на соответствующем выходе

45 блока 4 управления формируется импульс, по которому результат, сформированный на выходе сумматора 2, записывается в регистр 3. На выходе сумматора 2 при этом формируется раз50 ность значения правой части, поступающей с блока 1 памяти, и значения, сформированного сумматором 5. Результат на выходе равен сумме слагаемых, считываемых с сумматора 9, ко5

Продолжейие табл, ) (СЧ

Счет Таблица2

Мнемоничес кое обозна

Логическое условие чение

СЧИ-Мl Код счетчика индекса больше или равен Ml

СЧИ-0

Код счетчика адреса блоков

8 памяти суммы коэффициентов равен М3

СЧц-Р 15

ВПЧ, Ввод правой части 110

СЧИ-М2 . Код счетчика индекса равен М2

Код счетчика индекса равен 0

Выполненное число циклов вычислений равно числу, записанному в регистре

Р13

П р и м е ч а н и е. Nl — число коэффициентов а; 1, М2 — число разря-дов в регистрах 7, МЗ вЂ” число блоков

8 памяти суммы коэффициентов, P15— число итерационных циклов, заданное загружаемыми в регистр 13 данными, На архитектурном уровне содержание операций состоит в следующем.

"Ожидание", Никакие операции не выполняются, "Сброс". Блок 4 управления устанавливается в исходное положение, "Ввод начального приближения", Операция заключается в записи в регистры 7 данных, подаваемых на входы устройства Bl 1-Вl,m. Ввод признака окончания вычислений". Операция состоит во вводе данных с входов Bl.l-Bl m в блок 4 управления (количество итераций вычислений).

"Запись коэффициентов", Осуществляется после операций Сброс" и торые суммируют числа, поступающие ° с выходов блоков 8 памяти сумм коэффициентов и определяемые кодом, находящимся в соответствующих регистрах 7.

1405

Далее информация в регистре 7 сдвигается на один разряд„ а в первый триггер регистра 7 записывается результат, хранящийся в соответствующем триггере регистра 3.

В каждый последующий такт выпол1 няются аналогичные операции, в первые разряды регистра 7 записываются новые вычисленные значения х1. После 10 выполнения М1 сдвигов блок 4 управления формирует сигнал блокировки записи информации в регистры 7, в результате чего в регистр 7 записывают" ся О. Если выполняемый итерационный 15 цикл последний, блок 4 управления на выводе В7 формирует признак последнего цикла. В конце последнего цикла триггер "Работа" переводится в нулевое состояние. 20

Работа блока 4 управления определяется содержанием операций, приведенных в табл. 1. Выполнение каждой операции начинается после появления на выходе В9 сигнала "Занесение", в результате которого информацйя с входов Bl I-Вl.m оказывается занесенной в регистр 10 (фиг. 2). При записи в регистр 10 кодов операции, которые выполняются более чем за один 30 такт (коды 100-111), триггер 14 "Работа" устанавливается в "1" с помощью элемента И 27. Далее выполнение операций происходит следующим образом.

"Сброс". Осуществляется сброс счетчика 11 кодом адреса блока 8 памяти счетчика 12 и триггера 14.

"Ожидание". Импульсы тактовой частоты на выходах элементов 26, 23 и 40

32 не формируются, так как блокируются сигналами с выходов элемента 19 и дешифратора 15.

"Ввод начального приближения"„

При этой микрооперации сигнал с со- 45 ответствующего выхода дешифратора 15 подается на управляющие входы мультиплексоров 6, а сигналы тактовой частоты с выхода элемента 26 подаются на вход регистров 7.

"Запись коэффициентов", На выхо- де элемента 29 формируется сигнал, который подается на блоки 8 памяти в качестве признака записи. Запись осуществляется в блок 8, адрес которого определяется кодом в счетчике 11, "Ввод правой части". Сигнал с выхода дешифратора 15 через элемент

073 8

HE 29 поступает на вход элемента И

23,.на выходе которого формируется сигнал записи правой части в блок 1 памяти.

11

Ввод признака окончания вычислений".Информация с входов BI I-Bl m записывается в регистр 13.

"Счет". В каждый период тактовой частоты на выходе элемента 32 задерж" ки формируется импульс, задержанный на время установления сигналов на сумматорах 5 и 9. При записи в ре гистр 10 кода операции 111 все блоки

8 памяти суммы коэффициентов оказываются выбранными, В каждый период тактовой частоты формируются также сигналы на выходе элемента 26, обеспечивающие запись информации из регистра 3 в регистры 7 и увеличивающие мод счетчика I 2 на единицу, При формировании в счетчике кода

Ml элемент И 22 формирует сигнал бло-, кировки записи информации в регистре

7. При поступлении последуюпих тактовых импульсов в регистрах 7 записываются нули. При равенстве значений кодов счетчика циклов и регистра )3 на выходе сумматора 17 формируется код, равный О, При этом на нулевом выходе дешифратора 18 формируется признак последнего цикла.

В нулевом такте регистра 7 находятся начальное приближение и вычис ляется первое итерационное приближение х,. В первом такте начальное ( приближение сдвигается на один разряд вправо и в первый разряд регистра 7 записывается на один разряд вправо, и в первый разряд регистра 7 записы- вается вычисленное значение х,. В и-м такте в первый разряд ааписывается вычисленное значение х „. Итерационный цикл завершается после 2N сдви;. гов, в результате которых данные вы- числений занимают исходное положение для выполнения следующей итерации.

Состояние устройства в процессе вычислений может характеризоваться кодами, хранящимися. в триггере "Работа", в счетчике выбранных блокОв памяти суммы коэффициентов, в тригге-, рах регистров 7, соответствующих раз-, рядам адреса ячейки памяти суммы коэффициентов при выполнении микрооперации "Ввод коэффициентов" °

Загрузка кодов сумм коэффициентов в блоки 8 памяти и решение системы уравнений иллюстрируется блок-схемой

1405073

10 обозначены следующие действия и логические условия: 35 — "Сброс", в ре- < зультате которого блок 4 управления устанавливается в исходное положение;

36 - "Ввод начального приближения", в результате чего в регистры 7 записываются адреса ячеек блоков 8 памя- 10 ти.суммы коэффициентов (в последующем в эти ячейки записываются коды сумм коэффициентов); 37 — анализ логического условия, "Код счетчика индекса равен N2"; 38 — "Запись коэффици- 15 ентов", код с входных шин В1,1-В1.m записывается в адресуемую регистром

7 ячейку, выбранную дешифратором 1б кода счетчика 11 адреса блоков 8 памяти суммы коэффициентов; 39 — ана-, 20

1. Устройство для решения системы линейных алгебраических уравнений, содержащее блок памяти, первый сумматор, регистр, блок управления, причем первый, второй и третий входы кода операций и вход синхронизации устройства подключены соответственно к первому, второму, третьему входам режима и входу синхронизации блока управления, вход признака занесения б кода операции устройства подключен к четвертому входу режима блока уп.равления, с первого по р-.й входы свободнь1х членов устройства, где рразрядность представления информации, 0. подключены соответственно к первому по р-й иьформационным входам блока памяти, выход которого подключен к первому информационному входу первого сумматора, выход которого подключен к информационному входу регистра, вход записи которого подключен к первому выходу блока управления, с первого по р-й выходы регистра подключены соответственно к первому по р-й

0 информационным выходам устройства, о т л и ч а ю щ е е с я тем, что,с целью повышения быстродействия устройства,в него введено р мультиплексоров, р сдвигающих регистров, группа из р сумматоров, второй сумматор и р групп по Б блоков памяти, где

И вЂ” порядок системы уравнений, при этом входы с первого по р-й свободных членов устройства подключены соответственно к первым информационным входам с первого по р-й мультиплексоров, с первого по р-й выходы регистра подключены соответственно к вторым информационным входам с пер55 вого по р-й мультиплексоров, выходы которых подключены соответственно к информационным входам с первого по р-й сдвигающих регистров, второй выход блока управления подключен к пер

50 алгоритма работы устройства (фиг.5).

Цифрами и соответствующей мнемоникой лиз условия "Код счетчика адреса бло ков памяти 8 суммы коэффициентов равен МЗ"; 40 — анализ условия "Код адреса выбранной ячейки равен N4", где

М4. — максимальное значение адреса ячейки в блоке 8 памяти суммы коэффициентов"; 41 — "Ввод признака окончания вычисления", при котором код требуемого количества итераций запи ывается в соответствуюпр и регистр блока 4 управления; 42 — "Ввод начального приближения", данные начального приближения с входных шин устройства записываются в регистры 7;

43 — анализ логического условия "Код счетчика индексов равен N2"; 44— производится "Ввод правой части" (вектор вводится в блок 1 памяти)," 45 — анализ логического условия "Код, счетчика индексов равен N2" 4б—

"Счет", за один такт осуществляется вычисление одного значения х,. сдвиг содержимого регистров 7 на один разряд и запись вычисленного значения в освободившийся разряд, 47 — анализ логического условия "Код счетчика индексов больше или равен Nl" 48— формирование признака блокировки мультиплексора, равного 1; 49 — анализ условия "Код счетчика индекса равен M2"; 50 — формирование признака блокировки мультиплексора, равного 0; 51 — анализ логического условия "Выполненное число итерационных циклов вычислений равно числу, записанному в Р15"; 52 — формирование сигнала "Признак последнего цикла равен 1"; 53 — анализ логического условия "Код счетчика индексов равен

0"; 54 — формирование сигнала "Признак последнего цикла равен 0".

При необходимости решения системы (1) для следующего момента времени указанный процесс повторяется. В случае, когда изменяется только правая часть у, а значения а; остаются прежними, необходимость в процедурах вычисления и загрузки коэффициентов отпадает.

Формула изобретения

1405073

12 вым управляющим входам с первого по р-й муль типлек сор ов, третий выход блока управления подключен к вторым управляющим входам с первого по р-й

5 мультиплексоров, четвертый выход блока управления подключен к входу чтения блока памяти, пятый выход блока управления подключен к входам сдвига с первого по р-й сдвигающих регист- 10 ров, шестой выход блока управления подключен к входам чтения (записи) с первого по N-й блоков памяти с первой по р групп, с первого по р-й входы режима группы блока управления 15 подключены соответственно к входам с первого по р-й свободных членов устройства, седьмой и восьмой выходы блока управления подключены соответственно к выходу признака занятости 20 устройства и выходу признака последнего цикла устройства, а-й выход, где a=1,...,N, Ъ-го сдвигающего регистра, где Ъ= 1,...,р, подключен к адресному входу а-го блока памяти 25 b-й группы, выход которого подключен к а-му информационному входу b-го сумматора группы, выход которого подключен к b-му информационному входу второго сумматора, выход которого подключен к второму информационному входу. первого сумматора, а-й выход группы блока управления подключен к синхровходам а-х блоков памяти с ПерВои по р ю группe

2, Устройство по п. l, о т л ич а ю щ е е с я тем, что блок управления содержит два регистра, три дешифратора, два счетчика, сумматор, триггер, девять элементов И, четыре 40 элемента НЕ, элемент задержки, элемент 4И-ИЛИ и группу из N элементов

И, причем первый, второй и третий входы режима блока управления подключены соответственно к информацион- 45 ным входам с первого по третий первого регистра, четвертый вход режима блока управления подключен к синхровходу первого регистра, выход которого подключен к входу первого дешиф- 50 ратора, первый выход которого подключен к первому входу первого элемента И и первому входу второго элемента И, второй выход первого дешифратора подключен к второму входу первого элемента И, третий выход первого дешифратора подключен к входу записи считывания второго регистра,к третьему входу первого элемента И, четвертыи выход первого дешифратора подключен к первому входу третьего элемента И, пятый выход первого дешифратора подключен к входу первого элемента НЕ, третьему выходу блока управления и первому входу четвертого элемента И, шестой выход первого дешифратора подключен к входу второго элемента НЕ, седьмой выход первого дешифратора подключен к входу третьего элемента НЕ, к первому входу пятого элемента И, восьмой выход первого дешифратора подключен к первому входу шестого элемента И, первому входу седьмого элемента И, второму входу третьего элемента И и первым входам элементов И группы, вход синхронизации блока управления подключен к второму входу шестого элемента И, первому входу восьмого элемента И, второму входу пятого элемента

И, синхровходу второго дешифратора, второму входу седьмого элемента И, входу синхронизации второго регистра и второму входу второго элемента И, выход которого подключен к входам установки в "0 первого и второго счетчиков, выходы с первого по (N-1)-й второго дешифратора подключены к вторым входам соответственно элементов И с первого.по (N-l)-й группы, N-й выход второго дешифратора подключен к второму входу М-го элемента И группы и третьему входу третьего элемента И, выход которого подключен к первому входу элемента 4И-ИЛИ, инверсный выход которого подключен к входу четвертого элемента

НЕ, выход которого подключен к входу . установки в "0" триггера, выход кото.— рого подключен к седьмому выходу блока управления, выход первого элемента

И подключен к второму входу восьмого элемента И, инверсный выход которого подключен к входу элемента задержки, пятому выходу блока управления и счетному входу второго счетчика, выход элемента задержки подключен к первому выходу блока управления и пер" вому входу девятого элемента И, инверсный выход которого подключен к информационному входу триггера, выход четвертого элемента И подключен к второму выходу блока управления, инверсный выход пятого элемента И подключен к четвертому выходу блока управления и второму входу девятого элемента И, выход седьмого элемента И!

405073 подключен к счетному входу первого ( счетчика, выход которого подключен к информационному входу второго дешифратора„ выход первого элемента НЕ подключен к второму входу элемента

4И-ИЛИ, выход второго элемента НЕ подключен к шестому выходу блока управления, выход третьего элемента НЕ подключен к третьему входу элемента 10

4И-ИЛИ, выход шестого элемента И подключен к четвертому входу элемента

4И-ИЛИ, выходы элементов И с первого по N-й группы подключены соответственно к выходам с первого по Б-й 15 группы блока управления, входы режима с первого по р-й группы которого подключены к информационным входам соответственно с первого по р-й второго регистра, выход которого подклн— чен к первому информационному входу сумматора, выход которого подключен к входу третьего дешифратора, выход которого подключен к восьмому выходу блока управления и пятому входу элемента 4И-ИЛИ, первый и второй выходы второго счетчика подключены соответственно к второму входу четвертого элемента И и второму информационному входу сумматора, третий выход второго счетчика подключен к шестому, седьмому, восьмому и девятому входам элемента 4И-ИЛИ.

4 4 4

О х, ° ° в х, x, Xn-t

Х2

Х1

° 4 4

4 ° ° х, 1405073 хл о

4 4 4

Х

Хя х„

Ху

Х . 3

1405073

Составитель В, Смирнов

Редактор Н.Бобкова Техред И.Дидык

Корректор М Пилипенко

Заказ 3107/54 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул, Проектная, 4