Способ записи и считывания информации в мноп-элементе памяти и матричный накопитель для запоминающего устройства

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для создания как электрически программируемых постоянных запоминающих устройств, так и многократно перепрограммируемых запоминающих устройств повып еннай информационной емкости на основе МДП- структур, в частности МНОП-транзисторов. Целью изобретения является повьииение информационной емкости. Основой теля является МНОП-транзистор. Запись информации осуществляют подачей программирующих импульсов на каждую стокистоковую область, кроме одной, на которую подают при считывании импульс напряжения . Затворы МНОП-транзисторов любой нары смежных столбцов матрицы соединены с двумя адресными щинами таким образом, что к одной из них подключены затворы транзисторов только четных строк матрицы, а к другой - только нечетных. 2 с. п. ф-.1ы, 4 ил. eg

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (Я? 4 О 11 С l I 40 ".?«:

ОПИСАНИЕ ИЗОБРЕТЕНИЯ/ :

К АBTOPCHOMY СВИДЕТЕЛЬСТВУ

4й

CD

С

CD

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21 ) 3583900/24-24; 3578993/24-24 (22 ) 16.04. 83 (46) 23.06.88. Бюл. ¹ 23 (72) Ю. В. Голтвянский, А. II. Ду бчак, В. Д. Костюк и А, П. Нагни (53) 681.327.66 (088.8) (56) Гlатент США № 3846768, кл, G 11 С 11/40, опублик. 1974.

Патент ФРГ № 2657643, кл. H 01 L 29/76, опублик. 1977. (54) СПОСОБ ЗАГIИСИ И СЧИТЫВАНИЯ

ИНФОРМАЦИИ В МНОП-ЭЛЕМЕНТЕ

ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ

ДЛЯ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА (57) Изобретение относится к вычислительной технике и может быть использовано для создания как электрически программируемых постоянных запоминающих устройств, „„SU„„1405089 A 1 так и многократно перепрограммируемых запоминающих устройств повышенной информационной емкости на основе МДГIстру ктур, в частности МНОГl-транзисторов.

Целью изобретения является повышение информационной емкости. Основой накопителя является МНОП-транзистор. Запись информации осуществляют подачей программирующих импульсов на каждую стокистоковую область, кроме одной, на которую полают при считывании импульс напряжения. Затворы МНОП-транзисторов любой пары смежных столбцов матрицы соединены с двумя адресными шинами таким образом, что к одной из них подключены затворы транзисторов только четных строк матрицы, а к другой — только нечетных. 2 с. и. ф-лы, 4 ил.

1405089

Изобретение относится к вычислительной ( ехнике и может быть использовано для оздания как электрически программируе. ых постоянных запоминающих устройств, ак и многократно программируемых запоминающих устройств повышенной информационной емкости на основе СДП-структур, частности МНОП-транзисторов.

Целью изобретения является повышение йнформационной емкости.

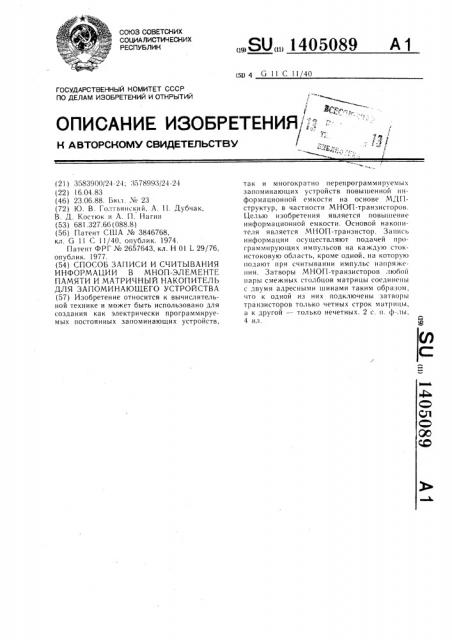

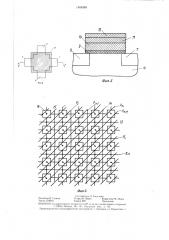

На фиг. 1 представлены эксперименталь ые выходные характеристики 1 — 3, разъяс яюц ие принцип считывания информации, оторая запиcûâàåòñÿ как со стока, так и о стороны истока обычного МНОП-транистора с двумя сток-истоковыми областями; а фиг. 2 — структура элемента памяти, ид сверху", на фиг. 3 — то же, вид сбоку; а фиг. 4 — — матричный накопитель на ос> ове МНОП-элемента памяти с четырьмя

C O K - H C TO K O B bl ill H О 6,1 3 C T 8 i%1 H .

При записи информации используют канальную или лавинную инжекцию носителей с захватом заряда в диэлектрике вблизи с окового р — n-перехода, но операцию прог аммирования производят столько раз, с олько QH имеет сток-истоковых областей.

Г ри этом с помощью инжскции «горячих» э11сктронов, например, в и-канальном МНОГI элементе форм и руют требуемую величину и рогового напряжения вблизи каждого с ок- исто ковогo р — n-перехода, подавая tloл жительное напряжение на его затвор и к нкретную сток-истоковую область, заземл в хотя бы одну из оставшихся при считыв нии информации, записанной вблизи выб анного сток-истокового р — n-перехода, н затвор МНОГI-элемента подают напряжен е величины, находящейся внутри его межи роговой зоны, а все остальные или хотя бы о, ин из невыбранных сток-истоковых р— и — р-переходов возбуждают напряжением п евышающим напряжение смыкания части

МНОП-элемента вблизи этого р — n-переход3 с учетом того, что эта часть может находиться в состоянии с высоким пороговым н4пряжением благодаря ранее накопленному заряду в диэлектрике вблизи данного р- и-перехода в предшествующей операции п) ограм мирования.

Напряжение смыкания части МНОПэх(емента вблизи сток-истокового р — и-перехода, находящейся в состоянии с высоким

HOpoI oBblM напряжением при определенных режимах записи, может превышать величину

5 В, выбранную, например, в качестве напряжения питания интегральной схемы при сч итывании. В конкретной реализации интетральной схемы по какой-либо причине пГ(и считывании может оказаться невыгодным формирование на стоке элемента импульса с амплитудой более 5 В. В этом случа е при программировании формируют требуемую величину порогового напряжения пс следовате1ьно вблизи каждого сток-исто10

55 кового р — n:ïåðåõîäà, за искл ючением по крайней мере одного, который при записи используется как исток, а при последующем считывании — как сток. В этом случае при считывании не требуется повышенное напряжение на стоке, но имеет место потеря по крайней мере одного бита информации на элемент.

Элемент памяти, реализующий предлагаемый способ, выполнен с четырьмя стокистоковыми областями и содержит подложку 4 р-типа, и-сток-истоковые области 5 — 8, первый — третий 9 — 11 слои подзатворного диэлектрика, управляющий электрод (затвор) 12.

При записи «горячих» электронов на сток 5, соединенный с затвором 12, подается импульс (l длительностью 10 с, исток 7 при этом заземлен. Принцип «разогрева» и инжекции электронов здесь аналогичен тому, который используется в приборах с плавающим затвором, с той лишь разницей что в данном случае захваченные электроны не растекаются вдоль канала, а сосредотачиваются на ловушках в нитриде кремния вблизи стока.

В зависимости от режима записи длина области вдоль канала со встроенными в диэлектрик зарядом колеблется вблизи значения мкм. При измерении эффективного порогового напряжения такого транзистора с записанным зарядом сток инвертируется с истоком, т. е. подается напряжение U =

=U»=Uiiop до появления тока в канале величиной 1 мкЛ.

Экспериментальные зависимости (фиг. 1) разъясняют принцип считывания информации, если ее записывать как со стороны стока, так и со стороны истока. Пусть к затвору элемента приложено некоторое напряжение (/»=+5 В, находящееся внутри межпороговой зоны МНОП-элемента (Uiiop=2 В, Uiiop=

=9 В). Если элемент находится в исходном состоянии, то его выходная характеристика имеет вид 1 независимо от того, какой электрод является стоком, т. е. ток в канале идет при любом напряжении на стоке (/ . Если произведена запись со стороны стока, то эта характеристика примет вид 2. При этом напряжение Ul соответствует напряжению смыкания части элемента вблизи стока с высоким пороговым напряжением, поскольку длина этой части весьма мала. Если запись произведена со стороны истока или с обеих сторон, то выходная характеристика 3 определяется или напряжением смыкания стокистокового элемента, или пробивным напряжением а -области стока U2 (в зависимости

+ от того, что меньше).

Таким образом, имеется межпороговая зона второго ряда U2+Uli наличие которой позволяет прочесть информацию, которая хранится у стока, а также информацию, которая записана у истока. Для этого при счи1405089

Фор,иуда изобретения см, икА

50

10

20 ус бв

Фиг.7 тывании подают поочередно на стоковую и истоковую области напряжение U, удовлетворяющее соотношению Ul(V(Uz, и по наличию или отсутствию тока определяют, какая информация хранится у противоположного электрода. При этом подается напряжение на затвор, удовлетворяющее соотношению Ю Р((/з(И.р. Таким образом, согласно предлагаемому способу управления

МНОП-элементом памяти с двумя сток-истоковыми областями его информационная емкость повышается в два раза.

Матричный накопитель на основе МНОПэлемента памяти с четырьмя сток-истоковыми областями (фиг. 4) содержит строчные разрядные шины 13, адресные шины 14, столбцовые разрядные шины 15, элемент 16 памяти.

П роти вон олож н ые сток-и сто ко вые обл асти элементов памяти каждой строки матрипы подключены к двум различным строчным разрядным шинам. Противоположные сток- 20 истоковые области элементов каждого столбца матрицы подключены к двум столбцовым разрядным шинам. а затворы элементов памяти соединены с адресными шинами таким образом, чтобы затворы двух произвольно взятых элементов памяти любого одного столбца или любой одной строки матрицы не были подключены к одной и той же адресной шине. Матричный накопитель предназначен для ППЗУ с электрическим стиранием. 30

Выполнение функций данным накопителем непосредственно вытекает из способа записи и считывания в элемент памяти. Предлагаемый накопитель обладает повышенной информационной емкостью.

l. Способ записи и считывания информации в МНОП-элементе памяти, заключающийся в подаче программирующих импульсов на стоковую и затворную области МНОПэлемента памяти при записи информации, а при считывании — в подаче импульса напряжения на затворную область, отличающийся тем, что, с целью повышения информационной емкости элемента памяти, при записи информации подают программирующие импульсы на каждую сток-истоковую область, кроме одной, на которую при считывании подают импульс напряжения.

2. Матричный накопитель для запоминающего устройства, содержащий элементы памяти, включенные в перекрестиях адресных и разрядных шин, отличающийся тем, что, с целью повышения информационной емкости накопителя, элементы памяти выполнены в виде МНОП-элемента с четырьмя сток-истоковыми областями, при этом llpoтивоположные сток-истоковые области элементов памяти каждой строки подключены соответственно к двум смежным строчным разрядным шинам, а противоположные стокистоковые области элементов памяти каждого столбца подключены соответственно к двум смежным столбцовым разрядным шинам, при этом затворы каждого из элементов памяти i-й строки и j-го столбца (гдеi и у —— текущие значения номера строки и столбца) соединены соответственно с затворами элементов памяти (/+2) -строки, (-2) -строки и (j+2) -столбца, (j — 2) -столбца и соответствующей адресной шиной.

1405089

Фиа 2

Составитель Л. Амусьева

Редактор Н. Гунько Текред И. Верес Корректор М. Г1ожо

Заказ 3108/55 Тираж 590 Подписное

ВНИИГ1И Государственного комитета C(:СР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раугиская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4