Способ интегрирующего аналого-цифрового преобразования

Иллюстрации

Показать всеРеферат

Изобретение относится к электроизмерительной технике и предназначено для создания высокоточных аналого-цифровых преобразователей постоянного напряжения. Целью изобретения является повышение точности и обеспечение преобразования сигнала произвольной полярности. Введение в известньй способ операций интегрирования опорного напряжения до момента равенства интегрального значения заданному пороговому уровню и интегрирования напряжения смещения в зависимости от размера входного сигнала-позволяет значительно повысить точность и обеспечить i.. преобразование сигнала произвольной полярности. 4 ил. Ш (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

„„80„„ 140511

А1 ду 4 Н 03 М 1/52

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ @ ñ

/ !1 Р,!

ОПИСАНИЕ ИЗОБРЕТЕНИЯ /,",, g

К А BTOPCKOMY СВИДЕТЕЛЬСТВУ (21) 4077242/24-24 (22) 13.06.86 (46) 23.03.88. Бюл. № 23 (71) Пензенский политехнический институт и Специальное конструкторское бюро вычислительной техники Института кибернетики АН ЭССР (72) Э.К.Шахов, О.А.Голышевский, В.А.Юрманов, В.Д.Михотин, Ю.П.Замараев и М.А.Пильв (53) В81.325(088.8) (56) Авторское свидетельство СССР № ?41459, кл. Н 03 M 1/50, 1978.

Авторское свидетельство СССР

¹ 1358095, кл. Н 03 M 1/52, 1985. (54) СПОСОБ ИНТЕГРИРУЮЩЕГО АНАЛОГОЦИФРОВОГО ПРЕОБРАЗОВАНИЯ (57) Изобретение относится к электроизмерительной технике и предназначено для создания высокоточных аналого-цифровых преобразователей постоянного напряжения, Целью изобретения является повышение точности и обеспечение преобразования сигнала произвольной полярности. Введение в известный способ операций интегрирования опорного напряжения до момента равенства интегрального значения заданному пороговому уровню и интегрирования напряжения смещения в зависимости от размера входного сигнала позволяет значитель-! но повысить точность и обеспечить преобразование сигнала произвольной полярности, 4 ил.

1405116

Изобретение Относитая к электроиэмерительной технике и предназначено для создания прецизионных аналогоцифровых преобразователей.

Цель изобретения — повышение точности преобразования.

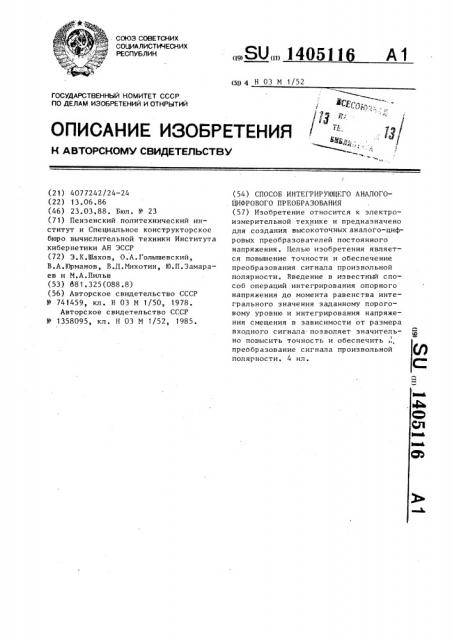

На фиг.1а показано преобразование входного сигнала положительной полярности при наличии напряжения смеще- 10 ния е, б — воэможность преобразования входного сигнала U произвольной полярности (е = О); на фиг.2 — один из возможных вариантов аппаратной реализации предлагаемого способа, на фиг.3-15 один из возможных вариантов аппаратной реализации устройства управления и преобразователя время — код (ПВК), на фиг ° 4 — временные диаграммы работы устройства управления и ПВК. 20

Сущность способа заключается в следующем.

Процесс преобразования осуществляется в два цикла Т, и Т . В первом цикле в течение образцового интервала 25 времени Т интегрируют входной сигнал

U вместе с напряжением смещения е, затем интегрируют опорное напряжение вместе с напряжением смещения до момента достижения накопленным интегралом значения меньшего заданного порогового уровня U . Для этого треп, буется интервал времени Т,, который пропорционален величине входного напряжения U„. Далее интегрируют только 35 напряжение смещения е до момента времени, отстоящего от начала интегрирования опорного напряжения U на заданный интервал времени Т. -t,, который для упрощения в дальнейшем бу- 40 дем обозначать через Т, (фиг.1а), является частным случаем. В общем случае Образцовый интервал времени

Т может выбираться из условия обесо печения заданного подавления помехи, 45

a (t -C, ) = (t,-t ) — из условия обеспечения требуемой разрешающей способности. После этого опять интегрируют опорное напряжение U, вместе с напряжением смещения е до момента достижения накопленным интегралом значения второго порогового уровня

U того же знака, для чего требуетП2 ся интервал времени ь Т, который при условии постОянства ОпОрного нап- 55 ряжения U и напряжения смещения е является величиной постоянной.

Во втором цикле Т в течение заданного интервала времени Т интегри- руют только напряжение смещения е. а,затем повторяют последовательность операций, приведенных в первом цикле.

При этом информативными являются интервалы времени Т и Т (см.фиг,1, а).

Результат преобразования Т находят как-разность определенных в ходе интегрирования интервалов времени по формуле Т = (Т + Т ) — (аТ, + z T ), которая представляет собой разность интервалов интегрирования опорного напряжения в первом и во втором циклах.

Способ при реализации обеспечивает малые значения составляющей погрешности преобразования, обусловленной дрейфом нуля интегратора, предполагает минимальное:- исло коммутаций опорного напряжения и отсутствие взвешенного суммирования величин интервалов времени, что по сравнению с известным способом позволяет повысить точность преобразования.

Величины двух пороговых уровней и U д одного знака выбирают, ис I

П ходя из величин опорного напряжения

U,, заданного интервала времени Т и постоянной времени интегрирования

Я. Например, величины пороговых уровней могут быть определены из следующих уравнений:

U,T — U

2 е(Т, — ЬТ, )

Кроме повышения точности преобразования способ обеспечивает также преобразование входного сигнала произвольной полярности при произвольной полярности напряжения смещения Е и при неизменной полярности опорного напряжения Ь . Для этого достаточно (фиг. 1б) обеспечить при U„ 0 длительность ЬТ, и Т, равной Т, /2, что достигается просто соответствующим выбором значения U,. Зто не требует абсолютно никаких дополнительных аппаратурных затрат при реализации и не вызывает дополнительных погрешностей.

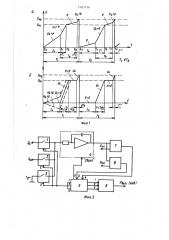

Схема (фиг.2) содержит ключи 1-3, интегратор 4, устройство 5 управления, преобразователь 6 времени в код (ПВК) и устройства 7 и 8 сравнения.

Временные диаграммы, представленные на фиг,1а, полностью отражают процесс изменения напряжения на выхо1405116 де интегратора 4. Соответствующие напряжения подключаются к входу интегратора 4 ключами 1-3, которые управляются сигналами с устройства 5 уп-;

5 равления. Устройства 7 и 8 сравнения определяют достижение интегратором пороговых уровней соответственно U

1 и U выдавая соответствующий сигнал

12 в устройство 5 управления, которое 10 проводит также разряд интегратора 4 после завершения циклов Т, и Т (после достижения интегралом второго порогового уровня U> ) .

ПВК 6 осуществляет операцию преоб- 15 разования в цифровой код информационI fl ного интервала времени Т = Т + Т— — dT, — ДТ, получаемого в процессе преобразования в устройстве 5 управления. 20

Один из возможных вариантов реализации устройства 5 управления и ПВК

6 приведен на фиг.3.

Устройство 5 управления содержит генератор 9 опорной частоты, триггера 10 и 11, которые осуществляют квантование моментов срабатывания устройств сравнения, делитель 12 частоты, дешифраторы 13-15, формирующие длительности циклов преобразования 30 и образцового и заданного интервалов времени, элемент ИЛИ 16, формирователь 17 импульсов, осуществляющий формирование коротких импульсов по переднему и заднему фронтам, импуль- З5 са длительностью То, элемент ИЛИ 18, триггер 19, элемент И 20, делитель 21 частоты формирующий сигнал "Сброс" для преобразователя время — код 6, элемент И 22. 40

ПВК 6 состоит из переключателя 23, выходы которого соединены с входами реверсивного счетчика 24.

Временные диаграммы работы устрой- 45 ства 5 управления приведены на фиг.4 с подробностью, достаточной для однозначного воспроизведения указанного устройства. Единственный узел, нуждающийся в пояснении, формирователь 17 импульсов. Он осуществляет формирование коротких импульсов по переднему и заднему фронтам импульса длительностью Т . Триггера 10 и 11 осуществляNT квантование моментов срабатывания устройств сравнения. Это осуществляется для того, чтобы исключить накопление погрешности квантования при алгебраическом,суммировании интервалов

I Ц,, времени b.Т,, ЬТ, Т и Т в реверсивном счетчике 24.

Фор мула из обретения

Способ интегрирующего аналого-цифрового преобразования, основанный на двух последовательных циклах преобразования, в первом из которых осуществляют интегрирование входного напряжения в течение образцового интервала времени и последующее интегрирование эталонного напряжения до момента достижения значения первого заданного порогового уровня, после чего осуществляют интегрирование нулевого напряжения до заданного момента времени, а во втором цикле интегрируют нулевое напряжение в течение образцового интервала времени и последующее интегрирование эталонного напряжения до момента достижения значения первого заданного порогового уровня, после чего осуществляют интегрирование нулевого напряжения до заданного момента времени, и формирование выходного кода путем заполнения импульсами эталонной частоты разности соответствующих интервалов времени интегрирования эталонного напряжения в первом и втором циклах, о т л и— ч а ю шийся тем, что, .с целью повышения точности преобразования, в каждом цикле преобразования после достижения заданного момента времени ининтегрируют эталонное напряжение до достижения значения второго заданного порогового уровня по абсолютному значению большего значения первого эаданного порогового уровня.

1405116

Une

Ung фиг.1

Фиа 2

1405116

8bix

Х5 йх.

3С6

Й/х

УГ8

Улр. йлЕ пр.

Вью

Оро унт. Ф

Составитель И. Козлов

Техред А. Кравчук

Корректор В.Бутяга

Редактор Н.Гунько

Заказ 3110/56

Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )K-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул . Проектная, 4