Устройство для измерения спада плоской части импульса

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано .при разбраковке изделий электронной техники по величине спада плоской части прямоугольных испытательных импульсов и прИ измерении величины скорости спада выходного напряжения аналоговых запоминающих устройств . Устройство для измерения спада плоской части импульса содержит блоки 1,2 памяти, дифференциальный усилитель 3 и блок 4 синхронизации. В описании изобретения даны две структурные схемы блока 4 синхронизации в зависимости от функциональной предназначенности устройства. Устройство просто по к-онструкции. 2 з.п. ф-лы, 5 ил.

СОЮЗ СОВЕтСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51)4 С 01 R 29/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

6 Аь т

11 р

Жив. f

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

Il0 ДЕЛАМ ИЗОБРЕТЕНИЙ ИОТНРЫТИЙ (21) 4)55065/24-21 .(22) 02.12.86 (46) 30.06.88. Бюл. У 24 .(71) Электротехнический завод им. Х. Пегельмана .(72) В.Н. Михайлов (53) 621.317. 075(088.8) (56) Авторское свидетельство СССР

У 1019367, кл. G 01 R 29/02, 1983.

Авторское свидетельство СССР

У 834612, кл. С 01 R 29/02, 1981. (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СПАДА

ПЛОСКОЙ ЧАСТИ ИМПУЛЬСА (57) Изобретение может быть использовано,при .разбраковке изделий элект„„SU„„1406530 А1 ронной техники по величине спада плоской части прямоугольных испытательных импульсов и при измерении величины скорости спада выходного напряжения аналоговых запоминающих устройств. Устройство для измерения спада плоской части импульса содержит блоки 1,2 памяти, дифференциальный усилитель 3 и блок 4 синхронизации.

В описании изобретения даны две структурные схемы блока 4 синхронизации в зависимости от функциональной предназначенности устройства.

Устройство просто по конструкции.

2 з.п. ф-лы, 5 ил.

1406530

Изобретение относится к злектроиэмерительной технике и может быть использовано при разбраковке изделий электронной техники по величине спада плоской части прямоугольных ис5 пытательных импульсов, а также при измерении величины скорости спада выходного напряжения аналоговых sanoминающих устройств.

Целью изобретения является расширение функциональных воэможностей устройства за счет обеспечения воз" можности измерения величины спада плоской части прямоугольного импульса и скорости спада выходного напряжения аналогового запоминающего устройства, а также упрощение устройг. ства.

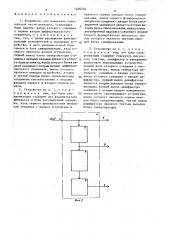

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 — структурная схема блока синхронизации, используемого для измерения величины спада, плоской части импульса; на фиг. 3 — структур-. ная схема блока синхронизации, используемого для измерения скорости спада выходного напряжения АЗУ; на фиг. 4 — диаграммы напряжений, поясняющие работу устройства при измерении величины спада плоской части импульса; на фиг, 5 — диаграммы напряжений, поясняющие работу устройства. при измерении скорости спада выходного .напряжения АЗУ, Устройство содержит (фиг. I) блоки l и 2 памяти, дифференциальный усилитель 3 и блок 4 синхронизации, причем вход блока 4 синхронизации является входом устройства, первый и

40 второй выходы блока 4 соединены соответственно с перцым и вторым входом блока 1 памяти, выход которого соединен с первым входом дифференциального усилителя 3, первый и третий выходы блока 4 синхронизации соединены соответственно с первым и вторым входами . блока 2 памяти, выход которого соединен с вторым входом дифференциального усилителя 3, а его выход является выходом устройства. В качестве блоков

1 и 2 памяти могут быть использованы микросхемы КР1100СКЗ с дополнительными элементами обратной связи и sanoминающими конденсаторами. Дифференциальный усилитель 3 может быть выполнен на операционном усилителе, например. К140УД14, с соответствующими. резисторами обратной связи. Блок 4 синхронизации, используемый для измерения спада плоской части импульса (фиг, 2), содержит формирователи 5 и

6 импульсов и блок 7 регулируемой задержки, причем вход устройства соединен с входом формирователя 5 им-:; пульса и является первым выходом блока 4 синхронизации, выход формирователя 5 является вторым выходом блока

4 синхронизации и соединен с входом блока 7, выход которого соединен с входом формирователя 6 импульса, выход которого является третьим выходом блока синхронизации. формирователи 5 и 6 импульса могут быть построены на базе интегральных таймеров КР1006ВИ1, включенных в режиме одновибратора. Длительность импульсов, формируемых этими таймерами, должна быть больше времени выборки используемых в качестве блоков памяти микросхем КР110ОСКЗ.

Блок 7 регулируемой задержки может содержать формирователь импульсов по фронту входного сигнала на микросхеме К155ЛАЗ и RC-цепочке, выход которого соединен с входом одновибратора на таймере КР1006ВИ1,длительность импульса в котором регулируется переменным резистором, выход одновибратора соединен с входом формирователя импульсов по спаду входного сигнала на микросхеме К155ЛАЗ и RC-цепочке.

Блок 4 синхронизации, используемый для измерения скорости спада выходного напряжения АЗУ (фиг. 3}, содержит генератор 8 импульсов, счетчик 9, дешифратор 10 и измеряемое

АЗУ 11, причем вход устройства соединен с первым входом АЗУ 11, выход которого является первым выходом блока. 4 синхронизации, выход генератора

8 соединен с входом счетчика 9, выход которого соединен с входом дешифрато- . ра, первый выход которого соединен с вторым входом АЗУ 11, а второй и третий выходы являются соответственно вторым и третьим выходами блока 4 синхронизации.

Генератор 8 импульсов может быть выполнен на микросхеме К155ЛАЗ с использованием кварцевого резонатора.

Для счетчика 9 можно использовать микросхему К155ИЕ5. Дешифратор 10 может быть построен на микросхеме

К155ИДЗ с использованием микросхемы

1406530

111 П2

К155ЛН1 для инвертирования выходных сигналов.

Устройство работает следующим образом.

Перед измерением величины спада плоской части прямоугольного импульса с помощью блока, 7 регулируемой задержки устанавливается задержка между импульсами, вырабатываемыми формирователями 5 и 6, равная длительности исследуемого прямоугольного импульса (фиг. 4). На вход устройства подают исследуемый прямоугольный импульс, имеющий начальную амплитуду U>, которая спадает к моменту окончания импульса до величины

U> (фиг. 4а). Исследуемый прямоугольный импульс поступает на информационные входы блоков 1 и 2 памяти. На вход управления блока 1 памяти в момент времени t1 подается импульс выборки, вырабатываемый формирователем

5 импульса (фиг. 4в). После окончания импульса выборки на выходе блока 1 памяти фиксируется напряжение UA (фиг. 4и). Перед окончанием исследуемого импульса на вход управления блока 2 памяти в момент времени t no2 дается импульс выборки, вырабатываемый формирователем 6 импульса (фиг. 4г). В результате на выходе блока 2 памяти фиксируется напряжение U (фиг. 4к). С выходов блоков

1 и 2 напряжения.U и U поступают . на входы дифференциального усилителя 3 и на его выходе устанавливается напряжение 4U о (фиг. 4л), равное разности напряжений Б и 11р 10с 04 UB °

Таким образом, на выходе устройства после окончания исследуемого импульса устанавливается напряжение

4Uc, равное величине спада плоской части прямоугольного импульса.

При измерении скорости спада выходного напряжения АЗУ используется блок 4 синхронизации, представленный на фиг. 3. На информационный вход измеряемого АЗУ 11 подается постоянное напряжение Uo (фиг. 5а). Генератор 8 импульсов вырабатывает тактовые им- пульсы, которые преобразуются с помощью счетчика 9 и дешифратора 10 в импульсы выборки для блока 1 памяти (фиг. 5в), блока 2 памяти (фиг. 5г) и для измеряемого АЗУ 11 (фиг. 5д).

В момент времени t на:вход управления измеряемого АЗУ 11 подается импульс выборки (фиг. 5д), на выходе измеряемого АЗУ ll устанавливается напряжение (фиг. 5б) 11 Пь+ Псм1 где U - напряжение смещения измеряемого АЗУ 11, В момент времени импульс выборки измеряемым АЗУ ll прекращается и напряжение на его выходе начинает уменьшаться вследствие тока утечки ключа до прихода следующего импульса выборки. Следующий импульс выборки измеряемым АЗУ 11 подают в момент времени t, к этому моменту времени напряжение на выходе измеряемого АЗУ 11 приобретает значение U . Таким образом, для определения скорости спада выходного напряжения, измеряемого АЗУ 11, требуется определить разность напряжений за фиксированный интервал времени

T=t>-, который выбирается, как правило, кратным 1, 10, IOO и т.д. Например, Т=l мс, 10 мс или 100 мс. Для определения величины изменения выход-. ного напряжения ДБ, измеряемого АЗУ

ll на вход управления .блока 2 памяти в момент времени t<, подают импульс выборки (фиг. 5r), а на вход управления блока 1 памяти подают импульс выборки в момент времени t (фиг. 5в), в результате чего в блоке 2 памяти запоминается напряжение U1 (фиг.5к), которое присутствовало на выходе измеряемого АЗУ 11 в момент времени t» а в блоке 1 памяти запоминается на" пряжение Uq (фиг. 5и),которое присутствовало на выходе измеряемого АЗУ 11 в момент времени t >. Напряжения с выходов блоков 1 и 2 поступают на входы дифференциального усилителя 3 где определяется разность этих напряжений d U =11, -U (фиг. 5л) .

Скорость спада выходного напряжения АЗУ будет равна

DU

Вйх, р где аБ — напряжение на выходе дифференциального усилителя; Т=г -t интервал времени между окончаниями импульсов выборки блоков 1 и 2.

Таким образом, в конце измерения на выходе предлагаемого устройства устанавливается напряжение, пропор- цирнальное скорости спада выходного напряжения, измеряемого АЗУ 11, 14065 формула изобретения

1, Устройство для измерения спада плоской части импульса, содержащее блок памяти, выход которого соединен

5 .с первым входом дифференциального усилителя, отличающееся

;тем, что, с целью расширения функцио-!

;нальнЫх возможностей и упрощения уст- 10 ройства, в него введены второй блок памяти и блок синхронизации, вход ко,торого является входом устройства, первый выход блока синхронизации сое динен с первыми входами первого и второ- 15 го блоков памяти, выход второго блока па-! мяти соединен с вторым входом дифферен,циального усилителя, выход которого, является выходом устройства, второй и третий выходы блока, синхронизации

;соединены соответственно с вторыми входами первого и второго блоков па мяти.

2. Устройство по и. 1, о т .л и— ч а ю щ е е с я тем, что блок син- 25

Йронизации содержит два формирователя импульсов и блок регулируемой задержжи, вход первого формирователя импуль. сов соединен с входом устройства и

30 является первым выходом блока синхронизации, выход первого формирователя импульсов соединен с входом блока регулируемой задержки и является вторым выходом блока синхронизации, выход блока регулируемой задержки соединен с входом второго формирователя импульсов, выход которого является третьим выходом блока синхронизации.

3, Устройство по п. 1, о т л ив ч а ю щ е е с я тем, что блок синхронизации содержит генератор импульсов, счетчик, дешифратор и измеряемое аналоговое запоминающее устройство, первый вход которого соединен с входом устройства, выход генератора импульсов соединен с входом счетчика, выход которого, соединен с входом дешифратора, первый выход дешифратора является вторым выходом блока синхронизации, второй выход дешифратора соединен с вторым входом измеряемого аналогового запоминающего устройства, выход которого является первым выходом блока синхронизации, третий выход дешифратора является третьим выходом блока синхронизации. фие. Я

1406530 . pace. Ф

44 е и

1406530

Составитель В. Антохин

Редактор Ю. Середа Техред JI.Cåðäþêoâà Корректор А. Тяско

Тираж 772 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ .3188/4) Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4