Процессор программируемого контроллера

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах управления технологическим оборудоваг нием. Цель изобретения - повышение быстродействия процессора программируемого контроллера. Процессор программируемого котроллера содержит сиихронизатор 1, блок 2 управления, блок 3 памяти микрокоманд, регистр 4 микрокоманд, регистр 5 управления вводом-выводом, блок 6 хранения фла гов, блок 7 анализа обрабатьшаемого бита и условий, модификатор 8, первый блок 9 ключей с трехстабильным выходом, регистр 10 кода обрабатываемого бита, второй блок 1 ключей с трехстабильным выходом, дешифратор 12 маски обрабатываемого бита, арифметико-логический блок 13, блок 14 ввода-вывода , внутреннюю шину 15 микрокоманд , внутреннюю тину J6 данных,канал 17 данных, первый элемент ИЛИ 18, , второй элемент ИЛИ 18. 15 ил. (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (5D 4 G 06 F 9/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3984412/24-24 (22) 03.12.85 (46) 30.06.88. Бюл. ¹ 24 (71) Минский конструкторско-технологический экспериментальный институт автомобильной промышленности (72) П.К,Сырель и И.Н.Сохина (53) 681.3(088.8) (56) Патент Великобритании № 1596115, кл. G 06 Е 9/22, 1981.

Патент США - 4266281, кл. 4 06 F 13/00, 1981. (54) ПРОЦЕССОР ПРОГРАММИРУЕМОГО КОНТРОЛЛЕРА (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах управления технологическим оборудова-.. нием. Цель изобретения — повышение

„Л0„„3406595 A 1 быстродействия процессора программируемого контроллера, Процессор nporpaMMvpyeMoro котроллера содержит синхронизатор 1, блок 2 управления, блок 3 памяти микрокоманд, регистр 4 микрокоманд, регистр 5 управления вводом-выводом, блок 6 хранения флагов, блок 7 анализа обрабатываемого бита и условий, модификатор 8, первый блок 9 ключей с трехстабильным выходом, регистр 10 кода обрабатываемого бита, второй блок ll ключей с трехстабильным выходом, дешифратор 12 . маски обрабатываемого бита, арифметико-логический блок 13, блок 14 ввода-вывода, внутреннюю шину 15 микро- @

O команд, внутреннюю вину l6 данных,канал 17 данных, первый элемент ИЛИ 18., 1 1 второй элемент ИЛИ 18 . 15 ил.

1406595

Изобретение относится к автоматике и вычислительной технике и может использоваться в устройствах управления технологическим оборудованием.

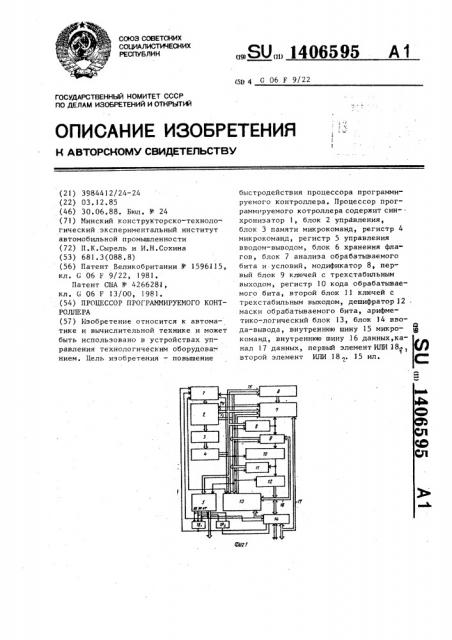

Цель изобретения — повышение быстродействия процессора, На фиг.1 приведена структурная схема предлагаемого процессора программируемого контроллера; на фиг.2 — 10 система микрокоманд процессора; на фиг.3 †. функциональная схема синхронизатора; на фиг.4 — функциональная схема блока управления; на фиг.5 функциональная схема блока анализа обрабатываемого бита и условий; на фиг.б — функциональная схема блока хранения флагов; на фиг.7 — таблица распределения функций регистров общего назначения (POH) арифметикологического блока; на фиг.8 — таблица распределения функций в регистре режима;,на фиг.9 — общий алгоритм работы процессора программируемого контроллера; на фиг.10 вЂ, алгоритм вы- 25 полнения обработки команды "Нормаль" но открытый контакт ; на фиг,11 — алгоритм выполнения команды Начало параллельной ветви"; на фиг,12 — алгоритм выполнения команды "Конец па- 30 раллельной ветви"; на фиг.13 показаны состав и разрядность шин, связывающих блоки 8-12; на фиг.14 представлена временная диаграмма работы процессора; на фиг.15 — структура блока ввода-вывода.

Процессор программируемого контроллера (фиг.1) содержит синхронизатор 1, блок 2 управления, блок 3 памяти микропрограмм (БПМ), регистр 4 микроко- ц) манд, регистр 5 управления вводом-выводом; блок 6 хранения флагов; блок 7 анализа обрабатываемого бита и условий; модификатор 8 микропрограмм, первый блок 9 ключей с трехстабильным выходом; регистр .10 кода обрабатываемого бита, второй блок 1 1 ключей с трехстабильным выходом, дешифратор 12 маски обрабатываемого бита, арифметико-логический блок (АЛБ) 13, блок 14 ввода-вывода, внутреннюю шину 15 микрокоманд, внутреннюю шину 16 данных, канал 17 данных, первый 18 и второй 18 < элементы ИЛИ.

Синхронизатор (фиг.3) содержит генератор 19, счетчик 20 тактов, дешифратор 21 тактов, второй элемент

ИЛИ 22, триггер 23, первый элемент

НЕ 24, первый элемент И 25, Блок управления процессором и ад" ресом микрокоманд (фиг,4) содержит дешифратор 26 формата микрокоманд,элементы ИЛИ 27, 28, регистр 29 возврата, второй элемент НЕ 30 элементы

2И-ИПИ 31 и ЗИ-ИЛИ 32, счетчик 33 адреса МК, Блок анализа обрабатываемого бита и условий (фиг,5) содержит мультиплексор 34, элемент ИСК1ПОЧАЮЩЕЕ ИЛИ 35, триггер Зб.

Блок хранения флагов (фиг.б) содержит элементы И 37-42 и триггеры 43-48.

Процессор работает следующим образом, Генератор 19 синхронизатора 1 (фиг.3) генерирует последовательность импульсов, которая преобразуется счетчиком 20 тактов и дешифратором 21 тактов в систему тактовых импульсов,синхронизирующих работу процессора. Тактовые импульсы поступают на входы элементов И-ИЛИ 31,32 (фиг.4) блока 2 управления.

С выходов счетчика 33 адреса МК сигналы поступают на адресные входы

БПМ 3 и определяют адрес считываемой микрокоманды. С выходов БПМ 3 информация поступает на входы регистра 4 микрокоманд, а с его выходов — во внутреннюю шину 15 микрокоманд.

Старшие разряды (MMK12-ММК15) магистрали 15 определяют формат микрокоманды (фиг.2) и поступают на дешифратор 26 формата микрокоманд (фиг.4).

С выходов дешифратора 26 формата микрокоманд управляющие сигналы (Fi) поступают на входы различных блоков процессора, определяя выполнение микрокоманды данного формата, В формате 01 выполняются команды

АЛБ 13. Код выполняемой микрокоманды определяют младшие разряды магистрали 15 микрокоманд (MMKOO-MMK11), АЛБ13, сигнализируя о своей готовности к приему микрокоманды, выставляет на выходе исполнения микрокоманд высокий уровень сигнала Ф1, который поступает на инверсный вход элемента 22 (фиг,3).

В то же время на вход элемента И 25 поступает сигнал F 01 с дешифрато-. тора 26 формата, на второй вход элемента И 25 поступает сигнал с инверсного выхода D-триггера 23, который в начальный момент установлен в нулевое состояние сигналом "Сброс" (не показан). С выхода элемента И 25 сигз 14065 нал СМП (такт АЛБ) поступает на тактовый вход AJII> 13, разрешая выполне.-. ние микрокоманды, и на второй вход элемента ИЛИ 22, с выхода ксторого поступает сигнал "Тормоз", блокирующий работу счетчика 20 тактов íà время приема и исполнения микрокоманды

АЛБ 13, который устанавливает низкий уровень сигнала ФI, С появлением сигнала "Тормоз" дешифратор 21 тактов формирует сигнал, блокирующий дешифратор 26 формата, который снимает сигнал формата F 01 и, соответственно, СМП. По окончании выполнения мик- 15 рокоманды АЛБ 13 устанавливает высокий уровень сигнала Ф1 и счетчик так" тов 20 разблокируется. Выполнению

АЛБ 13 микрокоманд с обменом-приемом информации из канала и выдаче информации в канал 17 данных должна предшествовать микрокоманда, устанавливающая соответствующие сигналы в регистре 5 управления вводом-выводом (формат F 13). Регистр 5 управления 25 вводом-выводом выполнен на микросхеме К589ИР12.

На установочные входы регистра 5 управления вводом-выводом подаются младшие разряды магистрали 15 микрокоманд. (MMKOO-MMK07).

На тактовый вход регистра 5 управления вводом-выводом поступает от дешифратора 26 формата сигнал соответствующего формата (Р 13). С выходов регистра 5 управления вводом-выводом снимаются сигналы, соответствующие адресуемому периферийному устройству (оперативное запоминающее устройство, блоки ввода-вывода, 40 пульт диагностики и другие — на чертеже не показаны), и сигналы управления выдаваемой или получаемой информацией: ЗП (запись), ЧТ (чтение), ВА (выдача адреса). Регистр 5 уп- 45 .равления вводом-выводом сбрасывается микрокомандой формата F 13 со всеми нулями в младших разрядах микрокоманды, Сигналы ВА, ЗП, ЧТ через элемент ИЛИ 18 поступают на вход D-триг- 50 гера 23. Информация о выполнении микрокоманды с обменом (наличие одного из сигналов ВА, КП, ЧТ) заносится s

D-триггер 23 по перепаду сигнала

55 элемент ИЛИ 22 включает торможение счетчика 20 тактов. Торможение снимается при появлении сигнала СП (синхронизация приема), Сигнал СП вырабаты95 вается приемником информации после того, как информация принята.. Таким образом, осуществляется асинхронный обмен между АЛБ 13 и периферийными устройствами. После снятия торможения синхронизатор 1 вырабатывает тактовый импульс, который поступает на входы элементов 2И-ИЛИ 31 и ЗИ-ИЛИ 32 и увеличивает значение счетчика 33 адреса МК на единицу, если выполнялась микрокоманда всех форматов,кроме F F F F 07.

По формату F 02 осуществляется прием команды рабочей программы пользователя (РПП), записанной в ОЗУ (не показано). Код операции команды РПП из канала 17 через блок 14 шинных формирователей поступает в шину 16 данных и на входы блока 9 ключей.

Формат F 02 коммутирует блок 9 ключей таким образом, что код операции команды РПП поступает в младшие разряды магистрали 15 микрокоманд (MMK0O-MMK05) и на установочные входы счетчика 33 адреса МК, Два разряда магистрали 15 микрокоманд (MMK06, MMK07) при приеме команды зависят от состояния модификатора 8 микропрограмм, который состоит из двух триггеров, устанавливаемых предварительной микрокомандой формата F 05. Таким образом. в счетчике 33 адреса MK устанавливается микрокомандой формата Р 02 адрес каталога (область ОЗУ), который определяется кодом операции команды РПП и состоянием модификатора 8 микропрограмм, Переключением модификатора 8 микропрограмм можно осущест визь прием одной и той же команды

РПП в четырех режимах (модификациях).

Микрокоманда формата F 03 осуществляет безусловный переход на адрес, указанный в младших разрядах микрокоманды (ММКОО-MMK11). Микрокоманда формата F 04 в зависимости от состояния триггера 36 условия (фиг,5) или осуществляет условный переход на адрес, указанный в младших разрядах микрокоманды (MMKOO ÌMÊ11)(åñëè условие выполняется), или увеличивает содержимое счетчика 33 адреса МК на

+1 (если условие не выполняется), Микрокоманды форматов F 06, F 07 осуществляют переход на вложенную подпрограмму и выход из нее. По микрокоманде формата F 06 в регистр 29 возврата (фиг.4) записывается адрес возврата из подпрограммы, содержа1406595 щийся в ММКОО-11 младших разрядах микрокоманды.Переход на вложенную подпрограмму осуществляется по микрокоманде формата F 03 (безусловный пе5 . реход). В конце вложенной подпрограммы ставится микрокоманда формата

F 07, которая осуществляет установку счетчика 33 адреса NK в значение, записанное в регистре 29 возврата.

Основной функцией процессора программируемого контроллера является быстрый анализ обрабатываемого бита (состояние анализируемого входа или выхода). Пр приему команды РПП (фор- 15 мат F 02) в регистр 10 кода обрабатываемого бита заносится из адресной части команды через блок 14 ввода-вывода и блок 9 ключей код адреса обрабатываемого бита. При поступлении ко- 2р манды анализа обрабатываемого бита (формат F 14) код обрабатываемого бита из регистра 10 кода обрабатываемого бита через блок ll ключей поступает через внутреннюю шину микроко- 25 манд (ММК02-NNK06) на адресные входы мультиплексора 34 (фиг.5). На информационные входы мультиплексора 34 поступает состояние всех входов (выходов), записанных в слове по адресу, 30 указанному командой РПП, Сигнал с выхода мультиплексора 34 поступает на вход элемента 35 ИСКЛОЧА10ЩЕЕ ИЛИ,на другой вход которого поступает разряд магистрали микрокоманд ММКОО, который указывает, на что осуществляется анализ — на "1" или "О".

В зависимости от результатов анализа обрабатываемого бита устанавливается триггер 36, на тактовый вход которого поступают сигналы форматов

F 14 или F 16. Аналогично анализу обрабатываемого бита производятся анализы состояния блока хранения флагов, магистрали состояний АЛБ 13, модифи- 45 катора 8 микропрограмм, Все эти анализы выполняются по микрокоманде формата F 16.

Формирование управляющего воздействия и выдача его по определенному выходу из группы выходов, записанных по определенному адресу таблицы состояний, производится по микрокоманде формата Р 10 (чтение маски). По этой микрокоманде код адреса обраба5 тываемого бита, поступающий из регистра 10 кода обрабатываемого бита,и дешифрованная маска обрабатываемого бита считываются из магистрали 16 данных (адреса) в РОН АЛБ 13, где и формируется управляющее воздействие на выход.

По микрокоманде формата F ll осуществляется установка флагов в блоке 6 хранения флагов, который состоит из группы D-триггеров 43-48 (фиг.6) и входной логики на элементах И 37 — 42.

В зависимости от значения разрядов магистрали l5 микрокоманд (MNKOONNKl1) устанавливается или сбрасывается тот или иной флаг. Состояние флагов анализируется блоком 7 анализа обрабатываемого бита и условий, Микрокоманды форматов F 15 и F 17 являются резервными.

Для тактирования используются две последовательности тактовых импульсов Ci и С2: Cl используется для изменения адреса микрокоманды, а С2 для записи кода микрокоманды в регистр микрокоманд, после чего начинается ее исполнение. Если микрокомандой является микрокоманда АЛБ, то формируется сигнал С синхронизации

АЛБ, Активным уровнем сигнала С является О.

Сигнал С будет находиться в активном состоянии до тех пор, пока от

АЛБ не будет получен сигнал об окончании исполнения микрокоманды И. Сигнал И снимает сигнал С и происходит переход к исполнению следующей микрокоманды.

Рассмотрим цикл записи данных, По первой микрокоманде в канал данных выставляется управляющий сигнал ВА (выдача адреса), а по следующей микрокоманде на АЛБ поступает указание о выдаче содержимого адресного регистра в канал. В АЛБ используется принцип квитирования информации, т,е. выдаваемая информация сопровождается сигналом СВ (сопровождение выдачи).

Направление сигнала СВ зависит от направления информации, Устройство-приемник информации выставляет сигнал СП (синхронизация приема), Сигнал СП всегда выдается как ответ о том, что информация приемником получена, Такой принцип позволяет производить обмен на максимально возможной скорости с высокой достоверностью.

Для завершения цикла записи процессор вь ставляет в канал управляющий сигнал ЗП (запись). Далее в ка1406595

25

60 нал выставляются данные иэ регистра данных АЛБ, которые также сопровождаются сигналом СВ и находятся в канале до-получения сигнала СП, Цикл чтения в адресной части производится аналогичном образом, а в . части чтения — по сигналу СВ, поступающему от источника считываемой информации. Данные записываются в регистр АЛБ, который выдает сигнал СП по адресу источника информации.

Процессор программируемого контроллера работает по алгоритму, представленному .на фиг.9. После нажатия кнопки "Пуск", следует программа начальной установки, в которой в регистры общего назначения АЛБ 13 заа писываются необходимые константы,модификатор 8 микропрограмм устанавливается в режим "Начальная установка

ll сбрасывается регистр 5 управления вводом-выводом, устанавливаются флаги. Счетчик адреса РПП (рабочая программа пользователя) устанавливается на номер первой команды РПП. Под счетчик адреса РПП отведен POH 15

АЛБ 13. Распределение функций регистров общего назначения (фиг.7) позволяет свести к минимуму количество об- 30 менов между процессором и периферий-. ными устройствами. Помимо четырех режимов работы процессора, устанавливае35 мых модификатором . 8 микропрограмм (начальная установка, программирова.ние, обработка, индикация), которые определяют адрес в каталоге, на который выходит процессор по приему команды, возможно выполнение еще нескольких дополнительных функций; поиск нужного элемента и высвечивание искомой цепи на экране, принудительное замыкание и:размыкание контактов внешней цепи (воздействие), функции редактирования программы (запись, .вставить, удалить) и др.

Признаки выполнения этих функций заносятся в РОН 14 (на фиг,8 приведена таблица распределений функций

РОН 14 — регистра режима) °

После того как счетчик адреса РПП установлен на первое слово РПП, анализируется переключатеЛь режима: работа/программирование. В режиме "Программирование . в 03У (не показано) заносится РПП и осуществляются функции редактирования РПП. Модификатор микропрограмм устанавливается в режим "Программирование" (не показана);8

В режиме "Работа", если модификатор 8 микропрограмм установ" лен в положение "Начальная установка" (первый цикл сканирования РПП), регистр режима обнулен, а флаг "1" установлен в "l", то программа перехо," дит на прием первой команды в режиме начальной установки, Адрес каталога, на который выходит программа по приему команды, является началом соответ-, ствующей подпрограммы, после выполнения которой осуществляется прибавление единицы в счетчик адреса РПП и переход к следующей команде РПП.

ПоДпрограммы начальной установки заносят признак обработки в таблицу состояний входов/выходов — область

ОЗУ, в которой хранятся состояния входных датчиков исполнительных механизмов. Последней командой РПП является команда "Конец программы". По этой команде производится сканирование входных датчикоВ и запись их значений в таблицу состояния входов, после чего модификатор микропрограмм .переключается в режим "Обработка", счетчик адреса РПП вновь устанавливается на адрес первой команды РПП.

В режиме "Обработка" анализируется признак Поиск" в регистре режима и при его наличии текущее слово РПП сравнивается с искомым, после чего анализируется флаг "l". Во флаге "1 " запоминается значение функции от решения нулевого уравнения текущей цепи. Если цепь замкнута, флаг "l " "равен "l" если цепь разомкнулась, то флаг "1" устанавливается в "0".

Как только последовательная цепочка размыкается, дальнейшая обработка ее контактов не имеет смысла и, если текущая команда не является началом или концом параллельной ветви (Q J) или выводом (- С )), то программа переходит к обработке следующей команды (+l в счетчик адреса РПП). Если флаг "1" равен "1", осуществляется

tl II прием команды в режиме Обработка

Прием команд Начало параллельной ветви" (), "Конец параллельной ветви" (g ) "Вывод" (- L j) осуществляется незаВисимо от состояния флага "1 ". Все подпрограммы в режиме

"Обработка" выходят на анализ индикации. Этот анализ проводится путем сравнения содержащихся в РОН адреса начала текущей цепи и адреса начала индицируемой цепи. Если индикации нет, 1406595

5

40

55

" o осуществляется переход на +1 в счетчик адреса РПП, Если текущая цепь является индицируемой, то анализируется пр знак Листинг" в р истре режима, При наличии этого признака подпрограмма "Листинг" осуществляет вывод на.экран номера команды и ее содержимого в цифровом виде, после чего осуществляется переход на +1 в счетчик адреса РПП, При отсутствии ! признака "Листинг" программа осуществляет прием команды s режиме "Индикация". Перед приемом команды модификатор микропрограмм устанавливается в режим "Индикация". После отработки соответствующей подпрограммы модификатор микропрограмм вновь переключается в режим "Обработка".

В режиме "Индикация" соответствующие подпрограммы осуществляют индикацию цепи на экране s виде релейноконтактной схемы (примеры выполнения подпрограмм в режиме "Обработка"— на фиг.10-12).

После приема команды " †1 " (фиг.10) производится формирование адреса таблицы состояний из адресной части команды и чтение содержимого таблицы состояний в РОН 11 АЛБ 13, после чего проводится анализ бита.. (одной.микрокомандой формата F 14).

Если бит равен "0", то во флаг "1": заносится "0", если бит равен "1", то состояние флага остается единичным.

При приеме команды " 1.. " (начало параллельной ветви) анализируется состояние флага "4" (во флаге "4" по команде "Начало цепи" запоминается значение флага "1").

Если перед началом параллельной ветви цепь не разомкнута (флаг "4" равен "1"), то во флаге "2" запоминается значение флага "I" то есть результат решения предыдущей параллельной ветви.

Если флаг "1" равен "1", то эта единица запоминается во флаге "2" а флаг "1" устанавливается в "0", Это позволяет исключить обработку последующей параллельной ветви, если предыдущая замкнута, - Ъ

По команде " T" (конец параллельной ветви) осуществляется функция

ИЛИ между флагами "1" и "2", результат записывается во флаг "1" (фиг,12)

Аналогично осуществляется обработка других команд РПП.

По команде "Вывод" (- ) осуществляется вывод результата (флаг "1") на соответствующее исполнительное устройство, изменение начального адреса текущей цепи (переход к обработке следующей цепи), обработка таймеров, При выполнении условия "Таймер" к текущим значениям таймеров, которые на данный момент, возбуждены, прибавляется единица, Условие "Таймер" поступает с триггера (не показан) на мультиплексор 34 условий. Триггер устанавливается частотой сети (0,) с) и сбрасывается программной микрокомандой формата

F 12 после того, как значение возбужденных таймеров увеличивается на единицу.

Алгоритм выполнения команды "Вывод на череж6 не показан.

После окончания цикла обработки РПП

25 по команде "Конец программы осущестTl

Ъ вляется сканирование входов и за пись .их . новых значений в ТС (таблицу состояний), чтение клавиатуры пульта диагностики и программирования (не показан) и запись соответствую30 щих. признаков в регистр режима. Затем в счетчик адреса РПП устанавливается номер первого слова РПП и цикл обработки РПП начинается сначала. формула изобретения

Процессор программируемого контроллера, содержащий синхронизатор, блок управления, блок памяти микропрограмм, регистр микрокоманд,арифметико-логический блок, регистр кода обрабатываемого бита, блок ввода-вывода, дешифратор маски обрабатываемо45 го бита, блок анализа обрабатываемого бита и условий, причем первый и второй выходы синхронизатора соединены соответственно с входами синхронизации блока управления и арифметикологического блока, первый выход блока управления соединен с адресным входом блока памяти микропрограмм, выход которого соединен с информационным входом регистра микрокоманд, с первого по седьмой выходы первой группы выходов блока управления соединены соответственно с первым входом блокировки синхронизатора, с первым и вторым входами запуска блока анализа обрабатываемого

1406595!

2 бита и условий, с входом синхронизации регистра микрокоманд, с входом синхронизаиий регистра кода обрабатываемого бита, со стробирующим входом дешифратора маски обрабатываемого би-! та, с входом управления записью кода операций арифметико-логического блока, выход признака результата операции арифметико-логического блока соединен 1р с первым информационным входом блока

I анализа обрабатываемого бита и условий, выход анализируемого бита которого соединен с входом условия блока управления, выход регистра обрабаты- 15 ваемого бита соединен с информационным входом дешифратора маски обрабатываемого бита, вход-выход управления приемом информации арифметикологического блока соединен с первым 20 входом-выходом признака передачи данных блока ввода-вывода и вторым входом блокировки синхронизатора, входвыход признака вывода информации арифметико-логического блока соеди-. нен с вторым входом-выходом признака передачи данных блока ввода-вывода, выход признака окончания выполнения операции арифметико-логического блока соединен с третьим входом блокиров-ЗО ки синхронизатора, о т л и ч а ю шийся тем, что, с целью повышения быстродействия, в него введены блок хранения флагов, модификатор микропрограмм, содержащий первый и вто- З5 рой триггеры, первый и второй блоки ключей с трехстабильным выходом, регистр управления вводом-выводом,пер-. вый и второй элементы ИЛИ, причем выходы регистра микрокоманд через дву- 40 направленную шину микрокоманд соединены с входами-выходами микрокоманды блока управления, с входом кода операции арифметико-логического блока, с информационным входом блока хране- 45 .ния флагов, с входом выбора логического условия блока анализа обрабатываемого бита и условий, с информационными входами первого и второго тригге-. ров, с первыми выходами первого и вто-50 рого блоков ключей с трехстабильным выходом, с информационным входом регистра управления вводом-выводом, выход первого элемента ЕЛИ соединен с входом задания режима синхронизатора и входом перевода в третье состояние блока ввода-вывода, первый информационный вход-выход которого через внутренннюю шину данных процессора соединен с информационным входом-выходом арифметико-логического блока, с выходом дешифратора маски обрабатываемого бита и с первым информационным входом первого блока ключей с трехстабильным выходом, второй выход которого соединен с информационным входом регистра кода обрабатываемого бита, выходы первого и второго триггеров соединены соответственно с вторым и третьим информационными входами первого блока ключей с трехстабильным выходом, кроме-того, выходы первого и второго триггеров объединены и подключены к второму информационному входу блока анализа обрабатываемого бита и условий, выход регистра кода обрабатываемого бита соединен с информационным входом второго блока ключей с трехстабильным выходом, выход блока хранения флагов соединен с третьим информационным входом блока анализа обрабатываемого бита и условий, с первого по третий выходы второй группы выходов блока управления соединены соответственно с входами управления третьим состоянием первого и второго блоков ключей с трехстабильным выходом и с входом синхронизации регистра управления вводом-выводом, выходы которого соединены с выходами управления вводом-выво" дом процессора, информационный входвыход процессора соединен с вторым информационным входом-выходом блока ввода-вывода, с четвертым информационным входом блока анализа обрабатываемого бита и условий, третий и четвертый вход-выход признака передачи данных блока ввода-вывода соединены соответственно с первым и вторым sxo" дами-выходами признаков передачи информации процессора, первый и второй выходы регистра управления вводом-выводом соединены соответственно с первым и вторыми входами первого и второго элементов ИЛИ, выход второго элемента ИЛИ соединен с первым входом управления направлением передачи блока ввода-вывода, второй вход управления направлением передачи которого соединен с третьим выходом регистра управления вводом-выводом и с третьим входом первого элемента ИЛИ,причем блок управления содержит регистр возврата, счетчик адреса микрокоманды, дешифратор формата микрокоманд, первый и второй элементы ИЛИ, первый элемент НЕ, элемент 2И-ИЛИ и элемент

14

35

ЗИ-ИЛИ, причем вход синхронизации блока управления соединен со стробирующим входом,цешифратора формата микрокоманд, с первым и вторым входами эле5 мента 2И-ИЛИ и с первого по третий входами элемента ЗИ-ИЛИ, с первого

iso пятый выходы первой группы дешиф ратора формата микрокоманд соединены ,соответственно с входом синхронизации 10 ,и с входом управления третьим состоя нием регистра возврата, с первым и ,вторым входами первого элемента ИЛИИ ,с.четвертым входом элемента ЗИ-ИЛИ, пятый вход которого соединен с третьим15 входом элемента 2И-ИЛИ и с шестым выходом первой группы дешифратора фор мата микрокоманд, выходы второй группы которого соединены с соответствую щими входами второго элемента ИЛИ и с 2р

:выходами второй группы блока управле.:ния, вход логического условия которого соединен с шестым входом элемента ЗИ-ИЛИ и через первый элемент НЕ с третьим входом элемента 2И-ИЛИ, вы- 25 ходы первого и второго элементов

ИЛИ соединены соответственно с пятым, входом элемента 2И-ИЛИ и седьмым входом элемента ЗИ-ИЛИ, выходы которых соединены соответственно с сумми- З0 рующим входом и с входом управления записью счетчика адреса микрокоманды, выходы которого соединены с вы,ходами первой группы блока управле, :ния, входы-выходы микрокоманды первой группы которого соединены с ин: формационными входами регистра воз, врата и счетчика адреса микрокоманды и с выходами регистра возврата, входы-выходы микрокоманды второй груп- щ пы блока управления соединены с информационными входами дешифратора формата микрокоманд, причем блок анализа обрабатываемого бита и условий содержит мультиплексор, элемент

ИСКЛЮЧАЮЩЕЕ ИЛИ и триггер, выход которого соединен с выходом логического условия блока анализа обрабатываемого бита и условий, с первого по четвертый информационные входы которого соединены соответственно с первого по четвертый информационными входами мультиплексора, выход которого соединен с первым входом элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с информационным входом четвертого триггера, синхровход которого соединен с входом синхронизации блока анализа обрабатываемого бита и условий, вход выбора логического условия которого соединен с управляющим входом мультиплексора, причем младший разряд входа выбора логического условий блока анализа обрабатываемого бита и -условий соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, причем блок хранения флагов содержит с первого по шестой триггеры и с первого по шестой элементы И, выходы которых соединены с синхровходами с первого по шестой триггеров, выходы которых соединены с выходами блока хранения флагов, информационные входы с первого по шестой триггеров соединены соответственно с нулевого по пятый разрядами информационного входа блока хранения флагов, с шестого по одиннадцатый разряды информационного входа которого соединены, соответственно с первыми входами с первого по шестой элементов И, вторые входы которого соединены с входом синхронизации блока хранения флагов.

1406595

1406595

1406595

Ц ,ф

Ф

tg

Ъ

tq

1406595

Acr<

1406595

Риг. 12

1406595

Рокпиан

l1u n чтено данных део одпена

Фиг. !4 цокл,1аьеи данных кэлаан

КЮАРа

1 ам азл ot кЭЛо5

2

5В9 б KDA 01н

1О КЭЛ 02Н

15 КЭЛООН

11 ч

cs

1

5 кэл очн

5 б кЭЛабН колоб

10 кэл ОбН

15 КЭЛ Огк араб

КЭЛ О1 ч ц

С5

V4 г ч 1 кэл овн

5 кэл аак

59 Е кРЛ 1аН кэл пн " ч

Сб о г ч

5 Ел 1гн кэл цн

1а кЭл 14Н

13 кэл 15н

Ч

55

5 канн

2 551

cs

cs ксви

Фи 15

Редактор А.Маковская

Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5,r

Заказ 3195/ 15

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 с1

cz .нк мк с и

КРЛ в

3П чт св сп

Составитель А,Афанасьев

Техред Л.Сердюкова Корректор В.Бутяга