Устройство для регистрации результатов контроля

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля цифровых логических схем и диагностики неисправностей. Цель изобретенияупрощение устройства за счет сокращения аппаратуры памяти. Логический анализатор содержит блок 1 памяти, два элемента задержки 2,3, элемент И 4, счетчик 5, регистр 6, коммутатор 7, генератор 8 импульсов, триггер 9, группу информационных входов 10, вход 11 задания режима работы , группу адресных входов 12, выход 13 готовности, вход 14 записи, вход 15 установки, группу информационных выходов 16. Анализатор работает в режимах занесения тестовой информации , записи ответных реакций и чтения ответных реакций. Положительный эффект достигается за счет использования блока 1 памяти для хране- g ния тестовых воздействий и записи ответных реакций с объекта диагностирования . 1 ил. (Л

СОЮЗ COBETCHHX

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51) 4 С 06 У ll/26

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТНЕННЬУ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

t (21) 3973363/24-24 (22) 08.10.85 (46) 30.06,88, Вюл. (Ф 24 (72) A.Í.Бучнев, О,A.Зимнович, Е.И.Карпунин и В.И.Песоченко (53) 681.3(088.8) (56) Авторское свидетельство СССР

Р 607218, кл. G 06 F 11/00, 1975.

Авторское свидетельство СССР

У 1045230, кл. G 06 F 11/26, 1983. (54) УСТРОЙСТВО Д11Я РЕГИСТРАЦИИ РЕЗУЛЬТАТОВ КОНТРОЛЯ (57) Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля цифровых логических схем и диагностики неисправностей. Цель изобретения— упрощение устройства за счет сокращеÄÄSUÄÄ 1406596 А 1 ния аппаратуры памяти ° Логический анализатор содержит блок 1 памяти, два элемента задержки 2,3, элемент

И 4, счетчик 5, регистр 6, коммутатор 7, генератор 8 импульсов, триггер 9, группу информационных входов 10, вход ll задания режима работы, группу адресных входов 12, выход 13 готовности, вход 14 записи, вход 15 установки, группу информационных выходов 16. Анализатор работает в режимах занесения тестовой информации, записи ответных реакций и чтения ответных реакций. Положительный эффект достигается за счет исР пользования блока 1 памяти для хране- Е ния тестовых воздействий и записи ответных реакций с объекта диагностирования. 1 ил ° С:

1406596

Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля логических узлов и диагностики неисправностей.

Целью изобретения является упрощение устройства путем сокращения аппаратуры памяти.

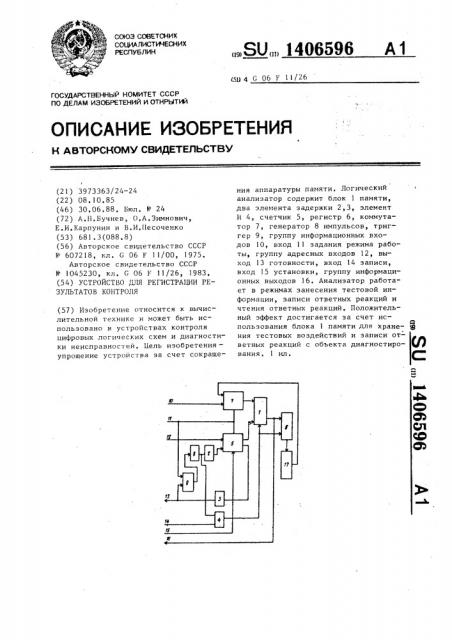

На чертеже изображено предлагае- 10 мое устройство.

Устройство содержит блок 1 памяти, два эпемента 2,3 задержки, элемент И 4, счетчик 5, регистр 6, коммутатор 7,генератор 8 импульсов,триг- 15 гер 9, группу информационных входов 10, вход 11 задания режима работы группу адресных входов 12, выход 13 готовности, вход 14 записи, вход 15 установки, группу информаци- 20 онных выходов 16. Кроме того, на чертеже :изображен объект контроля 17.

Устройство работает следующим образом.

Работа осуществляется в режимах занесения тестовой информации, регистрации ответных реакций и чтения ответных реакций. В режиме занесения тестовой информации на вход 11 задания режима работы и на вход 14 30 поступают нулевые сигналы, которые. переводят блок 1 памяти в режим записи, счетчик 5 — в режим параллельного занесения, а коммутатор 7 — в режим прохождения информации с группы информационных входов 10 устройства. В этом режиме производится запись тестовых кодов в блок 1 памяти.

На адресные входы 12 устанавливается адрес записываемой ячейки, на инфор- gp мационные входы 10 подаются тестовые коды, записываемые в данную ячейку.

Операция записи повторяется до тех пор, пока не будет записана информация во все ячейки памяти блока 1.

После этого на вход 15 установки подается положительный импульс, поступающий на вход установки счетчика 5 и устанавливающий счетчик в нуль. 3атем на входы 11 и 14 подается логи ческая единица, переводящая устройство в режим регистрации ответных реакций. Сигнал — логическая единица на входе 11 — переводит счетчик 5 в режим счета, поступает на управляющий 55 вход коммутатора 7, подключает к информационным входам блока 1 памяти выходы объекта контроля, передним фронтом устанавливает триггер 9 в единицу, разрешая работу генератора тактовых импульсов. Генератор 8 тактовых импульсов начинает генерацию тактовых импульсов с высокого уровня. Сигнал высокого уровня поступает на вход записи блока 1 памяти и задает режим чтения. Так как счетчик 5 обнулен, то читается ячейка с нулевым адресом, тестовые коды поступают на вход регистра 6. Через половину периода на выходе генератора 8 тактовых импульсов появляется низкий уровень, который переводит блок 1 памяти через элемент И 4 в режим записи, отрицательным фронтом импульса частоты информация записывается в регистр 6 и поступает на входы объекта контроля. Реакция на тестовое воздействие поступает через коммутатор 7 на информационные входы блока 1 памяти и записывается в нулевую ячейку.

Следующий сигнал — логическая единица — переводит блок 1 памяти через элемент И 4 в режим чтения и через элемент 2 задержки поступает на счетный вход счетчика 5, который по положительному фронту прибавляет единицу. Иэ блока 1 памяти считываются тестовые коды из первой ячейки. Описанная процедура чтения тестовых кодов и запись ответных реакций на них повторяется до тех пор, пока на выходе переполнения счетчика 5 не появится сигнал переполнения (он появится при записи реакции на последнее тестовое воздействие). Сигнал переполнения через элемент 3 задержки (на время записи) устанавливает в нуль триггер 9, блокирует работу генератора тактовых импульсов. Этот же сигнал поступает на выход 13 готовности, сообщая, что тестирование закончено.

После этого на входе 11 устанавливается низкий уровень, переводящий устройство в режим чтения ответных реакций. Далее чтение реакций из блока 1 памяти ведется следующим образом. На входе 14 записи устанавливается высокий уровень, а на входах 12 устанавливаются последовательно адреса ячеек блока 1 памяти. Информация с выхода блока 1 памяти поступает на информационные выходы 16. формула и з о б р е т е н и я

Устройство для регистрации результатов контроля,, содержащее блок памя1406596

Составитель И.Иваныкин с

Техред Л.Сердюкова Корректор Э.Лончакова

Редактор А.Маковская

Заказ 3195/45

Подписное

Тираж 704

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 ти, триггер, генератор импульсов, счетчик, коммутатор, регистр, элемент И и первый элемент задержки,причем группа выходов блока памяти соединена с группой информационных входов регистра, группа выходов которого является группой выходов устройства для подключения к группе информационных входов объекта контроля, выход генератора импульсов соединен с первым входом элемента И, о т л и— ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит второй элемент задержки причем пер1 15 вая группа информационных входов коммутатора является группой входов уст.ройства для подключения к группе выходов объекта контроля, группа выходов коммутатора подключена к группе информационных входов блока памяти, вторая группа информационных входов коммутатора является группой информациI онных входов устройства, управляющий вход коммутатора соединен с единич- g5 ным входом триггера, управляющим вхоpом счетчика и является входом задания режима работы устройства, группа информационных входов счетчика соединена с группой адресных входов устройства, тактовый вход счетчика через первый элемент задержки соединен с выходом генератора импульсов, установочный вход счетчика соединен с входом установки устройства, группа вы" ходов счетчика соединена с группой адресных входов блока памяти, вход записи которого объединен с тактовым входом регистра и подключен к выходу элемента И, второй вход которого является входом записи устройства, выход переполнения счетчика через второй элемент задержки соединен с нулевым входом триггера и является выходом готовности устройства, группа выходов блока памяти является группой информационных выходов устройства, выход триггера соединен с входом запуска генератора импульсов.