Частотно-фазовый детектор

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и .может использоваться в устр-вах АПЧ. Цель изобретения - улучшение темсвязи , сер. РИТ, пературной стабильности. Устройство содержит D-триггеры 1 и 2, элемент И - НЕ 3, четыре резистора 4, 5, 6, 7, конденсатор 8, операционный усилитель 9. В устройство введен второй конденсатор 10, соединенный с неи1шертирую1цим входом операционного усилителя . В результате одновременного понижения напряжения на неинвертирующем и новышения напряжения на инвертирующем входах операционного усилителя 9 напряжение на выходе частотно-фазового детектора понижается до момента прихода переднего фронта сигнала на вход синхро цизации D-триггера 1, пропорционального разности фаз входных сигналов. 1 ил.

СО)ОЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5ц 4 Н 03 D 13 00 ф(, s ",g -.; (I

ОПИСАНИЕ ИЗОБРЕТЕНИЯ! " Ц(H А BTOPGHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4078122/24-09 (22) 05.05.86 (46) 30.06.88. Бюл. ¹ 24

4й

Ж (71) Государственныи научно-исследовательский центр изучения природных ресурсов (72) В. А. Козинчук и В. А. Стрижевский (53) 621.376.6 (088.8) (56) Техника средств связи, сер. РИТ, 1982, ¹ 4, с 92, рис. 1 (54) ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР (57) Изобретение относится к радиотехнике и может использова ься в устр-вах

АГ1Ч. 1!ель изобретения - — улучшение тем„„SU„„1406717 А1 пературной стабильности. Устройство содержит Dтриггеры 1 и 2. элемент И вЂ” НЕ 3, четыре резистора 4, 5. 6, 7, конденсатор 8, операционный усилитель 9. В устройство введен второй конденсатор 10, соединенный с неинвертирую цим входом операционного усилителя. В результате одновременного понижения напряжения на неинвертируюьцем и повышения напряжения на инвертируюгцем входах операционного усилителя 9 напряжение на выходе частотно-фазового детектора понижается до момента прихода пе реднего фронта сигнала на вход синхро низации D-триггера 1, пропорционального разности фаз входных сигна.lов. 1 ил.

14067 1 7

Форму.га изобретения

Составитель Л. Колосов

Редактор Л IloB«aH Техред И. Верее Корректор 1!. Эрдейи

Заказ 3>04, 5! Тираж 928 Подписное

ВНИИПИ Госу дарственного комитета СССР по де.la ° изобретений и открытий

l 3035. Москва, Ж-- 35, Рау гпская наб., д. 4 5

Производс1венно-полиграфическое предпринтие, г Ужгород, ул. Проектная. 4

Изобретение относится к радиотехнике и может использоваться в устройствах автоподстройки частоты.

Цель изобретения улучшение температурной стабильности.

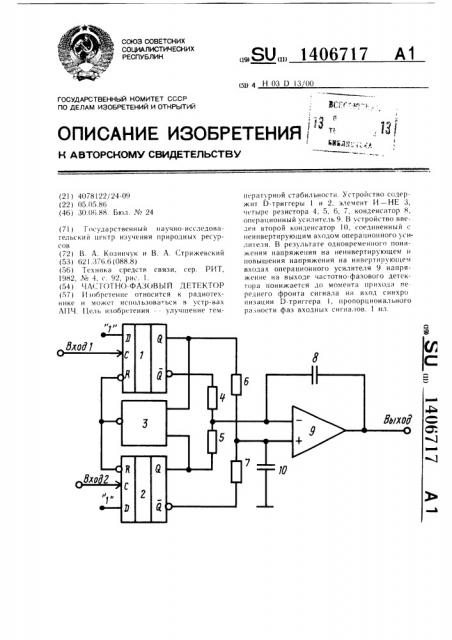

На чертеже приведена структурная электрическая схема частотно-фазового детектора.

Частотно-фазовый детектор содержит перный и второй Ртриггеры 1 и 2, элемент

И НЕ 3, четыре резистора 4, 5, 6 и 7, первый конденсатор 8, операционный усилитель 9 и второй конденсатор 10.

Частотно-фазовый детектор работает следующим образом.

В исходном «нулевом» состоянии Dтриггеров I и 2 потенциалы на обоих входах операционного усилителя 9 равны. В широком диапазоне рабочих температур синхронное изменение уровней логических «О» и

«!» на выходах D-триггеров 1 и 2 практически не влияет на выходное напряжение операционного усилителя 9.

В случае, когда сигнал на входе D-триггера 1 опережает по фазе сигнал на входе

B-григгера 2, то D-триггер 1 устанавливается н единичное состояние и второй конденсатор 10, соединенный с неинвертирующим входом операционного усилителя 9, начнет заряжаться через третий резистор

6, подключенный к прямому выходу D-триггера 1, и четвертый резистор 7, подключенный к инверсному выходу D-триггера 2, который находится в исходном состоянии.

Одновременгго ца инверсном выходе D-триггера устанавливается логический «0» и на иннертирующем входе операционного усилителя 9 напряжение понижается. Понижение напряжения на инвертирующем входе операционного усилителя 9 и повышение его на неинвертирующем входе вызывает рост напряжения на выходе частотно-фазового детектора.

Возрастание напряжения на выходе частотно-фазового детектора продолжается до прихода переднего фронта сигнала на вход

D-триггера 2. По переднему фронту этого сигнала на прямом выходе D-триггера 2 устанавливается логическая «1». Так как на обоих входах элемента И вЂ” НЕ 3 устанавливаются логические «1», то на выходе элемента И вЂ” НЕ 3 устанавливается логический «0», поступающий на входы сброса

D-триггеров и 2, которые устанавливаются в состояние логического «О», и частотно-фазовый детектор возвращается в исходное состояние. При этом на выходе частотно-фазового детектора сохраняется напряжение, пропорциональное разности фаз входных сигналов.

B lс.л9 уч а. е о0тTс тTа в а нHиHя H lс.иH!г нHа ла по фазе на входе D-триггера первым переклкучается в состояние логической «!» D-триггер 2, вследствие чего напряжение на втором конденсаторе 10 понижается за счет разряда через резисторы 6 и 7 и соответствующие выходы D-триггеров 1 и 2, находящиеся в состоянии логического «0», а напряжение на инвертирующем входе операционного усилителя 9 повышается за счет заряда первого конденсатора 8 через резисторы 4 и 5 и соответствуюгцие выходы D-триггеров, находящиеся н состоянии логической «1».

В результате одновременного понижения напряжения на неинвертирующем и повышени я напряжения на инвертирунгщем входах операционного усилителя 9 напряжение на выходе частотно-фазового детектора понижается до момента прихода переднего фронта сигнала на вход синхронизации

D-триггера 1, пропорционального разносз и фаз входных сигналов.

Частотно-фазовый детектор, содержагций первый и второй D-триггеры, входы синхронизации которых являются входами частотно-фазсвого детектора, информационные

D-входы D-триггеров являются входами логичесно г единицы частотно-фазового детектора, элемент И- -HF., входы которого соединены с прямыми выходами первого и второго D триггеров, а выход -- с входами сброса D-триггеров, четыре резистора, конденсатор и операционный усилитель, выход которого является выходом частотно-фазоного детектора, от гичающийся тем, что, с целью улучшения температурной стабильности, в него введен второй конденсатор, причем инверсный выход первого D-триггера соединен через последовательно подключенные первый и второй резисторы с прямым выходом нтсрого D-триггера, а точка соединения первого и второго резисторов подключена к иьвертирующему входу операционного усилителя и первому выводу первого конденсатора, другой вывод которого соединен с выходом операционного усилителя, прямой выход первого D-триггера соединен через последовательно подключенные третий и четвертый резисторы с инверсным выходом второго D-триггера, а точка соединения третьего и четвертого резисторов подключена к неинвертирующему входу операционного усилителя и первому ныноду второго конденсатора, другой вывод которого подключен к общей шине.