Программируемая линия задержки

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и предназначено для использования в устройствах обработки дискретной информации. Программируемая линия задержки (ПЛЗ) содержит оперативное запоминающее устройство 1 с произвольной выборкой, коммутатор 2, N буферных регистров 3ol-3.N и блок 4 управления, содержащий генератор 5 тактовых импульсов, элементы И 8,9, депгафратор 13 нулевого состояния , счетчик 7 номера отвода, счетчик 14 текущего адреса записи, регистр 16, вычитатель 15, оперативные запоминающие устройства 17,18, делитель 6 частоты, формирователь 10 случайных временных задержек, мультиплексоры 11,12, сумматор 19 и инвертор 20. ПЛЗ обеспечивает оперативное управление значениями задержек выходных сигналов и режим флуктуации значений задержек выходных сигналов на каждом независимом отводе 1 ил. (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) 53 A i (51)4 Н 03 К5 153

®Сй"ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPGKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

00 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2I) 4162552/24-21 (22) 15,12,86 (46) 30,06.88, Бюл. Ф 24 (71) Ленинградский электротехнический институт связи им.проф.

М.А.Бонч-Бруевича (72) А.Г.Брусенцов, А.Н.Волков и В.В.Лаюшка (53) 621.374 (088.8) (56) Авторское свидетельство СССР

Ф 1193789, кл. Н 03 К 5/153, 15.10.82. (54) ПРОГРАММИРУЕМАЯ ЛИНИЯ ЗАДЕРЖКИ (57) Изобретение относится к радиотехнике и предназначено для использования в устройствах обработки дискретной информации. Программируемая линия задержки (ПЛЗ) содержит оперативное запоминающее устройство 1 с произвольной выборкой, коммутатор

2, и буферных регистров 3.1-3.й и блок 4 управления, содержащий генератор 5 тактовых импульсов, элементы

И 8,9, дешифратор 13 нулевого состояния, счетчик 7 номера отвода, счетчик 14 текущего адреса записи, регистр 16, вычитатель 15, оперативные запоминающие устройства 17,18, делитель 6 частоты, формирователь 10 случайных временных задержек, мультиплексоры 11,12, сумматор 19 и инвертор 20, ПЛЗ обеспечивает оперативное управление значениями задержек выходных сигналов и режим флуктуаций значений задержек выходных сигналов на каждом независимом отводе. 1 ил.

1406753

Изобретение относится к радиотехнике и предназначено для использования н устройствах обработки дискретной информации, например в устройстI 5 вах моделирования многолучевых радиоканалов.

Целью изобретения является расширение области применения программируемой линии задержки за счет обеспе- 10 чения оперативного управления значениями задержек выходных сигналов и обеспечения режима флуктуаций значений задержек выходных сигналов на каждом независимом отводе линии задержки.

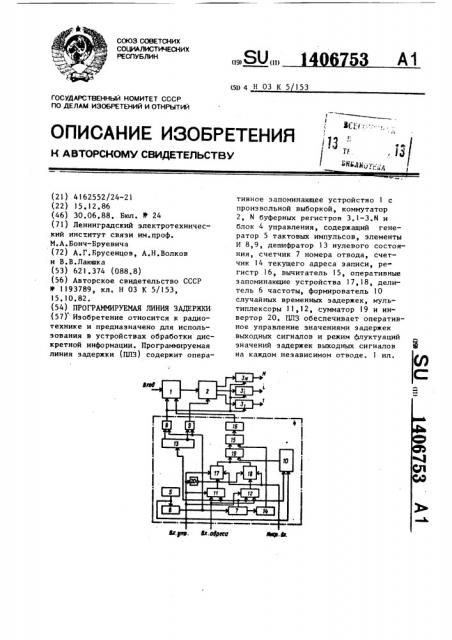

На чертеже приведена структурная схема программируемой линии задержки.

Программируемая линия задержки содержит оперативное запоминающее устройство (ОЗУ) 1 с произвольной выборкой, коммутатор 2, N буферных параллельных регистров 3.1-3.N u блок 4 управления. 25

Адресные входы и вход управления

ОЗУ 1 подключены соответственно к адресным и к первому управляющему выходу блока 4 управления, к второму управляющему ныходу которого подключен управляющий вход коммутатора 2, информационный вход которого подключен к выходу ОЗУ 1, а выходы — к входам буферных регистров 3.1-3.N.

Блок 4 управления содержит генератор 5 тактовых импульсов, подключенный выходом к входу делителя 6 частоты, выход которого соединен со счетным входом счетчика 7 номера отвода и с первыми объединенными входами эле40 ментов И 8 и 9, и к тактовому входу формирователя 10 случайных времен задержек, выход счетчика 7 номера отвода подключен к второму входу первого мультиплексора 11, первому входу второго мультиплексора 12, адресному входу формирователя 10 случайных времен задержек и через дешифратор 13 нуленого состояния — к вторым входам перного 8 и второго 9 элементов И соответСтвенно, выходы которых являются

50 соответственно первым и вторым управляющими выходами блока 4 управления, выход переполнения счетчика 7 номера отвода соединен через счетчик 14 текущего адреса записи с первым входом нычитателн 15, подключенного выхоцом через регистр 16 к адресным выходам блока 4 управления, Первый вход перного мультиплеКсора 11 соединен с вторым входом второго мультиплексора

12 и является адресным входом блока

4 управления, выходы первого 11 и второго 12 мультиплексоров подключены к адресным входам первого оперативного запоминающего устройства 17 и второго оперативного запоминающего устройства 18-соответственно, выходы которых объединены и подключены к первому входу сумматора 19, а объединенные информационные входы являются информационными входами блока 4 управления, Управляющие входы первого 11 и второго 12 мультиплексоров объединены и подключены к управляющему входу первого оперативного запоминающего устройства 17, который одновременно является управляющим входом блока 4 управления, и через иннертор 20 — к управляющему входу второго оперативного запоминающего устройства 18. Выход формирователя 10 случайных времен зацержек соединен с вторым входом сумматора 19, выход которого подключен к второму входу вычитателя 5.

Программируемая линия задержки работает следующим образом.

Импульсы генератора 5 тактовых импульсов, поступая через делитель 6 частоты на счетный вход счетчика 7 номера отвода, переводят его последовательно в положения от 0 до 1. Информация с выходов счетчика 7 номера отвода н виде параллельного кода через первый мультиплексор 11 (при подаче на вход управления, например, низкого уровня напряжения) поступает на адресные входы перного оперативного запоминающего устройства 17 значений задержек, определяя адрес ячейки памяти, н которой хранится двоичное число (коэффициент задержки), пропорциональное времени задержки на 1-м отводе линии. Импульсы переполнения счетчика 7 номера отвода поступают на счетный вход счетчика

14 текущего адреса записи, переводя

ere последовательно н положения от

0 до М (где M — количество ячеек памяти оперативного запоминающего устройства 1). Информация с выходов первого оперативного запоминающего устройства 17 значений задержек и формирователя 10 случайных времен задержек, поступает на входы сумматора

19, где происходит сложение значений

1406753 задержек из первого оперативного запоминающего устройства 17 со сформированными н формирователе 10 случайных времен задержек кодами задержек с учетом их знака. С выхода сумS матора 19 информация поступает на первый нход нычитателя 15, на второй вход которого поступают значения с выхода счетчика 14 текущего адреса записи.

В вычитателе 15 определяется адрес ячейки оперативного запоминающего устройства I иэ которой производится считывание информации для фор15 мирования выходного сигнала для 1-го отнода линии. Эта информация окаэьг вается задержанной по отношению к текущему времени, которое определяется состоянием счетчика 14 текущего адреса записи, на число тактов, вычисленное н сумматоре 19, Вычисленный адрес ячейки поступает на адресные входы оперативного запоминающего устройства I через регистр 16. Считы-25 ванне и запись в оперативное запоминающее устройство 1 происходит в зависимости от состояния счетчика 7 номера отвода. При поступлении информации на.входы дешифратора 13 нулево- 0

ro состояния с выходов счетчика 7 номера отвода для его состояний с- 1 до N с прямого выхода дешифратора 13 нулевого состояния снимается сигнал, запрещающий прохождение импульсов тактовой частоты от делителя 6 часто- 35 ты через элемент И 8, в результате последний вырабатывает сигнал, устанавливающий оперативное запоминающее устройство 1 в режим считывания.

Прн нулевом состоянии счетчика 7

40 номера отвода с прямого выхода дешифратора 13 нулевого состояния поступает сигнал на элемент И 8, раэрешанг щий прохождение через него одиночно- 45

ro импульса тактовой частоты, на время присутствия которого оперативное запоминающее устройство 1 установлено в режим записи и происходит запись входного сигнала в оператив50 ное запоминающее устройство I . При состояниях счетчика 7 номера отвода от 1 до N вычитатель 15 последовательно во времени формирует N адресов считываний иэ оперативного запоминающего устройства 1 сигнала, за55 писанного н него. Оперативное запоминающее устройство I в соответствии с вычисленными адресами вырабатывает

N сигналов, соответствующих сигналам на отводах на текущем такте работы линии задержки. Двоичное слово с выхода оперативного запоминающего устройства I поступает на коммутатор 2, необходимый для повышения нагруэочной способности оперативного запоминающего устройства 1 и для коммутации поступающих на его вход параллельных двоичных сигналов последовательно н буферные регистры 3 ° 1 — З.N. Коммутация осуществляется тактовыми импульсами управления с выхода делителя

6 частоты, проходящими через элемент

И 9 при наличии сигнала разрешения, поступающего,с инверсного выхода дешифратора 13 нулевого состояния для состояний счетчика 7 номера отвода с 1 до 1.

Для нулевого состояния счетчика 7 номера отвода дешифратор 13 нулевого состояния запрещает прохождение тактовых импульсов на управляющий вход коммутатора 2 и его переключения не происходит. Параллельный код с выходов коммутатора 2 поступает на информационные входы буферных регистров 3.1-3.N, запись в которых происходит при поступлении на их управляющие входы одиночного импульса тактовой частоты с выхода элемента И 8 при нулевом состоянии счетчика 7 номера отвода одновременно с записью в оперативное запоминающееся устройство 1 следующего значения входного сигнала. При состоянии счетчика 7 номера с 1 до Й буферные регистры 3,1З.N находятся в режиме хранения ин- формации. Входы буферных регистров

3.1-3.N представляют собой отводы линии задержки, с которой снимают выходные сигналы.

Операция по определению адреса считывания и само считывание иэ оперативного запоминающего устройства 1 в буферные регистры 3.1-3.N повторяется М раэ за один такт работы линии задержки. Длительность одного такта равна N периодам импульсов делителя 6 частоты. N-й тактоный импульс, поступая на счетчик 7 отвода, переводит его из N-го состояния в нулевое, при этом формируется импульс переполнения, поступающий на счетный вход счет1 чика 14 текущего адреса записи и переводящий его н следующее положение (m+I). При новом положении

5 14 счетчика 7 номера отвода в нычитателе 15 из кода, поступающего из счетчика 14, вычитается нулевой код, считанный с первого оперативного запоминающего устройства 17 (либо из второго оперативного запоминающего устройства 18) требуемого значения задержки. В этом такте на выходе формирователя 10 случайных нремен задержек появляется нулевой код, вследствие чего информация на выходе сумматора остается нулевой. Результат на выходе вычитателя 15 является адресом записи входного сигнала для данного такта. Далее работа линии циклически повтояется М раз, т,е. pо момента заполнения счетчика

14 текущего адреса записи, после чего М+1 импульс на входе счетчика

14 текущего адреса записи переводит его в нулевое состояние и запись входного сигнала опять идет с 0 до

М ячеек памяти.

Во время функционирования линии задержки к второму оперативному запоминающему устройству 18, находящемуся в третьем состоянии по выходу, осуществляется прямой доступ через второй мультиплексор 12 независимо от состояния счетчика 7 номера отвода. Это позволяет производить произвольную перезапись кодов задержек во втором оперативном запоминающем устройстве 18 и сопрягать данную линию задержки практически с любым устройством записи кодов задержек, н том числе и микропроцессорным. Единственным условием является то, чтобы общее время перезаписи кодов задержек во второе оперативное запоминающее устройство 18 не превышало времени функционирования линии задержки с кодами задержек, записанными н первом оперативном запоминающем устройстве

17.

При изменении на входе управления блока 4 управления урания напряжения с низкого на высокий первый 11 и второй 12 мультиплексоры подключают первые свои входы к выходу, первое оперативное запомпнакщее устройство

17 переключается н режим записи с третьим состоянием по выходу, а второе оперативное запоминающее устройство 18 — в режим считывания кодов задержек по адресам, поступающим со счетчика 7 номера отвода через второй мультиплексор 12. Перное опе06753 6 ративное запоминающее устройство, такйм образом, готово к перезаписи кодов задержек.

Емкость оперативного запоминают»е5 го устройства 1 с произвольной выборкой при параллельной к-разрядной записи входных данных выбирается из следующих соображений:

1О М, »У

T „ где M — количество ячеек памяти; ь „ — требуемая максимальная задержка; период тактовых импульсов на выходе делителя частоты, ранньп» периоду следования входной информации, Таким образом, диапазон изменения задержек на отводах линии лежит в пределах от Ттц до Т,„ . M с шагом дискретности Т,ц . Зако»» изменения задержки н указанном диапазоне опре25 деляется средними значениями коэффициентов, хранящихся н одном из двух оперативных запоминающих устройств блока управления, и коэффициентами, формируемыми формирователем случайgp ных времен задержки, и может быть выбран любым с точностью до Т,ц .

Ф о р и у л а и з о б р е т е н и я

Программируемая линия задержки, содержащая блок управления,оперативное запоминающее у.стройство с произвольной выборкой, информационный вход которого является входом устройства, а адресные входы и входы управления годключены соответственно к адресным и к первому управляющему выходам блока управления, коммутатор, информационный вход которого подключен к вы45 ходу оперативного запоминающего устройства,управляющий — к второму управляющему выходу блока управления, а выходы соединены с входами соответствующих буферных регистров, выходы которых являются выходами устройства, а управляющие входы подключены к первому управляющему выходу блока управления, причем блок управления содержит генератор тактовых импульсов, первый и второй элементы И, выходы которых являются соответственно перным и вторым управляющими выходами блока управления, а первые входы которых подключены соответственно к

1406753

Составитель А.Титов

Техред М.Ходанич

Редактор М.Бандура

Корректор Г.Решетник

Заказ 3206/53 Тираж 928 Подписное

I;H/31ÏÈ Государственного комитета СССР по делам изобретений и открытий

113035, 1 1оскна, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. 11роектная, 4 прямому и инверсному выходам дешифратора нулевого состояния, входы которого соединены с выходами счетчика номера отвода,вычитатель, первые входы которого через счетчик текущего адреса записи соединены с выходом переполнения счетчика номера отвода, регистр, входы которого подключены к выходам вычитателя, а выходы являются адресными выходами блока управления,о т л и ч а ю щ а яс я тем, что, с целью расширения области применения эа счет обеспечения оперативного управления значениями задержек выходных сигналов и обеспечения режима флуктуаций значений задержек выходных сигналов на каждом независимом отводе линии задержки, в блок управления введены первое и второе оперативные запоминающие устройства, выходы которых объединены и подключены к первым входам сумматора, адресные входы — к выходам соответственно перного и второго мультиплексоров, а объединенные информационные входы являются информационными входами блока управления, выходы суммлторл соелинени с нторымн входами вычитлтеля, л вторые нх >ды с ныходлми формирователя случлйнмх времен задержек, лдресные входы кото5 рого подключены к выходам счетчикл номера отвода, а тлктовый нход — к выходу генератора тактовых импульсон и входу делителя члстоты, подключенного выходом к счетному входу светчика номера отвода к вторым нходлм первого и второго элементов И, первые входы первого мультиплексора объединены с вторыми нхс ?олми нторого мультиплексора и являются лдресными входами блока управления, вторые входы первого мультиплексорл объединены с первыми входами второго мультиплексора и соединены с выходами счетчика номера отвода, упрлнляющие входы мультиплексоров объединены и подключены к управляющему входу первого оперативного запоминающего устройства, который одновременно является

25 управляющим входом блока управления, и через инвертор — к упрлвляющему входу второго оперативного элпоминающего устройства.