Мажоритарный элемент и @ л типа

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано в БИС на основе инжекционной логики . Цель изобретения - упрощение мажоритарного элемента И Л типа. Устройство содержит транзисторы 1-3 с инжекционным питанием, выходные транзисторы 7, 9 и 11 и промежуточные транзисторы 10 и 12. Предложенное функциональное соединение элементов схемы позволяет реализовать алгоритм работы два из трех с индикацией номера неисправного блока. 1 ип., I табл.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

06777 А1 (191 (11) (1) 4 Н 03 К 19/091 фЦ .г д 13

° с

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4155075/24-21 (22) 02.12.86 (46) 30.06.88. Бюл. 1(24 (71) Таганрогский радиотехнический институт им. В.Л.Калмыкова (72) Ю.И.Рогозов, А.В.Глоба, В.А.Колосов и Л.П.Чупрякова (53) 621.374 (088.8) (56) Разработка и исследование интегральных схем на новых типах полупроводниковых приборов. Руководство по схемотехническому проектированию цифровых БИС и сверх БИС на базе интегральной июкекционной логики. Отчет по НИР. — 1(ГР 75026315, инв.

М Б801544. М., 1979, с. 68, рис. 44. (54) 1"(А)((ОРИТАРНЬ1Й З.(1ЕМЕНТ И Л ТИПА (57) Изобретение может быть использовано в БИС на основе инжекционной логики. Цель изобретения — упрощение

2 мажоритарного элемента И Л типа. Устройство содержит транзисторы 1-3 с инжекционным питанием, выходные транзисторы 7, 9 и 11 и промежуточные транзисторы 10 и 12. Предложенное функциональное соединение элементов схемы позволяет реализовать алгоритм работы "два из трех" с индикацией номера неисправного блокa. .1 ип,, 1 табл .

1406777

Изобретение относится к импульсной технике и может быть использовано в

БИС на основе инжекционной логики.

Цель изобретения — упрощение мажог 5 ритарного элемента И Л типа.

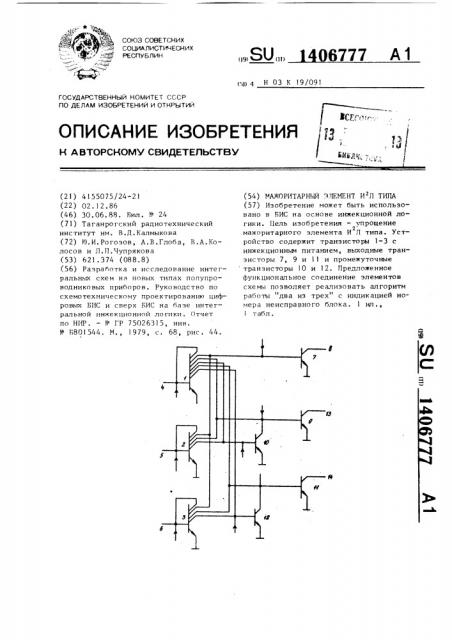

На чертеже изображена принципиальная схема мажоритарного элемента г

И Л типа.

Мажоритарный элемент содержит пер- 1р ный 1, второй 2 и третий 3 транзисторы с инжекционным питанием с весом инжектора, равным 1, базы которых соединены соответственно с пе рным 4, вторым 5 и третьим 6 входами и их со- 15 ответствукщими коллекторами. Соответствующие коллекторы транзисторов

3 соединены с базой первого выходного тр анэ ис тора 7 с инже кцио иным питанием с весом инжектора 1,5, коллектор которого соединен с ныходом 8 элемента. Соответствующие коллекторы транзисторов и 2 соединены с базой второго выходного транзистора 9 с весом инжектора 1,5 и коллектором 25 первого промежуточного транзистора 10 с инжекционным питанием с весом инжектора 0,5, база которого соединена с соответствующими коллекторами тран— зисторов 1 и 2. Соответствующие KoJIлекторы транзисторов 1 и 3 соединены с базой второго выходного транзистора 11 с инжекционпым питанием с весом инжектора 1,5 и коллектором RTo рого промежуточного транзистора 12 с инжекционным питанием с весом инжектора 0,5, база которого соединена с соответствующими коллекторами транэисторон 2 и 3. Коллекторы трачзисторов 9 и 11 соединены соответственно с первым 13 и вторым 14 выходамп номера неисправного блока. г

Мажоритарный элемент И Л типа работает следующим образом.

Для выполнения заданных функций мажоритарный элемент реализован н арифметическом базисе, для которого выходная функция F на выходе 8 и функции N,Ì, — номера неисправного 50 блока на выходах 13 и 14 имеют следующий нид:

F =P((F + F, + Е 2);

Мо l Рг (Fo + F 1) + P> (Fo + 55

+1 2)=-РР (2)

"а (Р, + F — 1) + Р (Р + где Р,, Р, Р— пороговые функции арифмической суммы входных аргументов

F,, F1 Р по порогу лва;

Р,Р— пороговые функции арифметической суммы аргументов Ро, F, Р по порогу один;

Г,V,,Р— сигналы на входах 4

6; (-) — арифметическая операция вычитания, которая (как это следует из правых частей выражений (3) и (2)) заменена Z-операцией, что позволяет реализовать предлагаемую схему с

I меньшими аппаратурными затратами.

Согласно соотношениям (1) — (3) в базы т!1анзисторов 1 — 3, которые работают в режиме токовых повторителей с коэффициентами передачи по каждому из колз екторон, равному единице, инжектируется по одному дискрету тока, н базы промежуточных транэисторон 10 и 12, которые реализуют пороговые функции Рг, Р„ согласно выражениям (2) и (3), ипжектируется половина дискрета тока (0,5I), н базы выход— ных транзисторов 7, 9 и 11, которые реализуют функции соответственно Р1, 1 !, инжектируется полтора дискре тв тока (1,5I) .

В предлагаемом элементе используется принцип функционально-схематической а нтеграции, суть которого заключается B совмещp.íèè н одном элементе выполнения нескольких функций.

В данном случае транзисторы 1О и 12 ныпо .няют функцию не только пороговых детекторов, но и иннерторов, так же, как и транзисторы 9 и 11.

Мажоритарная схема дна из трех реализ ует выходную функцию F npaвильно, если хотя бы два иэ трех входящих сигналов идентичны, причем на выходах 13 и 14 устройства (М,!1,) указывается, какой из входных сигналон не совпадает с двумя другими.

Рассмотрим работу схемы при F о.

Б .-:том случае транзисторы I — 3 закрыты, поэтому через их коллекторы не отбираются токи, инжектируемые в базы транзисторон 7, 10 и 12.

140Ь777

F F=Ð, Р Р еисправный лок, М

О 1 1

Третий

О О 1 О 1 О

0 О 1 О

Второй

О О 0 0 1

О 1 О О О

О О

О

0 !

Первый

Транзисторы 7, 10 и 12 нас ыщени (F = О), что приводит к закрытию транзисторон 9 и 11 М = М, = 1, т. е. нсе три Bx(>JII(l lx сигнала ранiиl между

5 собой (неисправного блока нет) .

Лри 1 О = F, = Р = 1, транзисторы

2 и 3 открыты и каждый отбирает через свои коллекторы по одному дискрету тока, а с базы транзистора 7 три дискрета тока. Следовательно, транзисторы 7, 9 — 12 закрыты: F = ), Мо = 1 (неиспранного блока нет) .

При Fо = F = О, F — — 1 транзисторы 2 и 1 закрыты, а транзистор 3 отбирает через свои коллекторы один дискрет тока с баз транзисторов 7, 11 и 12. Поэтому транзистор 12 закрыт (в его базу инжектируется

0,5.t), а транзистор 11 открывается 20 (M, = О), так как с базы транзистора

10 ток не отбирается, он открывается и своим кол и ктором закрывает транзистор 9 (М = 1) . С базы транзистора 7 отбирается один дискрет тока, что недостаточно для его запирания (F = О), т.е. на выходах 13 и 14 имеем комбинацию 11, = 0, E1 = 1, что говорит о неисправности третьего блока (сигнал по янине 1 ).

Аналогично рассмотрим работу устройства при других комбинациях входных сигналов (см. таблицу).

Номер неисправного блока кодирует— ся следующим образом. М „= М „=- 1 все блоки ис пранны; ь1„=- 1, 1, = О неисправен третий блок; М = О, М, — 1 — ..неисправен второй блок; М„ — М< = Π— неисправен первый блок.

Из таблицы видно, что мажоритарный

40 элемент реализует ал горитм работы мажоритарной схемы дна иэ трех с индикацией номера неисправного блока.

Ф о р м у л а и э о б р е т е н и я в

Мажоритарный элемент И J! типа, содержащий первый, второй и третий

О О О О О О О нходпые транзисторы с инжекпионным питанием, базы которых соединены соответственно с первым, вторым и третьим входами, первые коллекторы первого и второго входных транзисторов соединены с базой первого выходного транзистора с инжекционным питанием, коллектор которого соединен с выходом э 1емента, нторой коллектор первого входного транзистора соединен с базой н торо гo выходного транзистора с инжекционным питанием и коллектором первого промежуточного транзистора с инжекционным питанием, база которого соединена с вторым коллектором второго входного транзистора, третий коллектор первого входного транзистора соединен с базой третьего выходного транзистора с инжекционным питанием и коллектором второго промежуточного транзистора с инжекционным питанием, база которого соединена с первым коллектором третьего входного транзистора, коллекторы второго и третьего выходных транзисторон соединены соответственно с первым и вторым выходами номера неисправного блока, отличающийся тем, что, с целью упрощения, четвертый и пятый коллекторы первого входного транзистора соединены соответстненно с базами первого и второго промежуточных транзисторов, второй коллектор третьего входного транзистора соединен с базой первого выходного транзистора, третьи коллекторы второго и третьего входных транзисторов соединены соответственно с базами второго и третьего выходных транзисторов, а шестой дополнительный коллектор первого входного транзистора и четвертые коллекторы второго и третьего входных транзисторов соединены соответственно с их базами.

1406777

Продолжение таблицы

5 6 7 б 9 10

Ъ 4

I 0 0

1 0 1

0 1

I 1

Первый

Второй

I 1

1 1

Третий

Составитель A.ßíîB

Техред М.Дидык

Корректор А ОбРУчаР

Редактор Е.Копча

Заказ 3207/54 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

0 1

0 1

1 I

1 1

0 0 0

1 0 1

0 1 0

1 1 1