Логический элемент на полевых транзисторах

Иллюстрации

Показать всеРеферат

Изобретение относится к микроэлектронике и может быть использовано в цифровых интегральных схемах, аналого-цифровых преобразователях. Цель изобретения - повышение помехозащищенности и надежности работы устройства . Логический элемент состоит из инвертирующего транзистора (Т) 1, нагрузочного Т 2 и нагрузочного блока 3 с вьгоодами 4-6. Т I и 2 выполнены с одинаковыми пороговыми напряжениями Ur . Между выводами 4 и 5 нагрузочного блока 3 задан источник тока Т , а между выводами 5 и 6 - источник опорного напряжения . В описании приведены примеры выполнения Т 1 и 2 и нагрузочного блока 3. 4 з.п. ф-лы, 6 ил. S S (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (291 (121

А1 (522 4 Н 03 К 19 094

®Q и .7

i3„

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИ4ЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4168755/24-21 (22) 29,12.86 (46) 30.06.88, Бюл ° ¹ 24 (71) Московский институт электронной техники (72) В,А.Братов, Л.H.Кравченко, А.H.Сапельников, В.И.Старосельский, B.È.ÑóýòèH0â и А.И.Хлыбов (53) 621.374(088.8) (56) Европейский патент N - 0036791, кл. Н 03 К 19/094, Авторское свидетельство СССР

N 1050118, кл. H 03 К 19/094. (54 ) ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА ПОЛЕВЫХ

ТРАНЗИСТОРАХ (57) Изобретение относится к микроэлектронике и может быть использовано в цифровых интегральных схемах, /. аналого- цифровых преобразователях.

Цель изобретения — повышение помехозащищенности и надежности работы устройства. Логический элемент состоит из инвертирующего транзистора (Т) 1, нагрузочного Т 2 и нагрузочного блока . 3 с выводами 4-6. Т 1 и 2 выполнены с одинаковыми пороговыми напряжениями 1 .. Между выводами 4 и 5 нагруt зочного блока 3 задан источник тока

Т, а между выводами 5 и 6 — источник опорного напряжения U В описании приведены примеры выполнения Т 1 и 2 и нагрузочного блока 3. 4 з,п, ф-лы, 6 ил, 1406778

35 (ц 11 )(-. (11 111 1- +т из которого можно выра »ить»»л»»ряже»»»»е переключения

»! П +U "=+ о

П О»» где p: — крутизна первого тра»»эисторл; крутизна второго трлнэисторл.

45

Чтобы напряжение переключения ие зависило от разброса технологических параметров в случае изготовления транзисторов 1 и 2 нормально открытыми (U<<0), необходимо нагрузочньпf блок 50 выполнить так, чтобы выполнялось равенство

+ i 0 >

К! -Ка

U с (3, 55 тогда напряжение переключения равно х

=11

of> W !

11 1 С2 !

Устройство относится к микроэлектронике и может быть использонано н цифровых интегральных схемах, аналого-цифровых преобразователях.

Целью изобретения является повышение помехозащищенности и надежности работы за счет стабилизации и сужения зоны напряжения переключения.

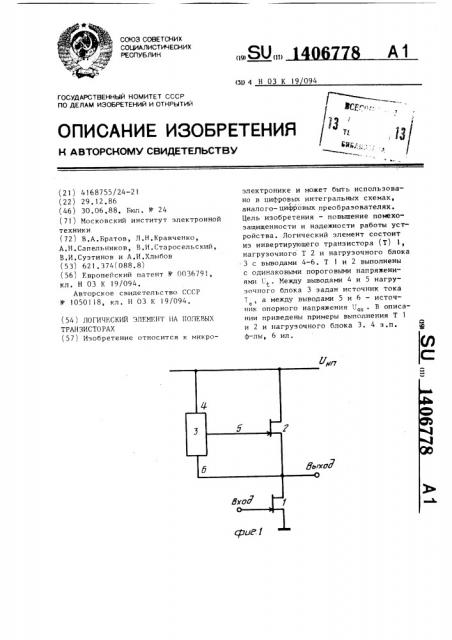

На фиг, 1 изображен логический 1р элемент на основе полевых транзисторов и нагрузочного блока; на фиг. 2-4 примеры выполнения нагрузочного блока; на фиг. 5 — схема логического элемента с повьппенным выходным сопро- 15 тивлением нагрузки; на фиг. 6 графически изображен принцип действия ло— гического элемента.

Логический элемент (фиг. I) состоит из инвертирующего 1 и нагрузоч- 20 ного 2 транзисторов и нагрузочного блока 3 с тремя выводами 4-6. Оба транзистора выполнены с один.экоными пороговыми»»апряжениям!» »1, . Между выводами 4 и 5 нагрузоч»»ого блока элд;»f» 25 источник тока Т, между ныводлми 5 и

6 — источник опорного нлпряж! ния

Напряжение переключения элемеиП та можно получить иэ условия раве»!— ства тока и»»вертирую»»»его трлизисто — 3p ра, который в момеит переключения спставляет (11 t . » . току нлгру.»ки, состоящего »»:«"» ка транзисторл, рлнл ного (11 -»»t, и тока блока 3 >О.

Это услоние в»,»1>ажио тr я рлвеиством и его зависимость от величины порогоI ного напряжения исключ аетс я, где Ж вЂ” ширина канала первого тран-! зистора;

W — ширина канала второго транзистора.

Пример выполнения нагрузочного блока, при котором условие легко реализуется, показан на фиг ° 2. Он состоит из нормально открытого транзистора 7 и диода 8. Величина опорного напряжения в блоке определяется падением напряжения на диоде 1!О, а ток

1 †. транзистором 7. Величина Т о о находится из BAX транзистора для напряже»»ия затвор — исток, равного нулю

Т,= -»-1, ° (5?

Подставляя (5) в (3), получим (6? (;»-F !-v q> =0

W Wg или, учитывая, что-> К условие (6 ) преобразуется к виду (7) >> —, +»7

Тлк»»»! с>бразом, задан соотношение (, 7 для ширины канала транзисторов 1, 2 и 7, получим, что напряжение переклк чения определяется выражением (4), которое с учетом того, что имеет н»»д

1 1

11 =11

-и D W ! (8) Выражение (8 ) показывает, что при

of!»»»»;1f»f»oM выполнении нагрузочного б:»! кл»1с»пряжение переключения зависит тс>лько от падения напряжения на диоде и соотношения ширины канала транзисторов 1 и ". Эти параметры наиболее восироизнодимы н технологическом процессе, что и дает возможность стабилизировать напряжение переклк>че»»ия и добиться положительного эффекта — повысить помехозащищенность и надежность элемента, При этом изменение других параметрон транзисторов (порогового напряжения, крутизны, максимального тока и других? ие сказывается на величине напряжения переключения, так как транзисторы ныполня!0Tñÿ в одном технологическом цикле, и уход их параметров проис. ходит одновременно с высокой степенью корреляции. Указанные факторы способствуют сохранению быстродейст1406778 ния наряду с улучшением иомехозащищеииости.

Другой способ стабилизации напряжения переключения, который может

5 быть использован как для нормально открытых, так и для нормально закрытых транзисторов, заключается н том, что нагрузочный и инвертирующий транзисторы выполняются идентичными, т.е.

WI=Ъ и p;I=v<, а в нагрузочном блоке ток задаетея достаточно малым, о чтобы выполнялось условие

- о и

"оч

Г,, (9) !5

Условие (9) означает, что ток много меньше тока нагрузочного транзистора (обычно в 10-100 раз .

При указанном условии и г; = на z. пряжение переключения, определяемое формулой (2), составляет (1О! п !оп

Примеры выполнения иагрузочиого 25 блока для логического элемента с напряжением переключения, равным опорному, показаны иа фиг. 2-4. При этом выполнение услс1вия (9) н иагрузочном блоке на фиг. 2 может быть обес- Зп печено соответствующим выбором ширины и длины капала иормалы о открыто— го транзистора 7, а н нагрузочных блоках иа фиг, 3 и 4 — выбором сопротивлений резисторон таким образом, чтобы при всех возможны ; состояниях логического элемента условие I 9, 35 также выполнялось.

В рассмотренном методе стабилизации напряжения переключения иредио40 лагается, что полевые транзисторы в пологой области ВАХ ирс дстанляют собой источники тока, близкие к иде— альным. Такое предположение оиравдано для относительно длиииокаиальных транзисторов, B то время как в короткоканальных, наиболее быстродеистнующих транзисторах, выходное сопротивление существенно меньше и ток стока заметно зависит от напряжения исток

50 сток. F этом случае стабилизацию напряжения переключения логического элемента следует осуществлять с использованием доиолиительиото нагрузочного блока и доиолнительного нагрузочиого

55 транзистора, как -1то показано и схеме логического элемента иа фи.. 5.

1огический элемент cîñòîèò из иивертирующего 1 и нагру амичис го 2 транзисторов, нагруэочного блока 3 с выводами 4-6, дополнительного нагруэочного транзистора 9 и дополнительного нагрузочного блока 11 с выводами 11 †.

13 ° Все транзисторы выполнены с одинаковыми пороговыми напряжениями, а нагрузочные блоки аналогичны описанным.

В данном варианте логического элемента принцип стабилизации напряжения переключения сохранения и нагрузочный блок 3 может быть выполнен по схемам на фиг. 2-4. Дополнительные транзистор 9 и блок 10 стабилизируют напряжение исток — сток нагрузочного транзистора 2, что приводит к повышению выходного сопрэтивления нагрузки, даже в случае использования короткоканальных транзисторов.

Источник тока в блоке 10 Т, должен о быть много меньше, чем ток нагрузки, чтобы выполнялось условие где Т вЂ” ток источника тока блока 3. о

Это дает возможность пренебречь дополнителыгым током блока 10 и оставляет в силе полученные соотношения для параметров транзисторов и блока 3.

Опорное напряжение в блоке 10 должно иметь величину, обеспечинающую работу блока 3 и транзистора 2 в качестве источников тока, Транзистор 7 должен обладать крутизной не меньшей, чем транзистор 2.

Лля этого ширина канала транзистора

9 должна быть больше или равна ширине канала транзистора 2, что обеспечивает согласование токов этих транзисторон.

11агрузочный блок 10 может быть реализован по схемам, показанным на фиг. 2 и 3, причем для получения требуемого опорного напряжения количество диодов в блоке может быть увеличено или использована обратная ветвь диода.

Целесообразно транзистор в блоке

10 выполнять длинноканальным (резистор высокоомным), что обеспечивает высокое выходное сопротивление и достаточно малую величину тока.

Логический элемент на фиг, 5 работает следующим образом.

При изменении на входе логическо1! в го элемента сигнала от уровня 1 до уровня "0" возрастание выходного на778

5 1406 пряжения происходит в момент равенства входного напряжения напряжению переключения. При использовании в логическом элементе полевых, транзисторов

r> с барьерным переходом и в случае, если нагрузкой служит аналогичный логический элемент, высокое выходное напряжение ограничивается на уровне напряжения отпирания барьерного перехо- «р да переключающего транзистора следу ющего каскада,и хотя потенциал истока нагрузочного транзистора 2 в процессе переключения меняется, напряжение затвор — исток и исток — сток благо- 15 даря транзистору 9 и нагрузочным блокам 3 и 10 остаются неизменными. Это определяет и постоянство нагрузочного тока, который после запирания транзистора 1 течет в затвор транзистора 2р (или диод) следующего каскада.

Поскольку нагрузочный ток не зависит от потенциала на выходе, выключение логического элемента происхо— дит при том же напряжении, что и 2 включение. и нагрузочный транзисторы выполнены нормально открытыми, а нагрузочный блок выполнен на основе нормально открытого транзистора и диода, причем сток транзистора подключен к первому выводу нагрузочного блока, соединенные исток и затвор подключены к второму выводу нагрузочного блока и первому выводу диода, второй вывод которого подключен к третьему выводу нагрузочного блока, при этом ширина канала переключающего транзистора равна суммарной ширине каналов нагрузочного транзистора и транзистора блока.

Э. Элемент по п. 1, о т л и ч аю шийся тем, что, с целью упрощения технологии изготовления, нагрузочный блок выполнен на основе последовательно включенных резистора и диода, причем резистор подключен к первому выводу нагруэочнрго блока, точка соединения резистора и первого вывода диода — к второму выводу, а второй вывод диода — к третьему выводу.

Ф о р м у л а и з о б р е т е н и я

«с, 1. Логический элемент на полевых Зр транзисторах, содержащий переключан щий и нагрузочный транзисторы с одинаковым пороговым напряжением и нагрузочный блок с двумя выводами, при этом исток переклн1чающего транзистора соединен с общей шиной, затвор подключен к шине входног.о сигнала, сток соединен с истоком нагрузочного транзистора, сток которого подкл)пчен к шине питания и к первому выводу на- g() грузочного блока, второй вывод которого соединен с затвором нагрузочного транзистора, отличающийся тем, что, с целью повьпцения надежности и помехозашише)шости за счет ста- д, билизации напряжения переключения, нагрузочный блок снабжен третьим выводом, подключенным к истоку иагрузочного транэистnpa, причем между первым и третьим выводами нагрузочного блока включен источник тока, а между вторым и третьям выводами — источник опорного напряжения.

2. Элемент по п, 1, о т л и ч аю шийся тем, что переключающий

4. Элемент по и. 1, о т л и ч аю шийся тем, что, с целью упрощения технологии изготовления, нагрузочный и переключающий транзисторь) идентичны, нагрузочный блок выполнен на основе трех резисторов и диода, причем первый резистор включен между первым выводом нагрузочного блока и первым выводом диода, второй вывод которого подключен к третьему выводу нагрузочного блока, второй и третий резисторы включены последовате.п,по между выводами диода, а точка их соединения подключена к второму выводу нагрузочного блока.

5. Элемент по и. 1, о т л и ч аю шийся тем, что сток нагрузочного транзистора подключен к шине питания через дополнительный транзистор, при этом сток нагрузочного транзистора соединен с истоком дополнительного транзистора, сток которого подключен к шине питания и к первому вь)воду дополнительного нагрузочного блока, а затвор — к второму выводу дополнительного нагрузочного блока, третий вывод которого соединен с истоком нагрузочиого транзистора.

1406778

Унп

1406778

Составитель А.Цекановский

Редактор Е.топча Техред М.яндык Корректор В.Бутяга

Заказ 3207/54 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Pã.óøñêàÿ наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4