Устройство для приема биимпульсных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи, может использоваться в системах передачи данных, использующих самосинхронизирующиеся коды. Цель изобретения - повышение достоверности приема путем уменьшения вероятности появления групповой ошибки. В устройстве осуществляется коррекция групповых ошибок, вызванных переходом приемника под воздействием ошибок в режим обратной работы. Для рещения поставленной цели в устр-во введены три элемента И 7, 9, 8, три регистра сдвига 11, 12, 10, два инвертора 13, 14, два триггера 15, 16 и элемент ИЛИ 17. 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСИОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (61) 1019656 (21) 4177361/24-09 (22) 09,01.87 (46) 30.06.88. Бюл. У 24 (72) Ю.И.Лосев и А.П.Орлов (53) 621, 394. 62 (088, 8) (56) Авторское свидетельство СССР

У 1019656, кл. Н 04 L 17/16, 1982. (54) УСТРОЙСТВО ДЛЯ ПРИЕМА БИИМПУЛЬСНЫХ СИГНАЛОВ (57) Изобретение относится к технике связи, может использоваться в системах передачи данных, использующих

„„SU„„1406809 A 2 само синхронизирующиеся коды. Цель изобретения — повышение достоверности приема путем уменьшения вероятности появления групповой ошибки. В устройстве осуществляется коррекция групповых ошибок, вызванных переходом приемника под воздействием ошибок в режим обратной работы. Для решения поставленной цели в устр-во введены три элемента И 7, 9, 8, три регистра сдвига 11, 12, 10, два инвертора 13, 14, два триггера 15, 16 и элемент ИЛИ 17. 3 ил.

1406809

Изобретение относится к технике связи„ может быть использовано в ! системах передачи данных, использующих самосинхронизирующиеся коды, и является усовершенствованием изобретения по авт.св. N- 1019656.

Цель изобретения — повышение достоверности приема путем уменьшения вероятности появления групповой 10 ошибки.

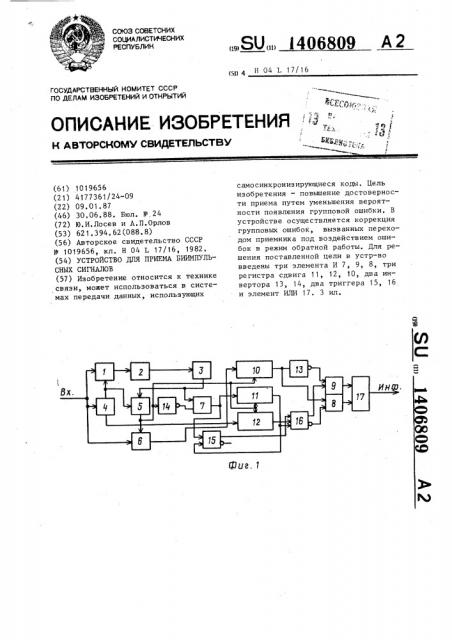

На фиг. 1 изображена структурная электрическая схема предлагаемого устройства; на фиг ° 2 — структурная схема генератора тактовых импульсов; на фиг. 3 - структурная схема решаю,щего блока.

Устройство содержит первый регистр 1 сдвига, дешифратор 2, формирователь 3 импульсов, генератор 4 20 тактовых импульсов, делитель 5 частоты, решающий блок 6, первый 7, третий

8 и второй 9 элементы И, четвертый I0 второй 11 и третий 12 регистры сдвига, второй 13 и первый 14 инвер- 25 торы, первый 15 и второй 16 триггеры

;и элемент ИЛИ 17.

Генератор 4 состоит из первого 18 и второго 19 блоков задержки, второго

20 и первого 2 1 дифференцирующих бло- 30 ков, первого 22 и второго 23 элемен тов ИЛИ, инвертора 24 и элемента

И 25.

Решающий блок 6 образуют дифференциру щ и бл 26, ементы И 27 и 28 35 и триггер 29, Устройство работает следующим образом.

На вход приемника поступают сообщения, представленные с помощью би- 40 импульсного кода (полагается,что предварительно осуществлено восстановление формы и длительности принимаемых импульсов) ° В генераторе 4 такToBblx HM b< .o < . o b 6JIoKa 18 45 задержки осуществляется задержка принимаемой последовательности на полонину периода следования символов. После дифференцирования дифференцирующими блоками 20 и 21 фронтов посылок этих последовательностей на выходе .>лемента ИЛИ 22 формируется последовательность синхронизирующих импульсов (СИ), имеющих период следования в два раза выше, по сравнению с принимаемыми символами. Эти импульсы че-

55 рез элемент ИЛИ 23 поступают на выход генератора 4 тактовых импульсов °

Возникновение ошибки в принимаемом сообщении приводит к невыдепению СИ.

Для обнаружения пропуска СИ и< пользуются блок 19 задержки, инвертор 24 и элемент И 25. В том случае, если

СИ отсутствует, то происходит его вставка с помощью блока 19 задержки (время задержки которой равно периоду следования СИ). Отсутствие СИ на первом входе элемента ИЛИ 23 в установленное время фиксируется с помощью элемента И 25, на выходе которого в этом случае формируется сигнал наличия ошибки в принимаемом символе.

Преобразование принимаемых сообщений из биимпульсного кода в двоичный осуществляется в решающем блоке 6 ° В этом случае используется такое свойство биимпульсного кода, как наличие посередине битового интервала отрицательного импуяьса дифференцирования при приеме единичного символа и положительного при приеме нулевого символа. Исходя из того, что логические элементы, в основном, используют однополярные импульсы, дифференцирующие блоки в предлагаемом устройстве имеют два выхода. На первом выходе формируются положительные импульсы, соответствующие отрицательным импульсам дифференцирования, а на втором — положительным импульсам дифференцирования. В соответствии с этим в решающем блоке 6 первый выход дифференцирующего блока 26 через элемент И 27 соединен с входом установки триггера 29 в единичное состояние, а второй выход через элемент

И 28 — с входом установки триггера в нулевое состояние. На вторые входы элементов И 27 и 28 поступают СИ, соответствующие моменту смены значений импульсов посередине биимпульсного сигнала. В этом случае на выходе триггера 29 формируется принимаемая информация в двоичном виде.

Выделение из формируемой на выходе генератора 4 тактовых импульсов последовательности СИ только тех СИ, которые соответствуют середине битового интервала, осуществляется с помощью регистра 1 сдвига, дешифратора

2, формирователя 3 импульсов и делителя 5 частоты на два. В данном случае используется такое свойство бииспульсного сигнала, как обязательное наличие при смене значений передаваемых символов комбинаций импульсов

00 или 11. В моменты смены значений

1406809 символов отсутствуют импульсы дифференцирования, формируемые в начале битового интервала, а осуществляется выделение только импульса дифферен5 цирования, формируемого посередине биимпульсного сигнала. Принимаемые данные записываются в регистр 1 сдвига. С помощью дешифратора 2 осуществляется вьщеление комбинации вида 11 или 00. По сигналу с его выхода формирователь 3 импульсов формирует импульс, который поступает на вход делителя 5. Если поступающий сигнал совпадает с импульсом на выходе дели- 15 теля 5 (на вход решающего блока 6 поступают необходимые СИ), т.е. имеет место синфазная работа, то изменение работы делителя 5 не происходит. В противном случае осуществляется вставка поступающего импульса в исходную последовательность СИ на входе делителя 5. Это приводит к смещению результирующей последовательности на половину периода (из- 25 меняется фаза).

Возникновение ошибки в принимаемом. сообщении за счет ложного возникновения пары импульсов 11 или 00, а также за счет пропуска СИ может при- 30 вести к нарушению .синфазности поступления СИ на решающий блок 6 (это имеет .место и в начальный момент функционирования приемника). Нарушение синфазности поступления СИ при-. водит к нарушению правильной работы

35 решающего блока 6. В этом случае имеет место обратная работа устройства, при которой принимаемый единичный символ фиксируется как нулевой и наоборот. Это возникает за счет смещения времени анализа принимаемых посылок на половину периода. Восстановление правильной работы приемника происходит только после выделения . 45 в принимаемой последовательности момента смены значений символов. Поэтому на выходе приемника при воздействии ошибки может появиться групповая ошибка, длительность которой зависит от момента выделения смены

50 значений символов в принимаемых данных. Обнаружение и исправление ошибок к малой кратности (одно-, двухкратных) осуществляются с помощью известных помехоустойчивых кодов (циклических, Хэмминга и т.д.), которые обеспечивают достижение требуемых вероятностных характеристик работы устройства, однако появление групповой ошибки в значительной мере повышает вероятность появления необнаруженной ошибки, а также снижает эффективность исправляющих ошибки кодов. Это приводит к снижению верности передаваемой информации.

Для исключения эффекта размножения ошибок в устройстве используются регистры 10-12 сдвига, два триггера 15 и 16, элементы И 7-9, инверторы 13 и 14 и элемент ИЛИ 17. Коррекция групповых ошибок осуществляется следующим образом. Двоичная информация с выхода решающего блока 6 поступает на вход регистра 10 сдвига, где осуществляется ее запоминание. Сигнал ошибки с выхода генератора 4 тактовых импульсов поступает на вход регистра

12 сдвига. Осуществляется запоминание момента появления ошибки (возможное начало групповой ошибки). В том случае, когда после выделения момента смены значений в принимаемой последовательности символов сигнал на выходе формирователя 3 импульсов не совпадает с сигналом на выходе делителя 3 (т.е. в результате воздействия ошибки произошло нарушение синфазности поступления СИ на вход решающего блока 6 (имеет место групповая ошибка), на выходе элемента И 7 формируется сигнал, который записывается в регистр 11 сдвига (запоминается момент восстановления синфаэной работы устройства или момент окончания групповой ошибки), и происходит установка в единичное состояние триггера 15, единичным сигналом с прямого выхода которого разрешается установка в единичное состояние триггера 16.

В этом случае по сигналу ошибки (начало групповой ошибки), поступающему с выхода регистра 12 сдвига, осуществляется его установка в единичное состояние. В результате происходит инвертирование выдаваемой потребителю информации (с помощью инвертора

13, элемента И 9 и элемента ИЛИ 17).

По сигналу восстановления синфазной работы, поступакицему с выхода регистра 11 сдвига, осуществляется установка в нулевое состояние триггера 15 и 16, в результате чего с этого момента информация потребителю поступает в неизменном виде.

В том случае, когда сигналы на выходах делителя 5 и формирователя 3

1406809 импульсов совпадают (т. е. ошибка не привела к появлению групповой ошибки), укаэанная группа элементов не оказывает влияния на работоспособность приемника.

5 формулаизобретения

1. Устройство для приема биим- 10 пульсных сигналов по авт. св.

11019656, отличающееся тем, что, с целью повышения достоверности приема путем уменьшения вероятности появления групповой ошибки, в него введены три регистра сдвига, 4 два инвертора, два триггера, три элемента И и элемент ИЛИ, причем выход формирователя импульсов соединен с первым входом первого элемента И, 20 выход которого соединен с первыми входами второго регистра сдвига и первого триггера, выход которого соединен с первым входом второго триггера, второй. и третий входы которого 25 соединены соответственно с выходами второго и третьего регистров сдвига, второй выход генератора тактовых импульсов соединен с первым входом третьего регистра сдвига, выход решающего блока соединен с первым входом четвертого регистра сдвига, выход делителя частоты соединен с вторыми входами второго, третьего и четвертого регистров сдвига и через первый инвертор с вторым входом первого элемента И, выход второго регистра сдвига соединен с вторым входом первого триггера, прямой и инверсный выходы второго триггера соединены с первыми 40 входами второго и третьего элементов

И, выход четвертого регистра сдвига соединен с вторым входом третьего элемента И и через второй инвертор с вторым входом второго элемента И, выходы второго и третьего элементов

И соединены с входами элемента ИЛИ.

2. Устройство по и. 1, о т л ич а ю ar, е е с я тем, что генератор тактовых импульсов состоит из двух блоков задержки, двух дифференцирующих блоков, двух элементов ИЛИ, инвертора и элемента И, причем входы первых блока задержки и дифференцирующего блока являются входом генератора тактовых импульсов, выход первого дифференцирующего блока соединен с первым .входом первого элемента ИЛИ, выход первого блока задержки через второй дифференцирующий блок соединен с вторым входом первого элемента ИЛИ, выход которого соединен с первым входом. второго элемента ИЛИ и через второй блок задержки с вторым входом второго элемента ИЛИ, выход которого является первым выходом генератора тактовых импульсов и соединен с первым входом элемента И, выход которого является вторым выходом генератора тактовых импульсов, выход первого элемента ИЛИ через инвертор соединен .с вторым входом элемента И.

3. Устройство по и. 1, о т л и— ч а ю щ е е с я тем, что решающий блок состоит из дифференцирующего блока, двух элементов И и триггера, причем выходы дифференцирующего бло" ка соединены с первыми входами элементов И, вторые входы которых являются первым входом решающего блока, вторым входом и выходом которого являются соответственно вход дифференцирующего блока и выход триггера, входы которых соединены с выходами элементов И.

1406809

Фиг. 2

Редактор А.Orap

Заказ 3209/55

Производственно-полиграфическое предприятие, г. Ужгород, ytI. Проектная, 4

Бои

КО бо ко5

Составитель Н.Лазарева

Техред М.Дидык Корректор Г.Решетник

Тираж 660 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5