Устройство для тестового контроля процессора

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для тестового контроля исправности процессоров цифровых ЭВМ, имеющих встроенные средства аппаратного контроля. Цель изобретения - повьппение надежности контроля. Устройство для тестового контроля процессора содержит первую группу 1 элементов И и К регистров 2 передачи данных, К-1 схем 3 сравнения, К-1 элементов И 4, а и 2117 1111 элемент ИЛИ 5, вторую 6, третью 7, четвертую 8 и пятую 9 группы элементов И, блок 18 элементов задержки, элемент НЕ 10, элемент И-НЕ 11, первую 13, вторую 12 и третью 14 группы элементов ИЛИ, блок 15 управления режимами, блок 16 распределения команд , буферный регистр 17. Устройство в процессе рабочего функционирования ЭВМ позволяет запоминать необходимую информацию, а во время технического обслуживания на ее основе адекватно воссоздавать ситуации, в которых неисправности (сбои и отказы) процессора проявились в виде ошибок, обнаруженных аппаратным контролем. Устройство может использоваться для классификации неисправностей (сбой и отказ ), для повторения ошибочных ситуаций необходимое при локализации отказа инженерными методами число раз и для проверки качества восстановления (ремонта) процессора. 2 з.п. ф-лы. 4 ил. 1 табл. го гч м}} (1 in сл 4i о СХ) 4 00 00 fut I

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

09) (I 1) А1

ОПИСАНИЕ ИЗОБРЕТ

К А ВТОРСКОЬЮ СВИДЕТЕЛЬСТВУ бб

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

{ (21) 4075892/24-24 (22) 11.05.86 (46) 07.07.88. Бюл. Ф 25 (72) В.Г.Тоценко, Д.В.Ершов, П.Г.Митрев и Н ° М.Рець (53) 681.3(088.8) (56) Авторское свидетельство СССР

В 616630, кл. G 06 F 11/00, 1978.

Авторское свидетельство СССР

У 552608, кл. G 06 F 11/00, 1977. (54) УСТРОЙСТВО ДЛЯ ТЕСТОВОГО КОНТРОЛЯ ПРОЦЕССОРА (57) Изобретение относится к вычислительной технике и может быть использовано для тестового контроля исправности процессоров цифровых 3ВМ, имеющих встроенные средства аппаратного контроля. Цель изобретения — повышение надежности контроля. Устройство для тестового контроля процессора содержит первую группу 1 элементов И и К регистров 2 передачи данных, К-1 схем 3 сравнения, К-1 элементов И 4, бб Рбб/б7 элемент ИЛИ 5, вторую 6, третью 7, четвертую 8 и пятую 9 группы элементов И, блок 18 элементов задержки, элемент НЕ 10, элемент И-НЕ 11, первую 13, вторую 12 и третью 14 группы элементов ИЛИ, блок 15 управления режимами, блок 16 распределения команд, буферный регистр 17. Устройство в процессе рабочего функционирования

ЭВМ позволяет запоминать необходимую информацию, а во время технического обслуживания на ее основе адекватно воссоздавать ситуации, в которых неисправности (сбои и отказы) процессора проявились в виде ошибок, обнаруженных аппаратным контролем. Устройство может использоваться для классификации неисправностей (сбой и от" каз), для повторения ошибочных ситуаций необходимое при локализации отказа инженерными методами число раз и для проверки качества восстановления (ремонта) процессора. 2 s.ë. ф-лы. 4 ил. 1 табл.

1408438

Изобретение относится к вычислительной технике и может быть использовано для тестового контроля исправности процессоров цифровых 3ВМ, имеющих встроенные средства аппаратного контроля правильности их функционирования.

Целью изобретения является повышение достоверности контроля. 10

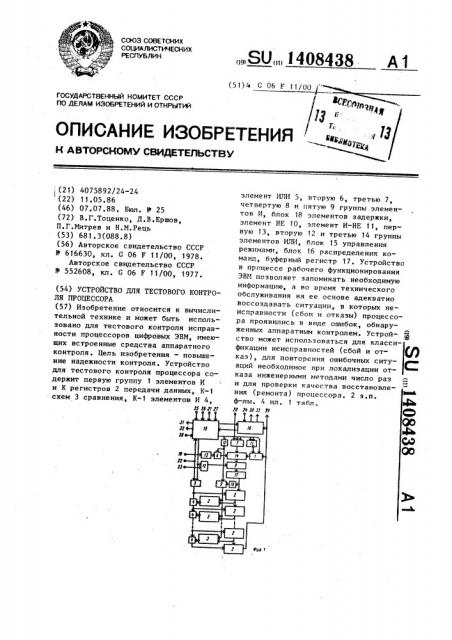

На фиг.1 приведены структурная схема устройства для тестового контроля процессора на фиг.2 — структурная схема блока управления режимами; на фиг.3 — структурная схема блока распределения команд, на фиг.4— структура информации о командах различных форматов, записываемых в буферный регистр.

Устройство для тестового контроля 20 процессора (фиг.1) содержит первую группу 1 элементов И, К регистров 2 передачи данных, К-1 схем 3 сравне. ния, К-1 элементов И 4, элемент ИЛИ

5, вторую 6, третью 7, четвертую 8 25 и пятую 9 группы элементов И, элемент

НЕ 10, х элемент И-НЕ 11, вторую 12, первую 13 и третью 14 группы элементов ИЛИ, блок 15 управления режимами, блок 16. распределения команд, буфер- 30 ный регистр 17, блок 18 элементов задержки, вход 19 устройства для подключения к выходной информационной шине контролируемого процессора, вход

20 тестовой информации устройства

35 вход 21 задания количества повторов таста устройства, вход 22 устройства для подключения к выходу конца команды контролируемого процессора, вход 23 устройства для переключения к вы40 ходу операций контролируемого процессора, вход 24 устройства для подключения к выходу синхронизации контролируемого процессора, вход 25 задания режима устройства, вход 26 пуска уст-45 ройства, вход 27 устройства для подключения к выходу сигнала аппаратного контроля контролируемого процессора, вход 28 готовности устройства, информационный выход 29 устройства, выход

30 устройства для подключения к вход50 ной информационной шине контролируемого процесса, выход 31 блокировки и тактовый выход 32 устройства, выход

33 устройства для подключения к входу разрешения контролируемого процессора.

Блок 15 управления режимами (фиг.2) содержит первый 34 и второй 35 счетчики, первый 36, второй 37, третий 38 и четвертый 39 элементы ИЛИ, первый

40, второй 41, третий 42, четвертый

43, пятый 44, шестой 45, седьмой 46, восьмой 47, девятый 48 и десятый 49 элементы И, первый 50, второй 51, третий 52 и четвертый 53 элементы НЕ, элемент 54 задержки и регистр 55.

Блок 16 распределения команд (фиг.3) содержит первый 56 и второй

57 дешифраторы, первый 58 и второй 59 элементы ИЛИ, первый 60, второй 61, третий 62 и четвертый 63 элементы И, первую 64 и вторую 65 группы элементов И, элемент НЕ 66, сумматор 67, первую 68, вторую 69, третью 70 четвертую 71 и пятую 72 группы элементов

ИЛИ, группу элементов 73 задержки и счетчик 74.

Устройство работает в одном из двух режимов: в режиме накопления тестов с выдачей накопительной информации на внешнее запоминающее устройство (ВЗУ) по сигналу ошибки от средств аппаратного контроля (АК) процессора и в режиме приема информации с ВЗУ и запуска тестов.

Режим накопления и выдачи тестов устанавливается путем подачи нулевого сигнала на вход 25 устройства (фиг.1). Запуск устройства осуществляется подачей едкничиого импульса на вход 26 устройства. Этот импульс через вход запуска блока 15 управления режимами (фиг.2),.поступает на вход сброса в ноль счетчика 35 и одновременно через элемент И 40 на вход сброса в ноль счетчика 34, устанавливая их в нулевые состояния. Нулевой сигнал с входа 25 устройства через вход задания режима блока 15 управления режимами запрещает прохож" дение единичных сигналов через элементы И 41 и 42 и поступает на вход элемента НЕ 51, единичный сигнал с выхода которого разрешает прохождение импульса запуска через элемент

И 40. Так как счетчик 34 устанавллвается в нулевое состояние, то на выходе элемента ИЛИ 37 устанавливается нулевое значение сигнала.

Этот сигнал, ссответствующий этапу накопления информации тестового набора, через выход режима блока 15 управления режимами поступает на вход элементов И группы 1 (фиг.1), запрещая прохождение через них сигналов на входы элементов ИЛИ группы 14, и з

14084 поступает на вход элемента HF. 10, единичный сигнал с выхода которого разрешает прохождение сигналов через элементы И групп 6 и 9. Нулевой сиг5 нал входа 25 устройства через вход задания режима и выход режима блока

15 управления режима поступает на вход элементов И группы 7, запрещая поступление информации с информацион- 1О ного входа 20 устройства на входы элементов ИЛИ группы 14. Таким образом, на этапе накопления тестовых наборов в первом режиме работы устрой. ства информация в регистр 17 поступа- 15 ет через элементы ИЛИ группы 13, элементы И группы 6, элементы ИЛИ группы . 14 и элементы И группы 8 информационного входа 19 устройства, подключенного к входам регистров процессора, gg в которые принимается информация (команды, адреса, операнда) по соответствующим микрооперациям. Сигналы данных микроопераций процессора поступают через вход 23 устройства и через 26 элементы ИЛИ группы 12 на входы элементов И группы 8, разрешения прием информации в соответствующие группы разрядов регистра 17 (параллельно с приемом этой же информации на.соот- ЗО ветствующие регистры процессора, осуществляемым теми же микрооперациями).

Подключение входов 18 и 23 устройства к регистрам процессора и выходам микрооперцций блока микропрограммного управления процессора соответственно и соединение выходов элементов ИЛИ группы 12 и 13 с входами элементов И групп 8 и 6 соответственно осуществляются таким образом, чтобы в регис- 4О тре 17 информация о выполняемых процессором командах различного формата запоминалась в таком виде, как это показано на фиг.4 (рассмотрение осуществляется применительно к процесса- 4Б ру с системой команды ЕС ЭВМ). В зависимости от формата (RR, RX RS или

SS) команд и использования в них регистров различного типа (POH — регистров общего назначения, РПЗ вЂ” регистров с плавающей запятой) в одних и тех же группах разрядов регистра 17 может запоминаться различная информация. На фиг.4 использованы следующие обозначения: ССП вЂ” слово состояния программы; КК вЂ” код команды, эб

ОП1, ОП2 — первый и второй операнды;

— значение базового адреса операнда, Х вЂ” значение индекса.

Накопленная в процессе выполнения команды информация из регистра 17 по сигналу окончания выполнения команды, поступающему иэ процессора на вход 22 устройства и проходящему через элемент ИЛИ 5 на вход разрешения приема информации первого регистра 2 передачи данных, передается в этот регистр.

Одновременно этот сигнал поступает на вход первого элемента И 4.

Если код операции в коде команды на регистре 17 поступающий через элементы задержки блока 18 и через элементы И группы 9 на первые входы схем 3 сравнения, не равен коду операции в коде команды на первом регистре 2 передачи данных, поступающему на второй вход первой схемы 3 сравнения, то на выходе этой схемы появляется единичный сигнал несравнения кодов операции, который разрешает прохождение единичного сигнала на выход первого элемента И 4, откуда он поступает на вход разрешения приема информации второго регистра 2 передачи данных, по которому в него записывается предыдущее значение информации первого регистра 2 передачи данных.

Если код операции в коде команды на втором регистре 2 передачи данных не равен коду операции в коде команды на регистре 17, то на выходе второй схемы 3 сравнения удерживается единичный потенциал, разрешающий дальнейшее распространение единичного сигнала через элементы И 4 до тех пор, пока оно не будет прекращено нулевым сигналом сравнения кодов операции с выхода одной из схем сравнения.

Регистры 2 передачи данных реализованы на двухступенчатых триггерах, прием значений в которые осуществляется по переднему фронту синхроимпульса, а перепись этих значений во вторую ступень и появление их на выходах триггеров — по заднему фронту синхроимпульса. Элементы задержки блока 18 необходимы для того, чтобы код операции, выполненной процессором команды, удерживался на входах схем

3 сравнения до завершения процесса распространения единичного импульса через все элементы И 4. Таким образом, регистры 2 передачи данных в совокупности со схемами 3 сравнения и элементами И 4 образуют регистровый стек, в котором по сигналу сдвига осуществляется последовательная пере50

5 14084 дача информации от предыдущего регистра к последующему, но только до того регистра 2 передачи данных, в котором хранится информация о команде с ко5 дом операции, совпадающим с кодом операции в регистре 17. Такой стек, содержащий К регистров 2 передачи дан данных, где К вЂ” количество различных кодов операций в системе команд процессора, позволяет запоминать но одному экземпляру (последней реализации) команды каждого типа,(каждого кода операции с упорядочением их по времени выполнения процессором), самая ранняя команда находится в К-м, последняя выполненная процессором команда — в первом регистре 2 передачи данных.

Устройство, работая в первом режи- 20 ме, постоянно обновляет информацию в регистрах 2 передачи данных до обнаружения ошибки средствами АК процессора и поступления соответствующего единичного сигнала на вход 27 устрой- 25 ства. Этот сигнал через вход ошибки блока 15 управления режимами (фиг.2) и через элемент И 43, открытый единичным сигналом с выхода элемента

НЕ 51, и элемент ИЛИ Зб поступает на вход начальной установки первого счетчика 34, устанавливая на нем значение К (переход к этапу выдачи теста на ВЗУ в первом режиме работы устройства). При этом на выходе элемен35 та ИЛИ 37 появляется единичный сигнал, который через элемент И 44 и выход блокировки блока 15 управления режимами поступает на вход 31 устройства, указывая режим записи информа- 40 ции для ВЗУ и блокируя работу процессора до окончания выдачи информации на ВЗУ.

Единичный сигнал с выхода элемента ИЛИ 37 через выход режима блока 15 4 управления режимами поступает на вход элемента НЕ 10 и третьи входы элементов И групйы 1. Нулевой сигнал с выхода элемента НЕ 10 запрещает прохождение информации через элементы И. групп 6 и 9. Нулевой сигнал с входа режима и единичный сигнал с выхода элемента HE 53 блока 15 управления режимами через выход режима этого блока поступают на входы элемента

И-НЕ 11. Единичный сигнал с выхода элемента И-НЕ 11 поступает на входы элементов И группы 1, вследствие чего на входы элементов И группы 8 через

38 6 элементы ИЛИ группы 14 и элементы И группы 1 поступает информация с выхода К-ro регистра 2 передачи данных, что соответствует этапу выдачи и циклической передачи информации в регистрах 2 передачи данных и регистре 17.

Единичный сигнал с выхода элемента ИЛИ 37 поступает на вход элемента

И 45, на второй вход которого поступает единичный сигнал с выхода элемента НЕ 53. При готовности ВЗУ к работе на вход 28 устройства подается единичный сигнал, который, проходя через вход готовности блока 15 управления режимами и через элементы И 45 и ИЛИ 39, вычитает единицу из значения на счетчике 34 и через элемент И

49 и тактовый выход блока 15 управления режимами поступает на выход 32 устройства. Единичный сигнал на выходе 32 устройства воспринимается ВЗУ как сигнал начала работы (в данном случае записи). ВЗУ записывает информацию, принимаемую с выхода К-го регистра 2 передачи данных через информационный выход 29 устройства. Одновременно единичный сигнал с выхода элемента ИЛИ 39 через выход сдвига блока 15 управления режимами поступает на входы элементов ИЛИ 5 и группы 12. Закончив запись информации, ВЗУ снимает и вновь выставляет единичный сигнал готовнссти на вход 28 устройства, в результате чего осуществляется циклический сдвиг информации в регистрах 2 передачи данных и регистре 17. Затем вновь по сигналу готовности ВЗУ из значения счетчика

34 вычитается единица. и т.д. до установки счетчика в нулевое состояние.

Наличие схем 3 сравнения и элементов

И 4 не препятствует виклической передаче информации, так как нулевым сигналом с выхода элемента НЕ 10 выходы элементов И группы 9 удерживаются в нулевом состоянии, что соответствует нулевому (отсутствующему в системе команд) току операции.

Когда значение счетчика 34 становится равным нулю, на выходе элемента ИЛИ 37 появляется нулевой сигнал, что соответствует переходу вновь к этапу накопления тестов первого режима работы устройства„ при этом снимается сигнал блокировки работы процессора (выход 31 устройства) и запрещается прохождение единичных сигналов готовности ВЗУ через элемент И 45.

38 8

7 14084

Распространение единичного сигнала с выхода элемента НЕ 52 на вход счетчика 35 через элемент И 42 блокируется нулевым сигналом с входа задания режима входа 25 устройства. Регистры

2 передачи данных и регистр 17 вновь содержат ту же информацию, что и в момент обнаружения ошибки средствами

AK процессора. Запрещается прием информации через элементы И группы 1 и разрешается прием информации в регистр 17 через элементы И группы 6.

При снятии сигнала AK и пуске процес/ сора запоминание информации в регист- 16 ровом стеке продолжается до следующего обнаружения ошибки средствами

АК процессора. Затем вновь осуществляется выдача накопленной информации на ВЗУ и т.д. 20

B результате работы устройства в первом режиме в память ВЗУ записывается некоторое количество тестовых наборов, которые впоследствии могут быть приняты в ВЗУ, в регистры 2 пе- 26 редачи данных устройства и регистр 17 и выполнены во втором режиме работы устройства.

Режим приема и запуска тестов.устанавливается путем подачи единичного сигнала на вход 25 устройства.

Процессор должен быть переведен в режим покомандной работы и останова JI0 сигналу AK. На регистр 55 через вход

21 устройства заносится число реали35 заций каждого тестового набора. Запуск устройства осуществляется подачей единичного импульса на вход 26 устройства. По этому импульсу счетчик 35 устанавливается в ноль, а счетчик 34 единичным импульсом, про" ходящим через элементы И 41 и ИЛИ 36, устанавливается в состояние К. Значение ноль на счетчике 35 и отличие от нуля значение на счетчике 34 при вто- 4 ром режиме работы устройства является . признаком этапа приема тестового набора в ВЗУ на регистры 2 передачи данных и регистр 17. чения счетчика 35 единицу, а затем, пройдя через элемент И 46, разрешает прием на счетчик 35 значения с региотра 55. На выходе элемента ИЛИ 38 появляется единичный сигнал, а на выходе элемента НЕ 53 — нулевой, заТак как на выходе элемента НЕ 51 В0 удерживается нулевое значение сигнала, то на выходе элемента И 44 и, следовательно, на выходе 31 устройства также, удерживается нулевой сигнал, означающий отсутствие блокировки 6В работы процессора и режим чтения информации с ВЗУ.

Единичный сигнал с выхода элемента ИЛИ 37 через выход режима блока 15 управления режимамй поступает на вход элемента НЕ 10, нулевой сигнал с выхода которого блокирует прохождение сигналов через элементы И групп 6 и

9. Единичные сигналы с выхода элемента НЕ 53 н с входа задания режима блока 15 задания режима через выход режима этого блока поступают на входы элемента И 7, разрешая прохождение информации с информационного входа 20 на входы элементов ИЛИ группы 14. Эти же сигналы поступают на входы элемента И-НЕ 11, нулевой сигнал на выходе которого блокирует прохождение информации через элементы И группы 1.

Единичный сигнал с выхода элемента ИЛИ 37 поступает на вход элемента

И 45, разрешая прохождение сигнала готовности ВЗУ с входа 28 устройства через вход готовности блока 15 управления режимами, элементы И 45 и ИЛИ

39. Единичный сигнал с выхода элемента ИЛИ 39 вычитает единицу из содержимого счетчика 34 и проходит через элемент И 49 и тактовый вьжод блока

15 управления режимами на второй управляющий выход 32 устройства, разрешая начать работу ВЗУ. Одновременно сигнал проходит с выхода элемента

ИЛИ 39 через выход сдвига блока 15 управления режимами и элементы ИЛИ групп 12 и элемент ИЛИ 5 (фиг. 1) на входы элементов И группы 8 и входы разрешения приема в регистры 2 передачи данных, разрешая прием в регистровый стек информации с ВЗУ через информационный вход 20 устройства.

Далее устройство работает аналогично этапу выдачи тестового набора на ВЗУ с той лишь разницей, что производится не запись, а чтение информации с ВЗУ и циклическая передача информации в регистрах 2 передачи данных и регистре 17 блокирована.

Этап приема завершается, когда на счетчике 34 устанавливается нулевое значение. При этом на выходе элемента ИЛИ 37 появляется нулевой сигнал, закрывающий элемент И 45 и вызывающий появление единичного сигнала на выходе элемента НЕ 52, который, пройдя через элемент И 42, вычитает из эна9

14084 прещающий прохождение сигналов через элементы И 45, 46, и 49. Единичный сигнал с выхода элемента И 42, проходя через элемент ИЛИ 36 вновь устаФ

5 навливает на счетчике 34 значение К.

Ненулевые значения на счетчиках 34 и 35 являются признаком этапа запуска тестов второго режима работы устройства. 10

Единичный сигнал с выхода элемента ИЛИ 38 разрешает прохождение сигналов через элементы И 47 и 48, Единичный сигнал с тактового выхода блока 16 распределения команд через так- 15 товый вход блока 15 управления режимами, элемент И 48 и элемент ИЛИ 39 поступает на вычитающий,вход счетчика 34, вычитая из его значения единицу, и через элемент И 47 проходит на выход записи блока 15 управления режимами (элемент И 47 открыт сигналом, поступающим с первого управляющего входа 22 устройства через вход окончания команды блока 15 управле- 25 ния режимами). Единичный сигнал с выхода записи блока 15 управления режимами через вход записи блока 16 распределения команд поступает на вход разрешения приема информации счетчика 74 (фиг.3). С выхода К-го регистра 2 передачи данных через вход данных блока 16 на элемент ИЛИ 59 поступает код операции, на дешифратор

57 — первые два разряда кода опера35 ции, определяющие формат команды, на элемент И 62 — нулевой и второй разряды кода операции, на элемент И 63разряды 0-6 кода операции, на элемент

И 64 — вся информация из К-го регист40 ра 2 передачи данных. Если код операции отличен от нуля, то на выходе элемента ИЛИ 59 вырабатывается единичный сигнал, разрешающий прохождение информации через элементы И 60 и 65.

Единичный сигнал с соответствующе.. го выхода дешифратора 57, проходя через элемент И 65, по еденичному сигналу на входе разрешения приема информации счетчика 74 устранавливает

его в определенное состояние: если значения разрядов 0 и 1 кода операции равны 00 (формат RR), то счетчик 74 устанавливается в состояние "2", если — 01.(формат RX), то - в состоя55 ние "8", если " 10 (формат RS) то— в состояние "16", если 11 (формат SS), то — в состояние "32". Если код опе38 10 рации нулевой и элемент И 65 закрыт, то счетчик 74 устанавливается в состояние "0". На выходах элементов И 62 и 63 в зависимости о- кода операции устанавливаются значения 00, 10 или

01, однозначно определяемые типом используемых в команде регистров: общего назначения, с плавающей запятой, управляющих регистров процессора соответственно.

Признаком использования регистров с плавающей запятой является наличие нуля в нулевом и единицы во втором разрядах кода операции. Признаком использования управляющих регистров является значение 1011011 в разрядах

0-6 кода операции. На входы элемента

И 62 поступают значения 0-10 разряда кода операции в инвертированном виде (с инверсного выхода соответствующего разряда К-ro регистра 2 передачи данных) и второго разряда кода операции в прямом виде. На входы элемента И

63 поступают инвертированные значения первого и четвертого разрядов кода операции и "прямые" значения разрядов

О, 2, 3 5 и 6 кода операции. В соответствии с кодом на счетчике 74 возбуждается определенный выход дешифратора 56. Выходы дешифратора 56 с номерами 1, 6, 15, 22 и 42 соединены с входами элемента ИЛИ 58, поэтому при установке одного из значений О, 2, 8, 16 или 32 на счетчике 34 на выходе элемента ИЛИ 58 появляется нулевой сигнал, который, инвертируясь элементом НЕ 66, разрешает прохождение на счетный вход счетчика 74 через элемент И 61 и импульсный вход блока 16 импульсов с входа 24 устройства, подключенного к выходу генератора импульсов процессора. Счетчик 74 считает до тех пор, пока на нем не установится одно из значений 1, 6, 15, 22 или 42, что соответствует появле- нию единичного сигнала на выходе элемента ИЛИ 58. Алгоритмы рассылки команд представлены в таблице.

Выходы дешифратора 56, элементов

ИЛИ 68 и элементов И 64 скоммутированы таким образом, что импульсы, появляющиеся на выходах дешифратора 56, разрешают выполнение пяти групп действий (см. таблицу) по рассылке информации команд в местную память, оперативную память и на регистр слова состояния программы процессора. OneI l 14084 ранцы и коды команд в оперативную память передаются с выходов элементов

И группы 64 через элементы ИЛИ группы 70. Адреса по которым осущест1

5 вляется запись этих операндов в ОП, выдаются с выхода накапливающего сумматора 67. Адреса (номера) регистров местной памяти и записываемые в них значения передаются через элементы

ИЛИ групп 72 и 71 соответственно.

ССП передается в процессор непосредственно с выходов элементов И группы 64. Стробирукнцие сигналы записи информации в ОП, местную память и на регистр слова состояния программы выдаются с выходов соответствующих элементов ИЛИ группы 68. Эти сигналы вместе с рассылаемой информацией через выход данных блока 16 поступают на второй информационный выход 30 устройства, который подключается к соответствукяцим регистрам и схемам процессора. Элементы задержки группы

73 введены для того, чтобы при снятии 25 единичного сигнала с одного выхода дешифратора 56 и появлении единицы на следующем его выходе, воспринимаемой как сигнал записи в ОП, ИП или

ССП, выданная в предыдущий момент времени информация некоторое время удерживалась на.выходах элементов И группы 64. Этого времени должно быть достаточно для записи информации с второго информационного выхода 30 устройства в ОП, MI или ССП.

Таким образом, в зависимости от формата команды устройство по одному из пяти алгоритмов, приведенных в 40 таблице, рассылает соответствующую информацию в регистры и ячейки памяти процессора, которые используются при выполнении этой команды. В последнем такте рассылки информации на счетчи- 45 ке 74 устанавливается одно из значений 1, 6, 15, 22 или 42. При этом на . выходе элемента ИЛИ 58 появляется единичный сигнал, блокирующий элемент

НЕ 66 поступление импульсов с гене- 50 ратора на вход счетчика 74 через элемент И 61. Этот же сигнал выдается через тактовый выход блока 16 и тактовый вход, блока 15 на вход элемента

И 48. Одновременно этот сигнал, если команда имеет допустимый (отличный от нуля) код операции, выдается через элемент И 60 и выход разрешения счета блока 16 на выход 33 устройства, (38 12 разрешая процессору выполнить одну (разосланную) команду.

Единичный сигнал, проходя через элементы И 48 и ИЛИ 39, вычитает единицу из счетчика 34 (фиг.2) и поступает на выход сдвига блока 15 управления режимами и на вход элемента

И 47. Процессор, закончив выполнение команды, выставляет единицу на первом управляющем входе 22 устройства, откуда она через вход окончания команды блока 15 управления режимами, элемент И 47 и выход записи этого же блока поступает на вход записи блока

16 распределения команд, что означает переход к рассылке информации следующей команды. Сдвиг информации в регистрах 2 передачи данных осуществляется по заднему фронту единичного импульса на выходе элемента И 39.

Рассыпка и выполнение команд продолжается либо до появления сигнала

AK процессора, либо до установки счетчика 34 в ноль. В первом случае процессор останавливается, не закончив выполнения команды, и блокирует работу устройства нулевым сигналом на первом управляющем входе 22 устройства. При установке счетчика 34 в ноль .на выходе элемента НЕ 52 появляется единичный сигнал, который осуществляет вычитание единицы из значения счетчика 35 и установку на счетчике 34 значения К. Если значение на счетчике 35 не равно нулю, то вновь начинается рассыпка и выполнение команд. Если счетчик 35 устанавливается в ноль, то происходит переход к этапу приема с ВЗУ следующего тесТового набора. Элемент 54 задержки использован для того, чтобы при установке счетчика 34 в состоянии К, а счетчика

35 в 0 счетчик 34 успел перейти в состояние К и на выход элемента НЕ

52, а следовательно, и на вход другого элемента И 46 приходит единичный сигнал с выхода элемента НЕ 53. Это устраняет возможность самопроизвольной установки на счетчик 35 значения с регистра 55.

Прием очередного тестового набора с ВЗУ, покомандная рассылка и его выполнение, заданное (на регистре 55) число pas, продолжается либо до появления сигнала АК в процессоре, либо до перехода ВЗУ в состояние неготовности, 10

20

30

l3 14О

Таким образом, в процессе рабочего функционирования ЭВМ, когда длительные перерывы, связанные с анализом причин ошибок в работе процессора р обнаруженных средствами АК, недопустимы, устройство позволяет запомнить информацию о ходе вычислительного процесса, достаточную для воссоздания условий, в которых неисправности (сбои или отказы) процессора проявляются в виде ошибок, и тем самым осуществить как бы отложенный на удобное время анализ причин этих ошибок. Повторяя зафиксированные ситуации заданное число раз, определяется, была ли вызвана ошибка случайным сбоем или устойчивым отказом некоторых элементов процессора ° В последнем случае устройство позволяет повторять ситуацию необходимое для локализации отказа (инженерными методами) число раз. Эти же тесты могут служить эффективным средством проверки качества восстановления (ремонта) процессора.

Программные тесты получаются с помощью устройства автоматически. Получаемый набор тестов настроен на обнаружение именно тех неисправностей, которые имеют место в конкретном экземпляре процессора в конкретных условиях его применения и которые мешают выполнению конкретного потока задач, решаемых на данной ЭВМ.

Для быстродействующих процессоров, в которых реализовано совмещение выполнения различных этапов нескольких последовательных..к6манд, регистр 17 устройства должен состоять из нескольких регистров, в которых накапливается информация о командах, находящихся на различных уровнях их выполнения. Перепись информации из одного регистра в другой в этом случае должна осуществляться по сигналу перехода к следующему уровню выполнения команд.

Формула изобретения

1. Устройство для тестового контроля процессора, содержащее первую группу элементов И и К регистров передачи данных, где К вЂ” количество кодов операций в системе команд контролырреыого процессора, выход х-го егистра передачи данных (i = 1, (К-1) ) соединен с информационным входом

8438 14 (i+1)-го регистра передачи данных, выходы К-го регистра передачи данных соединены с первыми входами элементов

И первой группы, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, устройство содержит с первой по (К-1)-ю схемы сравнения, с первого по (К-1}-й элементы И, элемент ИЛИ, с второй по пятую группы элементов И, блок элементов задержки, элемент HE элемент

И-НЕ, с первой по третью группы элементов ИЛИ, блок управления режимами, блок распределения команд и буферный регистр, выход которого соединен с информационным входом первого регистра передачи данных и с входом блока элементов задержки, входы элементов

ИЛИ первой группы образуют вход устройства для подключения к выходной информационной шине контролируемого процессора, выходы элементов ИЛИ первой группы соединены с первыми входами элементов И второй группы, первый разряд выхода задания режима блока управления режимами соединен с. входом элемента НЕ и с вторыми входами элементов И первой группы, второй разряд выхода задания режима, блока управления режимами соединен с первыми входами элементов И третьей группы и с первым входом элемента

И-НЕ, третий разряд выхода задания режима блока управления режимами сое35 динен с вторыми входами элементов И третьей группы и с вторым входом элемента И-НЕ, выход которого соединен с третьими входами элементов И первой

40 группы, первые входы элементов ИЛИ второй группы образуют вход устройства для подключения к выходу операций контролируемого процессора, выходы элементов ИЛИ второй группы соединены с первыми входами элементов И

45 четвертой группы, выходы которых образуют информационный вход буферного регистра, выходы элементов И третьей группы соединены с первыми входами элементов ИЛИ третьей группы, выходы

50. которых соединены с вторыми входами элементов И четвертой группы, первые входы элементов И пятой группы образуют выход блока элементов задержки, выход элемента НЕ соединен с вторыми входами элементов И второй и пятой групп, первые группы входов с первой по (К-1)-ю схем сравнения соединены с выхолами элементов И пятой группы, 14084 вторая груттнв вколов 1-й схемы сравнения соединена с выходами i — rn ретистра передачи данных, выход э.-й схемьi сравнения соединен с первым входом

i — го элемента И, выходы с первого по

5 (К-2)-й элементов И соединены с вторыми входами соответственно с второго по (К вЂ” 1)-й элементов И, выход i-го элемента И соединен с входом разреше- 10 ния (i+1)-ro регистра передачи данных, выход элемента ИЛИ соединен с вторым нходом первого элемента И и с входом разрешения первого регистра передачи данных, вход признака окончания команды блока управления режимами и первый вход элемента ИЛИ подключены к входу устройства для подключения к выходу конца команды контролируемого процессора, выход сдвига 2О блока управления режимами соединен с вторым входом элемента ИЛИ и с вторыми входами элементов ИЛИ второй группы, вход готовности устройства подключен к входу готовности блока уп- 25 равления режимами, тактовый выход и выход блокировки блока управления режимами являются соответственно тактовым выходом и выходом блокировки устройства, входы задания режима, пуска и кода количества повторов теста блока управления режимами являются соответственно входами задания режима, пуска и задания количества повторов теста устройства, вход признака ошибки блока управления режимами является входом устройства для подключения к выходу сигнала аппаратного контроля контролируемого процессора, третьи входы элементов И третьей 4О группы образуют вход тестовой информации устройства, выходы К-го регистра передачи данных образуют вход данных блока распределения команд и информационный выход устройства, синхровход 45 блока распределения: команд является входом устройства для подключения к выходу синхронизации контролируемого процессора, ныход данных и разрешающий выход блока распределения команд являются выходами устройства для подключения соответственно к входной информационной шине и к входу разрешения контролируемого процессора, выход признака записи блока управления режимами соединен с входом записи блока

55 распределения команд, тактовый выход которого соединен с тактовым входом блока управления режимами, выходы

18 16

-лемсвтон И нертэой группы соединены с вторыми входами лемеитон ИЛИ треThE .é группы, третьи входы которых со единевы с выходами .элементов И второй группы.

2. Устройство по п.1, о т л и ч аю ш е е с я тем, что блок управления режимами содержит первый и второй счетчики, с первого по четвертый элеметтты ИЛИ, с первого по десятый элементы И, с первого по четвертый элементы HE элемент задержки и регистр, информационный вход которого является входом кода количества повторов теста блока, выход первого элемента ИЛИ соединен с входом начальной установки перного счетчика, выходы которого соединены с входами второго элемента

ИЛИ, вьгход регистра соединен с информационным входом второго счетчика, вход пуска блока подключен к первым входам первого и второго элементов И, к входу сброса второго счетчика и через первый элемент HE к первому входу третьего элемента И, вход задания режима блока подключен к вторым входам второго и третьего элементов И, к входу второго элемента НЕ и является вторым разрядом выхода задания режима блока, выход второго элемента

НЕ соединен с вторым входом перного элемента И и с первыми входами четвертого и пятого элементов И, первый и второй входы первого элемента ИЛИ соединены соответственно с выходами второго и четвертого элементов И, выход второго элемента ИЛИ соединен с вторым входом пятого элемента И, через третий элемент НŠ— с третЬим входом третьего элемента И, с первым входом шестого элемента И и является первым разрядом выхода задания режима блока, второй вход четвертого элемента И является входом признака ошибки блока, выход пятого элемента И является выходом блокировки блока, выход третьего элемента И соединен с третьим входом первого элемента ИЛИ, с первым входом седьмого элемента И и с вычитающим входом второго счетчика, вход разрешения которого соединен с выходом седьмого элемента И, второй вход которого соединен с выходом элемента задержки, выходы второго счетчика соединены с входами третьего элемента ИЛИ, .ныход которого соединен с входом четвертого элемента НЕ и с первыми входами восьмого и девяНомер выхода дешифратора

Формат команды

Действия

Выдача номера регистра первого операнда (Р1) и значения первого операнда (ОПУ)

Запись в местную память (ИП), сброс сумматора

Выдача номера регистра второго о