Устройство для контроля качества дискретного канала связи

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи . Цель изобретения - сокращение времени контроля. Устр-во содержит анализатор 1 ошибочных комбинаций. блок 2 управления, элемент ИЛИ 3, ;счетчик 4 комбинаций, счетчик 5 ошибочных комбинаций, блок индикации (БИ) 6, регистр памяти 10, С целью сокращения времени контроля в устр-во введены БИ 7, два постоянных запоминающих блока 8, 9, регистр памяти 11, комбинационньй сумматор 12, счетчик 13повторных комбинаций, дешифратор 14повторных комбинаций.Если показания индикатора превьш1ают допустимые, то оператор может оперативно перейти на другую рабочую частоту передачи или приема или перейти на другой режим работы. При этом не тратится время на специальную проверку, диагностический контроль путем прерьшания рабочего режима (сеанса связи) и перехода в режим контроля, диагностики и обратно. 4 ил. i (Л

CO)03 СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) (51) 4 Н 04 1 11/08

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ Ф сощщ„

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMV СВИДЕТЕЛЬСТВУ %Щ д

Кои, (21) 4168967/24-09 (22) 29. 12. 86 (46) 07.07.88. Бюл. И 25 (72) Н. Ф. Логвиненко, В. И. Петрович, Е. А. Горбачев, В. Д. Русаков, С. Н. Абрамов, Ю. П. Сухоруков, А. П. Сорокин и В. П. Плотвинов (53) 621. 396. 664 (088. 8) (56) Авторское свидетельство СССР

1(849524, кл. Н 04 L 11/08, 1981.

Авторское свидетельство СССР

9 938421, кл. Н 04 L 11/08, 1982. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА

ДИСКРЕТНОГО КАНАЛА СВЯЗИ (57) Изобретение относится к электросвязи..Цель изобретения — сокращение времени контроля. Устр-во содержит анализатор 1 ошибочных комбинаций, блок 2 управления, элемент ИЛИ 3, счетчик 4 комбинаций, счетчик 5 ошибочных комбинаций, блок индикации (БИ) 6, регистр памяти 10, С целью сокращения времени контроля в устр-во введены БИ 7, два постоянных запоминающих блока 8, 9, регистр памяти 11 комбинационный сумматор 12, счетчик

13 повторных комбинаций, дешифратор

14 повторных комбинаций. Если показания индикатора превышают допустимые, то оператор может оперативно перейти на другую рабочую частоту передачи или приема ипи перейти на другой режим работы. При этом не тратится время на специальную проверку, диагностический контроль путем прерывания рабочего режима (сеанса связи) и перехода в режим контроля, диагностики и обратно. 4 ил.

1408538

Изобретение относится к электросвязи и может быть применено в системах передачи данных с решающей обратной связью.

Цель изобретения — сокращение времени контроля.

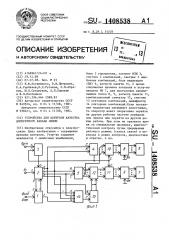

На фиг. 1 представлена структурная электрическая схема устройства для контроля качества дискретного канала связи; на фиг.2 — структурная электрическая схема анализатора ошибочных комбинаций; на фиг.3 — структурная электрическая схема блока управления; на фиг.4 — структурная электрическая схема дешифратора повторных комбинаций.

Устройство для контроля качества дискретного канала связи содержит анализатор 1 ошибочных комбинаций, 20 блок 2 управления, элемент ИЛИ 3, счетчик 4 комбинаций, счетчик 5 ошибочных комбинаций, первый 6 и второй

-7 блоки индикации, первый 8 и второй, 9 постоянные запоминающие блоки (ПЗБ),.5 первый 10 и второй 11 регистры памя" ти, комбинационный сумматор 12, счетчик 13 повторных комбинаций и дешифратор 14 повторных комбинаций.

Анализатор 1 представляет собой фактически известный декодер цифровой информации (фиг.2), состоящий, например, из регистра сдвига, образованного из D-триггеров 15 — 25, четырех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ (сумматоры по модулю два) 26 — 29, подключенных к соответствующим входам и первым выходам регистра сдвига, и дешифратора 30, подключенного своими входами к вторым выходам регистра сдвига. Для обнаружения ошибки может быть применен,. например, образующий полином 11 степени (Х + Х + Х + Х + 1).

Блок 2 управления содержит (фиг.3) следующие стандартные элементы: три элемента И 31-33, два D-триггера 34 и

35, счетчик 36, дешифратор 37, два элемента ИЛИ 38 и 39, два элемента

НЕ 40 и 41 и формирователь 42.

Дешифратор 14 содержит (фиг.4) следующие стандартные элементы: Dтриггер 43, элемент НЕ 44 и элемент

И-НЕ 45.

Устройство работает следующим образом, э5

После включения напряжения питания в блоке 2 (фиг.2) формирователь 42 вырабатывает сигнал обнуления (" Сброс" ), который подается внутри блока 2 через элемент ИЛИ 38 на установочный вход счетчика 36, через элемент НЕ 40 на установочный вход триггера 34, а через элемент ИЛИ 39 — на второй выход блока 2.

В результате все счетчики 4, 5 и

13 (фиг. 1) обнуляются.

По приходу сигнала "Пуск", синхронизированного с началом кодовой комбинации (т. е., сформированного вне предлагаемого устройства, в аппаратуре по окончании циклового фазирования при наличии команды "Пуск" ), через элемент ИЛИ 3 на третий вход блока

2 управления последний разрешает прохождение импульсов тактовой частоты, поступающих на второй вход блока 2 управления, с пятого своего выхода на второй вход анализатора 1 ошибочных комбинаций. В результате этого цифровая информация, поступающая на первый вход анализатора 1, подвергается поблочной обработке с целью выявления ошибочных блоков— (комбинаций), причем биты входной информации опережают фронты импульсов тактовой частоты. С первого выхода анализатора 1 на первый вход блока

2 выдается сигнал ошибки (логической единицы), если хотя бы одна ошибка содержится в комбинации, и записывается на триггере 35 блока 2 управления. С второго выхода анализатора 1 на дешифратор 14 выдается информационная кодовая последовательность, часть разрядов которой содержит служебные биты. 22-й разряд кодовой (35,24-разрядной) комбинации содержит информацию о повторении комбинации. Блок 2 управления с помощью содержащихся в нем счетчика 36 и дешифратора 37 (фиг.3) выделяет 22-й импульс и выдает его с четвертого выхода на третий вход дешифратора 14, под действием которого информация (признак) о наличии повторенной комбинации (бит в 22-м разряде) записывается и хранится в D-триггере 43 дешифратора 14 (фиг.4). При совпадении трех сигналов: признака повторной комбинации (третий вход дешифратора

14), отсутствии ошибки в комбинации (второй вход) и признака окончания комбинации (первый вход), дешифратор

14 формирует импульсный сигнал на вход счетчика 13.

l

С третьего выхода блока 2 управления на вход счетчика 4 комбинаций

1408538 выдаются импульсы, каждый из которых означает, что на устройство поступила очередная комбинация 35, 24-разрядного кода, где 35 означает полное число разрядов комбинации (блока), а 24 — число разрядов, отведенное для информации и служебных битов в том числе, а остальные 11 разрядов — проверочные биты. С второго выхода блока10

2 управления на вход счетчика 5 поступают импульсы, каждый из которых означает наличие хотя .бы одной ошибки в кодовой комбинации. После отсчета счетчиком 4, работающим в режиме сложения, количества импульсов, соответствующих 125 комбинациям, с его выхода на синхронизирующие входы записи первого 10 и второго 11 регистров формируется импульс. При этом по 20 переднему фронту импульса в первый регистр 10 записывается число ошибочных комбинаций, подсчитанное за цикл (период), равный по времени интервалу времени из 125 комбинаций (на соответствующей скорости приема-передачи дискретной информации).

Во второй регистр 11 по переднему фронту импульса записывается число, означающее сумму ошибочных комбинаций, подсчитанных счетчиком 5 и выданных на входы комбинационного сумматора 12, и повторных комбинаций, подсчитанных счетчиком 13, который принял их с дешифратора 14 и выдална вторые входы комбинационного сумматора 12. Этот же импульс, поступивший с выхода счетчика 4 через элемент

ИЛИ 3 на вход блока 2 управления, означает конец одного цикла измерения.

Код числа, записанный в первом регистре, выдается через ПЗБ 8 на первый блок 6 индикации, который отображает процент безошибочных комбинаций на приеме в режиме работы аппаратуры пе45 редачи данных с решающей обратной связью в процессе сеанса связи. Код числа, записанный во втором регистре

11, выдается через ПЗБ 9 на второй блок 7 индикации, который отображает процент безошибочных комбинаций, полученных на приеме, с учетом числа новых, формируемых на передаче, комбинаций, т.е. числа повторенных комбинаций в процессе сеанса связи.

Показания обоих блоков 6 и 7 ин55 дикации изменяются через интервалы времени передачи (приема) 125 комби. наций 35, 24-разрядного кода.

Первый блок 6 индикации отображает коэффициент потерь передачи информации в одном (обратном) канале, а второй блок 7 индикации †. в другом (прямом), причем показания второго всегда не превышают показаний первого и выражаются в процентах.

ПЗБ 8 и 9 кодируются таким образом, чтобы двоичный код (число комбинаций), поданный на каждый из блоков, преобразовывался в двоичный код, соответствующий коэффициенту потерь или скорости передачи цифровой информации, выраженных в процентах.

Например, если на вход ПЗБ поступает .двоичный код числа, находящегося в пределах от 0 до 5, то это означает, что блок индикаторов покажет:число О .

Если на входе ПЗБ двоичный код числа, находящегося в пределах от 18 до 29, то индикатор покажет число 20, а если на входе ПЗБ двоичный код числа, находящегося в интервале от 90 до

101, то индикатор покажет число 80%.

Таким образом, наблюдая за показаниями индикаторов, оператор в процессе сеанса связи может судить о коэффициенте потери скорости передачи цифровой информации в прямом и обратном каналах связи за счет переспросов ошибочных комбинаций 35, 24-разрядного кода в системе передачи данных с использованием режима обратной связи.

Если показания индикатора (или индикаторов) превышают допустимые (это означает, что из-за наличия помех принимается большой процент оши= бочных комбинаций и скорость передачи цифровой информации очень снизилась), то оператор может оперативно перейти на другую рабочую частоту передачи или приема или перейти на другой режим работы. При этом не тратится время на специальную проверку, диагностический контроль путем прерывания рабочего режима (сеанса связи) и перехода в режим контроля, диагностики и обратно.

Формула изобретения

Устройство для контроля качества дискретного канала связи, содержащее последовательно соединенные анализатор ошибочных комбинаций,.первый вход которого является информационным входом устройства, и блок управления, второй вход которого является такто I408538 вым входом устройства, элемент ИЛИ, выход которого подключен к третьему входу блока управления, первый выход которого подключен к установочным входам счетчика ошибочных комбинаций и счетчика комбинаций, выход которого подключен к первому входу элемента

ИЛИ, второй вход которого является ( пусковым входом устройства, а второй выход блока управления подключен к счетному входу счетчика ошибочных комбинаций, выходы которого подключены к установочным входам первого регистра памяти, и первый блок индикации, о т л и ч а ю щ е е с я тем, что, с целью сокращения времени контроля, введены последовательно соединенные дешифратор повторных комбинаций, счетчик повторных комбинаций, комбинационный сумматор, второй регистр памяти, первый постоянный запоминающий

;блок и второй блок индикации, второй

1 постоянный запоминающий блок, включенный между выходами первого регистра памяти и входами первого блока индикации, при этом выходы счетчика ошибочных комбинаций подключены к другим входам комбинационного сумматора, выход счетчика комбинаций подключен к синхронизирующим входам первого и второго регистров памяти, уста новочный вход счетчика повторных комбинаций соединен с первым выходом блока управления, второй, третий,и четвертый выходы которого подключены соответственно к первому, второму и третьему входам дешифратора повторных комбинаций, четвертый вход которого соединен с вторым выходом анализатора ошйбочных комбинаций, второй вход которого соединен с пятым выходом блока управления, третий выход которого подключен к счетному входу счет" чика комбинаций.

1408538

Составитель А. Сеселкин

Корректор И.Муска

Техред М.Дидык

Редактор Н. Тупица

Тираж 660 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

lI 3035, Москва, Ж-35., Раушская наб., д. 4/5

Заказ 3361/57

Производственно -полиграфическое предприятие, r. Ужгород, ул. Проектная, 4