Устройство для умножения десятичных чисел

Иллюстрации

Показать всеРеферат

Изобретение относится к области , вычислительной техники. Целью изобретения является повышение быстродействия устройства для умножения десятичных чисел. Использование в устройстве К сумматоров 2 в блоке 1 на- 1копления кратных множимого, 2К-разрядного сумматора 4, блока 5 определения очередности дифр и К. счетчиков 7 в блоке 6 контроля значения множителя позволяет считывать в сумматор 4 соответствующие кратные множимого без их сдвига по мере формирования последних в определенных сумматорах 2 - блока 1 накопления кратных множимого, Процессом формирования кратных путем их параллельного накапливания и считьшанием соответствующих кратных множимого управляет блок 5 определения очередности дифро 4 ил, 1 табл. f

СООЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

119) Н1) А1

gg 4 С 06 F 7/52

ОЛИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К ABTOPCH0MV СВИДЕТЕЛЬСТВУ (21) 4126359/24-24 (22) 24.06,86 (46) 15.07.88. Бюл. У 26 (71) Грузинский политехнический институт им. В.И. Ленина (72) В.П. Кожемяко, О.Г. Натрошвили, Н.З, Чхаидзе, Т.В, Мартынюк и В.Г. Гигаури (53) 681.325.5(088.8) (56) Кожемяко В.П. и др. О реализации алгоритмов умножения и вычитания десятичных .чисел на оптоэлектронных сумматорах. — Изв. вузов. Приборостроение, Ф 3, 1976, с, 62-65, Авторское свидетельство СССР

У 510714, кл. G 06 F 7/52, 1974. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ (57) Изобретение относится к области, вычислительной техники, Целью изобретения является повышение быстродействия устройства для умножения де-сятичных чисел. Использование в устройстве К сумматоров 2 в блоке 1 накопления кратных множимого, 2I(-разрядного сумматора 4, блока 5 определения очередности цифр и К. счетчиков

? в блоке 6 контроля значения множителя позволяет считывать в сумматор 4 соответствующие кратные множимого без их сдвига по мере формирования по" следних в определенных сумматорах 2 - блока 1 накопления кратных множимого.

Процессом формирования кратных путем ф их параллельного накапливания и считыванием соответствунзцих кратных множимого управляет блок 5. определения

М очередности цифр, 4 ил, 1 табл, 1410023

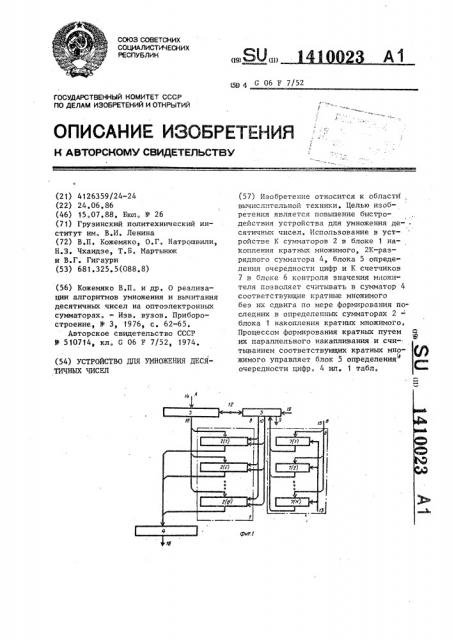

Изобретение относится к вычислительной технике, Цель изобретения — повышение быстродействия устройства для умноже-= ния десятичных чисел, На фиг. 1 представлена структурная схема устройства для умножения десятичных чисел; на фиг, 2 - функ= циональная схема блока определения очередности цифр; на фиг, 3 - алго-ритм работы устройства;, на фиг. 4 временная диаграмма поступления сиг=нала управления устройства.

Устройство для умножения десяти ных чисел (фиг, 1) содержит блок накопления кратных множимого, ссцер= жащий К сумматоров 2 (K = раз-ряд.ность операндов), регистр 3 множимо- 20

I o 2К-разрядный сумматор 4, блок 5 определения очередности цчфр, блок

6 хранения значения, множителя, содер-жащий К счетчиков 7. Вьгхсд 8 блока 5 является выходом сигнала завершения формирования 1(pRTHblx> выходы прHзняксв равенства нулю счетчиков 7 соединены с информационным входом 9 блока

5, выход 10 которого подключен к вхс=дам управления накоплением сумматоров:,0

2 блока 1, a:âbõoä 11 — к вхспам уп-" равления считыванием сумматоров 2 блока 1. Выходы сумматоров 2 блока соединены с входами сумматора 4 таким образом, что:входы разрядов сумматo= ра 4 с первого по (К+1)-и соединены с выходами первого сумматора 2, входы разрядов сумматора 4 со второго по (К+2)-й соединены с выходами второго сумматора 2 и т.д., входы сумматора

4 с К-го по 2К вЂ” с выходами К-гс сумматора 2 . Вход управления считыванием регистра 3 и вход управления считыванием блока 5 подключены к входу 12 управления считыванием устч ройства, счетные входы счетчиков 6 подключены к:входу 13 управления уменьшением значений разрядов множи теля устройства. Информационный вход регистра 3 и:информационные входы

50 счетчиков 6 подключены к шинам 14, 15 множимого и множителя, соответственно, выход сумматора 4 подключен к шине 16 произведения устройства.

Выход 17 блока 5 является выходом за55 вершения операции устройства, выход

18 регистра 3 соединен с информапнон-ным входом каждого сумматора 2 блока

1, установочный вход блока 5 подклю-чен K н стянсвОчнОму вхОду 19 JjcTpoAства а

Блок 5 определения очередности цифр (фиг. 2) состоит из К-разрядных ячеек 20„ каждая из которых содержит

RS.=-триггер 21,, элемент 22 задержки, элементы И 23,, 24 и 25, элемент НЕ 26 и элемент ИЛИ 27, Кроме того, все ячейки 20, кроме К-й, содержат элеме.-,т И--ИЛИ 28„. Блок 5 содержит также

=-лементь1 И 29 и 30, Устройство цля умножения десятичных чисел работает следующим образом. множимое А записывается в регистр 3 по шине 14, умножитель В записыва.-тся в счетчики 7 по шине 15 таким сб;.»азом, что I-" десятичная цифра Кразрядного множителя В записывается в:.--й десятичный счетчик 7. Bce RSтриггеры 21 блока 5 устанавливаются ь "-ЦИНИЧНОЕ СОСТОЯНИЯ Пс СИГнаЛУ у поступающему на вход 19. Сумматоры 2 блока I и сумматор 4 сбнулены, Затем выполняется анализ цифр множителя блоком = с учетом сигналов нулевого содержимого всех,десятичных счстчикoI3 7, ПОступяющих HB вход 9 блока 5.. и при наличии сигнала опроса Т,-.-. Iocтупаюшего на вхolT, 12 блок"", .5 -8 случае если отсутствует сигнал нулевого содержимого в -м счет-=.ике 7, не происходит формирования сигнала разрешения считывания информапии из 1-го сумматора 2 блока 1, поступающего с выхода 11 блока 5 на вход управления считыванием сооТ вет rayiomer o > -ro сумматора 2. Поско" льну в,г,анном слу-гяе информация во в=ех K сумматорах 2 блока 1 равна нулю, тс соответствующие разряды сумматоров 4 останутся в нулевом состоянии„ Одновременно со считыванием инфсрмяц п из определенного сумматора

2 выполняется суммирование содержимого ссстветствуюших сумматоров 2 с мнсжимым A., поступающим с выхода 18 регисrp; 3,. по сигналам управления с выходя 10 блока 5. Затем происходит уменьшение на единицу содержимого всех счетчиков 7. Б следующем цикле

-работы устройства вновь анализируется содержимое всех счетчиков 7 блоком

5 и выполняется считьвяние кратного множимсго из определенногс сумматора

2,, состветствуюшегс счетчику 6, соцержю.oE: которого сбнулилось, и формирсв",ние кратных мнсжимсгс путем сук. «грс явня с содержимым регистра 3

1410023 в сумматорах 2, соответствующих счетчикам 7, в которых информация не равна нулю и уменьшится на единицу в данном цикле. Этот процесс повторяется до тех пор, пока не появится сигнал признака нуля на выходе 17 блока 5. Считывание информации из регистра 3 выполняется по сигналу на входе 12, анализ информации блоком 5 - 1p о сигналу на входе 12, а уменьшение на единицу содержимого всех счетчиков 7 — по управляющему сигналу, поступающему с входа 13 на счетные входы всех счетчиков 7. Таким образом, 15 результат находится в сумматоре 4, в регистре 3 сохраняется множимое А, а все К сумматоры 2 блока j и счетчики 7 обнулены, поскольку считывание информации из сумматоров 2 проис- 2О ходит с обнулением.

Блок 5 определения очередности цифр (фиг. 2) работает следующим образом.

Первоначально по сигналу У по- 25 ступающему на вход 19, происхоцит установка в единичное состояние RS-триггеров 21 с учетом сигналов нулевого содержимого на входах 9 всех ячеек 20.

В случае наличия сигнала нулевого со- 30 держимого в соответствующих ячейках

20 блока 5 появляется едининчый сигнал на выходе элемента И 25, который че»-рез элемент ИЛИ 27 поступает на R- . вход RS-триггера 21 и устанавливает

его в нулевое состояние, что соответствует формированию сигнала завершения считывания информации из соответствующего сумматора 2 блока 1. В случае отсутствия сигнала нулевого со- 4О держимого в соответствующих ячейках

20 нулевой сигнал на выходе элемента И 25 через элемент НЕ 26 поступает на S-вход RS-триггера 2 1 и устанавливает его в единичное состояние. Это означает, что соответствующие ячейки 20 готовы к формированию управляющих сигналов накопления и считывания в процессе работы устройства.

Основная задача блока 5 заключается в выделении десятичного разряда множителя, в котором информация равна нулю, в данный такт работы устройства. При этом просмотр разрядов выполняется, начиная с младшего разряда множителя, т.е. с младшего счетчика 7. Если сигнал нулевого содержимого поступает, например, с выхода первого счетчика 7, то нри.наличии сигнала на входе 12 появляется единичный сигнал на выходе элемента И 23 первой ячейки 20 блока 5, который с выхода 11 блока 5 поступает на вход управления счетыванием первого сумматора 2 блока 1. Одновременно с этим происходит появление нулевого сигнала на выходе элемента И 24, который с выхода 10 блока 5 поступает на вход управления накоплением первого сумматора 2. Во всех остальных ячейках

20 блока 5 в связи с тем, что отсутствуют сигналы нулевого содержимого в соответствующих счетчиках 7, появляется единичный сигнал на выходе элемента И 24 и отсутствует сигнал на выходе элемент". И 23, Таким образом, сигналы на выходах 10 и 11 блока 5 вызывают считывание информации из первого сумматора 2 блока и запись ее в соответствующие разряды сумматора 4 и одновременно суммирование содержимого всех остальных сумматоров 2 блока 1 с содержи ьм реFHcTpB 3. Элемент 22 задержки Во всех ячейках 20 служит для того, чтобь1 препятствовать прохождению единичного сигнала с выхода элемента И 23 на R-вход RS-триггера 21 во время считывания информации из соответствующего сумматора 2 блока 1. Возможен случай, когда одновременно в двух или более ячейках 20 блока 5 по явились сигналы нулевого содержимого, например, в первой и во второй ячейках 20. В этом случае появление единичного сигнала на выходе элемента

И 23 первой ячейки 20 совпадает с блокировкой, которая через элементы

И-ИЛИ 28 запрещает срабатывание элементов И 23 всех следующих ячеек 20.

Таким образом, считывание в каждом такте работы устройства выполняется только из одного соответствующего сумматора 2 блока 1. Одновременно с этим во второй ячейке 20 отсутствует единичный сигнал, как на выходе элемента И 23, вызывающий считывание из второго сумматора 2 блока

1, так и на выходе элемента И 24, вызывающий суммирование содержимого сумматора 2 блока t с содержимым ре" гистра 3, поскольку необходимое кратное в данном сумматоре 2 к этому моменту сформировано.

Блокировка сигнала на выходе элемента И 23 во всех ячейках 20,. начи1410023 сигнала

При Х1 = Π— разрешение формирования кратных множимого в блоке 1 накопления кратных множимого

При Х2 = 1 — завершение выполнения операции умножения

Устанавливает блок 5 в начальное состоXI

Х2

У2

19 яние

Разрешает считывание информации из регистра 3 и синхронизирует работу блока 5 определения очередности цифр

Разрешает уменьшение на единицу содержимого группы К счетчиков 7

У2

У3

13 ь(ая со второй, снимается в том случае, если в предыдущих младших ячейках 20 в данный момент не формируетс я сигнал разрешения чтения, т. е. в

«1их отсутствует сигнал на соответст«вующем входе 9 и RS-триггер 21 нахо1 ится в единичном состоянии, либо ест и в некоторых из предыдущих младших

« чейках 20 сигнал разрешения чтения

« этому моменту уже был сформирован, .е. в них присутствует сигнал нулеого содержимого на соответствующем ходе 9, но RS-триггер 21 находится нулевом состоянии.

Номер Обозначение Назначение связи связи

Алгоритм умножения десятичных чисел (фиг. 3), реализуемый устройством, состоит в следукпцем, 1. Устанавливается в начальное со- 35 стояние блок 5 определения очередноСти цифр, т.е. RS-триггеры 21 всех го ячеек 20 устанавливаются в единичное состояние.

2. Выполняется считывание информации из регистра 3 множимого и суммирование ее с содержимым определенных сумматоров 2 блока 1, определяемых блоком 5 и считывание информации из

Ф

45 соответствующих сумматоров 2 блока 1, также определяемых блоком 5.

3. Проверяется условие нулевого содержимого группы К счетчиков 7, Если отсутствует сигнал нулевого содержимого группы счетчиков 7 (1 = О), то

50 уменьшается на единицу содержимое счетчиков 7 и выполняется переход к п. 2.

4.Если присутствует сигнал нулевого содержимого счетчиков 7 (XI = 1), то

55 проверяется условие завершения операции (Х2 = О), выполняется и, 2, иначе п. 5.

Процесс считывания и накопления соответствующих кратных множимого в сумматорах 2 блока 1 выполняется до тех пор, пока не появится единичный сигнал на выходе 17 блока 5, свидетельствующий о завершении форми рования сигналов разрешения чтения во всех ячейках 20 бло ка 5„

Набор управляющих и логических сигналов, необходимых для реализации алгоритма работы устройства (фи6, 3) приведен в таблице.

5. Операция умножения завершена.

На временной диаграмме (фиг. 4) показана последовательность сигналов

У1, У2 .и Y3, а также временные отрезки Т1 и Т2, соответствующие времени выполнения цикла формирования кратных множимого в блоке 1 и цикла считывания из сумматоров 2 блока 1 информации цо полного обнуления всех сумматоров 2 блока 1.

Формула изобретения

Устройство для умножения десятичных чисел, содержащее регистр множимого, сумматор, блок накопления кратных множимого, блок определения очередности цифр, блок хранения значения множителя, причем выход регистра множимогс соединен с информационным входом блока накопления кратных множимого, (1. — и выход которого (1 = 1, К, К вЂ” разрядность операндов) со сдвигом íà i-разрядов в сторону старших разрядов соединен с входами сумматора, первык и второй выходы блока определения очередности цифр

1410023 соединен с входами управления накопления считыванием блока накопления кратных множимого, информационный вход блока определения очередности

5 цифр соединен с выходом блока хранения значения множителя, информационные входы регистра множимого и блока хранения значения множителя соединены с шинами множимого и множителя 10 устройства, выход сумматора соединен с шиной произведения устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, блок хранения значения множителя со3 держит К счетчиков, блок накопления кратных множимого содержит К суммато-ров> а блок определения очередности цифр содержит два элемента И и К разрядных ячеек, каждая из которых 20 содержит триггер, три элемента И, три элемента ИЛИ, элемент HE элемент задержки, кроме того. каждая разрядная ячейка, кроме последней, содержит элемент И-ИЛИ, при этом ин- 25 формационные входы счетчиков блока . хранения значения множителя поразрядно соединены с информационным входом блока хранения значения множителя,. вычитающие входы счетчиков блока хра- 30 нения значения множителя соединены с управляющим входом блока хранения значения множителя, который подключен к входу управления уменьшением значений разрядов множителя, выходы признаков равенства нулю счетчиков

35 блока хранения значения множителя поразрядно соединены с выходом блока хранения значения множителя, информационные входы сумматоров блока на- 40 копления кратных множимого соединены с информационным входом блока накопления кратных множимого, входы управления накоплением и считыванием сумматоров блока накопления кратных множимого соединены с одноименными входами блока накопления кратных множимого, выходы сумматоров блока накопления кратных множимого являются соответствующими выходами блока накопления кратных множимого, первые

50 входы первых элементов И разрядных ячеек блока определения очередности цифр, поразрядно соединены с информационным входом блока определения очередности цифр, а вторые входы — с

55 установочным входом блока определения очередности цифр, который подключен к установочному входу устройства, в каждой разрядной ячейке блока определения очередности цифр выход первого элемента И через элемент HE подключен к S-входу триггера, S-вход которого соединен с выходом элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, первый вход которого соединен с первым входом второго элемента И и первым входом (инверсным) третьего элемента И, а во всех разрядных ячейках, кроме последней, соединен также с первым входом первой группы элемента

И-ИЛИ и первым входом (инверсным) второй группы элемента И-ИЛИ, второй вход третьего элемента И соединен с вторым входом второго элемента И и входом уп1>авления считыванием блока определения î-iåt>åäíoñòè цифр, который соединен с входом управления считыванием устройства и входом управления с-1итыванием регистра множимого, в каждой разрядной ячейке блока определения очередности цифр прямой вь?ход триггера соединен с третьим входом второго элемента И, а во всех ра- ðnni:.bix ячейках кроме последней, соепинен также с вторым входом второй группы элемента И-ИЛИ, второй вход первой группы элемента И-ИЛИ каждой разрядной ячейки, кроме последней, соединен с инверсным выходом триггера, четвертый вход второго элемента И подключен к выходу элемента И-ИЛИ предыдущей разрядной ячейки блока определения очередно.сти пифр, а во всех разрядных ячейках, кроме последней, соединен также с третьими входами первой и второй групп элемента И-ИЛИ, выход второго элемента И через элемент задержки подключен к второму входу элемента ИЛИ, выходы третьих элементов И разрядных ячеек блока определения очередности цифр поразрядно соединены с первым выходом блока определения очередности цифр, выходы вторых элементов И разрядных ячеек блока определения очередности цифр поразрядно соединены с вторым выходом блока определения очередности цифр, в котором входы первого элемента И соединены с первыми входами первых элементов И разрядных ячеек, инверсные выходы триггеров которых соединены с входами второго элемента И, выходы первого и второго элементов И являются третьим и четвертым вь>ходами бло14 !0023 ка определения очередности цифр которые подключены к выходам сигналов

q т в,е о ц ц» пи сг вавершения

Формирования кратных и операции устройства.

1410023

У!

Тираж 704

Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Редактор А. Долинич

Заказ 3481/45

Составитель В. Березкин

Техред Л.Олийнык Корректор С. Черни