Устройство сопряжения вычислительной системы

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано в высоконадежных вычислительных системах для обработки данных в реальном масштабе времени. Цель - изобретения - повышение надежности функционирования вычислительной системы - достигается тем, что в устройство , содержащее генератор тактовых импульсов и группу формирователей циклов, дополнительно введены,группы элементов ИЛИ и И, элемент ИЛИ, триггер , регистр состояний системы, шифратор, блок памяти, информационный регистр, элемент задержки, причем С формирователи циклов содержат регистр цикла, элемент задержки, триггер пуска , элемент И, элемент ИЛИ,счетчик тактовых импульсов, элемент сравнения , 1 з.п. ф-лы, 2 ил,д

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУб ЛИК (19) (11) Ai

F 15/.16 (5D 4

ОПИСАНИЕ ЙЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОбРЕТЕНИЙ И ОТКРЫТИЙ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4117557/24-24 (22) 22.05.86 (46) 15.07.88. Бюл. 1(26 (72) Г.С.Евтушенко, В.П.Неверов и В.А.Титов (53) 681;325(088.8) (56):Авторское свидетельство СССР.

9 529953, кл. G 06 F 15/16, 1975.

Авторское свидетельство СССР

В 734698, кл. G 06 .F 15/16, 1980. (54) УСТРОЙСТВО СОПРЯЖЕНИЯ ВЫЧИСЛИ.—

ТЕЛЬНОЙ СИСТЕМЫ (57) Изобретение относится к области вычислительной техники и может быть использовано в высоконадежных вычислительных системах для обработки данных в реальном масштабе времени. Цель . изобретения — повышение надежности функционирования вычислительной системы — достигается тем, что в устройство, содержащее генератор тактовых импульсов и группу формирователей циклов, дополнительно введены. группы" элементов ИЛИ и И, элемент ИЛИ, триггер, регистр состояний системы, де шифратор, блок памяти, информационный регистр, элемент задержки, причем (Формирователи циклов содержат регистр цикла, элемент задержки, триггер пуска, элемент И, элемент ИЛИ, счетчик тактовых импульсов, элемент сравнения., 1 з.п. ф-лы, 2 ил.

1410048

Изобретение относится к области вычислительной техники и может быть использовано в высоконадежных вычислительных системах для обработки дан ных в реальном масштабе времени.

Целью изобретения является повы1 !

|шение надежности функционирования

; вычислительной системы, сохранение (l ee работоспособности по реализации задач управления объектом.

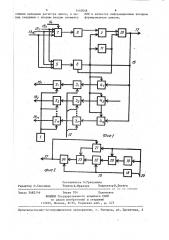

На фиг.1 представлена структурная схема устройства сопряжения вычислительной системы, на фиг.2 — структурная схема формирователя циклов.

Устройство содержит (см. фиг, 1). генератор 1 тактовых импульсов, группу формирователей 2 циклов, группу элементов 3 ИЛИ, группу элементов 4 И, элемент 5 ИЛИ, триггер 6, регистр 7 состояния системы, дешифратор 8, блок

9 памяти, информационный регистр 10, элемент 11 задержки, входы устройства 12-14, выходы 15-17.

Формирователь циклов 2 (см. фйг.2) содержит регистр 18 цикла, элемент 19 задержки, триггер 20 пуска, элемент

21 ИЛИ, элемент 22 И, .счетчик 23 тактовых импульсов, элемент 24 сравнения, а также вход 25, вход 26 и выход 27, являющийся выходом 16 устройства.

Устройство работает следующим образом.

В исходном состоянии регистр 7 находится в нулевом состоянии (его сброс осуществляется управляющим процессором системы по входу 14). Это свидетельствует об исправности всех каналов (ЭВМ) вычислительной системы. ,На регистрах циклов 18 формирователей 2 управляющим процессором вычислительной системы по входу 12 устанавливаются коды, соответствующие циклам работы управляемых ЭВМ, функционируюmmmm в реальном масштабе времени. Кроме того, единичный сигнал, подаваемый по входу 12 на входы элемента задержки 19, триггера 20 и элемента 21 ИЛИ, сбрасывает счетчик 23, сбрасывает в нулевое состояние триггер 20, после чего запрещается подача тактовых импульсов с выхода генератора 1 по входу 26 через элемент 22 И на вход счетчика 23. Через промежуток времени, достаточный для приема кода на регистр 18 цикла и обнуления счетчика 23, единичный сигнал с выхода элемента 19 задержки устанавливает триг10

2

rep 20 в единичное состояние, после чего формирователь 2 циклов готов к работе. В процессе функционирования вычислительной системы этот код может быть изменен.

При выходе из строя 3BN системы от ее блока по входу 13 поступает единичный сигнал неиснравности на соответствующий вход регистра 7 и элемента 5 ИЛИ. С выхода элемента 5 ИЛИ сигнал неисправности устанавлйвает триггер 6 в единичное состояние, с выхода которого единичный сигнал поступает на выход 15 устройства как сигнал управляющему процессору системы о наличии в ней неисправности, а также на первые входы групп элементов

4 И, на вход блока 9 памяти и через элемент 11 задержки — на вход регистра 10. Одновременно код с выхода регистра 7 поступает на вход дешифратора 8, который обеспечивает выбор из готового, к работе блока 9 (на его втором входе находится к этому моменту времени высокий потенциал с выхода триггера 6) на вход регистра 10 соответствующего кода-инструкции, который поступает на выход 17 устройства к управляющему процессору, кроме того, код-инструкция с выхода регистра 10 через открытые группы элементов И 4, группы элементов ИЗГЛ 3 поступает на выходы соответствующих формирователей 2 циклов.

Код-инструкция представляет собой совокупность кодов по числу ЭВМ, в каждом из которых имеется "1", подаваемая на входы элементов 19, 20, 21, а также,код времени цикла решения задач управления объектом в реальном масштабе времени управляемой ЭВМ, подаваемый на регистр 18 циклов.

Каждый формирователь циклов 2 функционирует следующим образом. В исходном состоянии на регистре 18 находится код, пропорциональный величине цикла, который поступает с выхода регистра на первый вход элемента 24 сравнения. После прихода единичного сигнала на вход триггера 20 с выхода элемента 19 задержки на выходе элемента 22 И будут появляться единичные сигналы с генератора 1, которые пос-, тупают на вход ранее сброшенного в нулевое состояние счетчика 23, выход которого подсоединен к второму входу элемента 24 сравнения. При совпадении кодов в элементе 24 на его выходе з 141 появляется единичный сигнал окончания цикла, поступающий в соответствующую

ЗВМ (не показана) и на первый вход элемента 21 ИЛИ, на второй вход которого поступает сигнал сброса, подаваемый по входу 25 управляющим процессором системы или с выхода. регистра

10. Выход элемента 21 ИЛИ подсоединен к установленному в нулевое состояние входу счетчика 23, после чего начинается формирование нового цикла и т.д..

Через время, достаточное для установки на регистре 10 кода-инструкции, перезаписи ее в формирователи 2, с выхода элемента 11 задержки снимается единичный сигнал, который сбрасывает регистр 10 в нулевое состояние, и этим же сигналом сбрасывается в нулевое состояние триггер 6. Предполага- ется также, что к этому моменту времени неисправная ЭВМ будет отключена и регистр 7 будет сброшен в нулевое состояние. 0

При подключении исправной ЭВМ в систему предлагаемое устройство обеспечит перенастройку (реконфигурацию) системы путем изменения кода"инструкции управляющим процессором. системы .по входу 12, в результате чего ЭВМ системы будут функционировать с учетом изменения вычислительной нагрузки после увеличения числа исправных ЭВМ в системе.

Предложенное устройство обеспечивает реконфигурацию управляющей вычислительной системы и тем самым сохраняется работоспособность системы вплоть до выхода из строя последней (или минимального числа) ЭВМ системы.

Формула изобретения

1. Устройство сопряжения вычисли-. тельной системы, содержащее группу формирователей циклов, генератор тактовых импульсов, выход которого соединен с тактовыми входами формирователей циклов группы, о т л и ч а -ю— щ е е с я тем, что, с целью .повышения надежности функционирования вычислительной системы, в него введены регистр состояния системы, элемент

ИЛИ, дешифратор, блок памяти, элемент задержки, информационный регистр, группу элементов ИЛИ, группу элементов И, триггер, вход установки в "1" которого соединен с выходом элемента

ИЛИ, входы которого являются первыми

0048

25

5

10 l5

50 информационными входами устройства и соединены с соответствующими информационными входами регистра состояния системы, информационные выходы которого соединены с информационными входами дешифратора, выходы которого соединены с адресными входами блока памяти, информационные выходы которого соединены с информационными входами информационного регистра, а вход записи соединен с прямым выходом триггера, управляющим выходом устройства, вторыми входами элементов И группы и входом элемента задержкой, выход которого соединен с входом сброса триггера и входом записи информационного регистра, информационные выходы которого являются первыми информационными выходами устройства и соединены с первыми входами соответствующих элементов И группы, выходы элементов И группы соединены с первыми входами соответствующих элементов ИЛИ группы, вторые входы которых являются вторыми информационными входами устройства, выходы элементов ИЛИ группы соединены с информационными входами соответствующих формирователей циклов группы, выходы которых являются вторыми информационными выходами устройства, вход сброса регистра состояния системы является входом сброса устройства.

2. Устройство по п.1, о т л и ч аю щ е е с я тем, что каждый формирователь циклов группы содержит элемент сравнения, счетчик тактовых имнульсов, элемент ИЛИ, элемент И, триггер пуска, элемент задержки, регистр цикла, информационные входы которого являются соответствующими информационными входами формирователя циклов, старший разряд информационных входов которого соединен с входом .сброса триггера пуска, с первым входом элемента ИЛИ и с входом элемента задержки, выход которого соединен с входом установки в "1" триггера пуска, прямой выход которого соединен с первым входом элемента И, второй вход которого является тактовым входом формирователя циклов, а выход соединен со счетным входом счетчика тактовых импульсов, вход сброса которого соединен с выходом элемента ИЛИ, а информационные выходы соединены с первыми входами элемента сравнения, вторые входы которого соединены с информациСоставитель О.Гречухина

Техред A. Êðàâ÷óê Корректор В.Бутяга

Редактор О.Спесивых

Тираж 704 Подписное

ВНИИПИ Государственного-комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Заказ 3482j46.Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

5 i4f0048 6 онными выходами регистра цикла, à вы- ИЛИ и является информационным выходом ход соединен с вторым входом элемента формирователя циклов.