Устройство для приема избыточной информации

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСжИХ

РЕаЪБЛИК

А2 (19) (И1

<5ц 4 С 08 С 19/28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (61) 824263 (21) 3922424/24-24 (22) 01.07.85 (46) 15.07.88. Бюл. У 26 (72) С.В.Науменко, С.Н.Жуков и B.Н.Шевченко (53) 621.398(088.8) (56) Бородин Л.Ф. Введение в теорию помехоустойчивого кодирования. М.:

Советское радио, 1969, с. 270-271.

Авторское свидетельство СССР

11 824263, кл. G 08 С 19/28, 1979. (54)(57) УСТРОЙСТВО ДЛЯ ПРИЕМА ИЗБЫТОЧНОЙ ИНФОРМАЦИИ по авт.св. У- 824263, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения путем обеспечения автоматического регулирования задающего порога, в него введены усилитель с постоянным коэффициентом усиления, усилитель с регулируемым коэффициентом усиления, первый и второй блоки аналого1 ного сравнения, управляемый ключ, дополнительный сумматор, пороговый селектор выполнен управляемым, выход усилителя с регулируемым коэффициентом усиления соединен с входом первого и первым входом второго блоков аналогового сравнения, выход первого соединен с первым входом управляемого ключа, выход которого соединен с вторым входом второго блока аналогово- . го сравнения, выход которого соединен с первым входом усилителя с регулируемым коэффициентом усиления, с вторым входом дополнительного сумматора и регулирующим входом порогового селектора, выход усилителя с постоянным коэффициентом усиления подключен к второму входу управляемого ключа, .входы усилителей с постоянным и регу-! лируемым коэффициентом услияния обЪе- С динены и подключены к выходу приемника.

1410080

Изобретение относится к электросвязи, а именно, к устройствам при, ема избыточных сигналов в целом, и может быть использовано в системах

5 ! передачи дискретной информации в

Э которых для передачи информации при меняются избыточные коды большой мощности.

Целью изобретения являетс» расширение области применения путем обеспечения автоматического регулирования задающего порога.

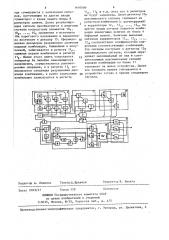

На чертеже приведена функциональная схема предлагаемого устройства. 15

Устройство содержит приемник 1, преобразующий элемент избыточного сигнала в аналоговые величины, например амплитуду импульсов, первый

;пороговый селектор 2, состоящий из 20

Iэлемента 2 сравнения и управляемого источника 22 порогового напряжения, величина которого устанавливается автоматически в зависимости от уровня

;помехи, блок 3 вычитания„ в котором из величин амплитуд выходных им пульсов элемента 21 сравнения вычита-! ются величины амплитуд его выходных ,,импульсов, первый и второй блоки, 4 и 5 буферной памяти, реализованные, ЗО

:например, в виде дискретно-аналоговых (, линий задержки, усилитель 6, состоя ний из п усилителей 6, 6, ..., 6> с регулируемыми коэффициентами уси,ления и регенератора 6,„ линейно из- 5 ,меняющегося напряжения, выходное нап; ряжение которого осуществляет синхронное изменение коэффициента усиления .усилителей 6, 62, ..., 6„ сумматор

7, осуществляющий поразрядное сложе- 40 ние колебаний сигналов, поступающих . на его входы и состоящий из и одноразрядных сумматоров (например, опе. рационных усилителей 7, 7, ..., 7„ ), второй блок 8 реГистров памяти, реа 45 лизуемый в виде, например, последовательного цифрового регистра, информация с которого считывается параллельно, второй пороговый селектор 9, состоящий из п элементов 9, 92„

9„сравнения, источник 9а порогового напряжения ификсатора 9б перехода величины порогового напряжения величиной амплитуды сигнала на выходе одного

Н3 усилителеи 6< 62, 6< третий по 55 роговый селектор 10, состоящий из элементов 101, 10, ..., 10,, сравнения и источника 10а порогового напряжения, первый блок 11 регистров памяти, состоящий из двоичных регистров 11 f у блок 12 упра е я выдачей информации, состоящий из и-корреляторов 121, 12 . . . 12 и детектора 12а максимального сигнала, декодер 13, в котором каждой поступающей на его входы двоичной кодовой комбинации ставится в соответствие ближайшая разрешенная двоичная кодовая комбинация, усилитель 14 с регулируемым коэффициентом усиления, компаратора 15, усилитель 16 с постоянным коэффициентом усиления, управляемый ключ 17, сумматор 18, сравнивающее устройство 19 и блок управления и синхронизации (не показан).

Сущность работы элементов заключается в следующем.

Введенные элементы реализуют процедуру обучения с выравненными ошибками, которая описывается математическим выражением

V(n+1) = V(n) + 8,0(п), Т

Y(n), V (n)Y(n) l, 0; где Q(n)

-Y(n) (n)Y(n) >0, и сходимость которой к минимуму вероятности ошибки доказана °

V(п+1), V(n) — коэффициенты усиления усилителя с регулируемым коэффициентом усиления, выполненного по стандартной схеме;

S„ — шаг, с которым данная процедура сводится к минимуму вероятности ошибки и реализуется„ например, коэффициентом усиления усилителя с постоянным коэффициентом усиления, вь|ставляемым вручную или автоматически в зависимости от характера нестационарной помехи в канале связи;

Y(n) - образцы канальных сигналов, искаженные помехой и поступающие на вход приемника, 1410080

Устройство работает следующим образом.

На вход приемника 1 поступает сложный избыточный сигнал. На выходе

5 приемника 1 появляется (последовательно) совокупность аналоговых сигналов

Y,= (у„, у, ..., У,„), соответствующих элементам входного сигнала, где

n — - количество элементарных сигналов 10 в составном избыточном сигнале и количество двоичных символов в комбинации избыточного кода. Каждый аналоговый сигнал подается на вход усилителя 14 с регулируемым коэффициентом усиления, на вход усилителя

16 с постоянным коэффициентом усиления и на первый вход порогового селектора 2. С выхода усилителя 14 с регулируемым коэффициентом усиления 20 усиленные в V раз аналоговые сигналы поступают на компаратор 15, где производится сравнение полученного произведения V(n) ° (V<) с нулем. По результатам сравнения компаратор 13 25 управляет управляемым ключом 17, разрешая прохождение сигнала f„Y(n) с вых ода усилит ел я .1 6 с пос т оя н ным коэффициентом усиления либо. инверсно, либо неинверсно, т.е. определяет знак произведения S 7(п). Полученный сигнал поступает на второй вход сумматора 18, на первый вход которого поступает сигнал с выхода сравнивающего устройства )9, который является оцен35 кой коэффициента усиления (и соответственно пропорционален ему) усилителя 14 с регулируемым коэффициентом усиления на данном шаге. На выходе сумматора 18 в зависимости от знака 40 произведения Sn (Yn) получается разность или сумма V(n) + Sn,Y(n), которая поступает на вход сравнивающего устройства 19, где сравнивается с сигналом, поступающим на его второй вход с выхода усилителя 14 с регулируемым коэффициентом усиления, Напряжение, полученное на выходе сравнивающего устройства 19 в результате сравнения, одновременно регулирует коэффициент усиления усилителя 14 с

50 регулируемым коэффициентом усиления и поступает на второй вход порогового селектора 2, а именно на вход управляемого источника 2 порогового напряжения, которое изменяется любым известным способом, например изменяется коэффициент усиления усилителя, На вход элемента 21 сравнения поступает аналоговый сигнал с выхода приемника 1. На второй вход элемента

21 сравнения поступает пороговое напряжение управляемого источника 2 по2 рогового напряжения, которое автома- тически изменяется в зависимости от отношения сигнал/шум на выходе приемника 1 по алгоритму, описанному выше. В элементе 2 сравнения осуществляется сравнениа величин входных сигналов. Если величина входного аналогового сигнала меньше величины порогового напряжения, то на выходе элемента сравнения появится сигнал

"0", в противном случае — " 1". Таким образом аналоговый сигнал преобразуется в двоичный. В блоке 3 вычитания из величины двоичного сигнала вычитают величину соответствующего аналогового сигнала. В результате в декодере 13 последовательно записывается кодовая комбинация, соответствующая посимвольному приему входного сигнала.

Декодер в регистр 11, после соот,ветствующих операций записывает (последовательно) двоичную разрешенную кодовую комбинацию, являющуюся бли-. жайшей к двоичной посимвольной. В блоке 8 регистров памяти также последовательно записывается и хранится в нем двоичная кодовая комбинация

1посимвольного приема. В блок 5 буферной памяти записывается и хранится совокупность аналоговых сигналов, полученных с выхода блока 3 вычитания, Из блока 5 памяти эти сигналы параллельно подаются на у-силители

6, 6, ..., 6„ с регулируемыми коэффициентами усиления. В это время запускается генератор 6а линейно изменяющегося напряжения и коэффициент усиления усилителей увеличивается (начальный коэффициент усиления равен 1). Выходные сигналы усилителей подаются на элементы 9, 9, ..., 9 сравнения, к другим выходам которых подключен источник 9а порогового напряжения. Как только в каком-нибудь элементе сравнения выходной сигнал усилителя превысит величину порогового напряжения, сразу же срабатывает фиксатор 9б перехода и генератор ба линейно изменяющегося напряжения выключится. Усиленные сигналы с выхода усилителей 61, 6>, .. °, 6„ подаются на выходы соответствующих одноразрядных сумматоров 7>, 7 . ..,, 7q

141ОО80.

Редактор А. Лежнина Техред A. Кравчук

Корректор В, Бутяга

Заказ 3483/47

Тираж 558

Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, R-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г ° Ужгород, ул. Проектная, 4 где суммируются с величинами сигна-лов, поступающих на другие входы сумматоров с ячеек памяти блока 8 регистров памяти. Далее результиру5 ющие сигналы преобразуются в двоичные сигналы посредством элементов 10, 10 . .. °, 10„ сравнения и источника

10а порогового напряжения и параллельно поступают в декодер 13. Сформированная декодером разрешенная двоичная кодовая комбинация, ближайшая к полученной, записывается в регистр 11у, сдвигля первую комбинацию в регистр

11<. После этого опять запускается генератор ба линейно изменяющегося напряжения, осуществляются рассмотренные операции, и в регистр 114 записывается следующая разрешенная двоичная комбинация, а ранее записанные комбинации записываются в регистр

11 „ 11 и т.д. пока все и регистров не будут заполнены. Далее детектор 12а максимального сигнала считывает из регистров комбинации (с регенерацией) на другие входы которых подается комбинация аналоговых величии из блока 4 буферной памяти. Величины выходных сигналов корреляторов 12, 12

12 соответствуют коэффициентам корреляции соответствующих комбинаций.

Эти сигналы поступают в детектор 12а максимального сигнала, который определяет максимальный из них и соответствующую максимальному сигналу кодовую комбинацию из блока 11 считывает на выход устройства. Далее все элементы памяти считываются и устройство готово к приему следующего сигнала.