Асинхронный последовательный регистр

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении асинхронных устройств приема и передачи информации. Целью изобретения является упрощение регистра . Для достижения этой цели каждая ячейка памяти регистра, состоящая из двух элементов ИЛИ-НЕ и двух инверторов, содержит два ключевых элемента, каждый из которых выполнен на МДП-транзисторе, исток , сток и затвор которого соединены соответственно с вторым и третьим входами и выходом соответствующего элемента ИЛИ- НЕ. Число МДП-транзисторов, составляющих ячейку памяти регистра, по сравнению с прототипом уменьщено с 18 до 14. Частота приема (или выдачи) информации составляет 1/6 Я (CL - задержка переключения МДП-транзистора). 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5у 4 G 11 С 1900

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АBTOPCHOMY СВИДЕТЕЛЬСТВУ

4Ь

CO

@АР

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4147273/24-24 (22) 17.11.86 (46) 15.07.88. Бюл. № 26 (71) Ленинградский электротехнический институт им. В. И. Ульянова (Ленина) (72) В. И. Варшавский, А. Ю. Кондратьев, Н. М. Кравченко и Б. С. Цирлин (53) 681.327.66 (088.8) (56) Авторское свидетельство СССР № 661606, кл. G 11 С 19/00, 1976.

Авторское свидетельство СССР № 1136216, кл. G 11 С 19/00, 1985. (54) АСИНХРОННЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ РЕГИСТР (57) Изобретение относится к автоматике и вычислительной технике и может быть ис„„SU„„1410103 пользовано при построении асинхронных устройств приема и передачи информации. Целью изобретения является упрощение регистра. Для достижения этой цели каждая ячейка памяти регистра, состоящая из двух элементов ИЛИ вЂ” НЕ и двух инверторов, содержит два ключевых элемента, каждый из которых выполнен на МДП-транзисторе, исток, сток и затвор которого соединены соответственно с вторым и третьим входами и выходом соответствующего элемента ИЛИ—

HE. Число МДП-транзисторов, составляющих ячейку памяти регистра, по сравнению с прототипом уменьшено с 18 до 14. Частота приема (или выдачи) информации составляет 1/6 (Ч вЂ” задержка переключения

МДП-транзистора). 1 ил.

14!0!Оз

40

55

Изобретение относится к автоматике и вычислительной технике и может быть ис( пользовано при построении асинхронных устройств приема и передачи информ ации.

11елью изобретения является упроп(ение регистра.

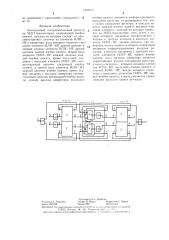

На чертеже приведена схема предлагаемого регистра.

Регистр на ЧДП-транзисторах содержит ячейки 1 памяти, каждая из которых состоит ( из двуx симметричных цепочек 2, выполненных на инверторе 3 и элементе ИЛИ вЂ” - HE 4, первый 5 и второй 6 входы цепочек и первый

7 и второй 8 выходы цепочек, управляющий вход 9 считывания регистра, информ ационные выходы 10 регистра, управляющий выход 11 записи регистра, информ ационные входы 12 регистра, элемент ИЛИ вЂ” HE 13, первый и второй инверторы !4, третий инвертор 15 и ключевой элемент 16, выполненный на МДI I-транзисторе.

Регистр работает следующим образом.

Состояние ячейки 1.1 (значение на инне!эсно (ппфорх(ац((онно((BhlxoJc 7 K2ih30i( цепочки) соответствует 10 — в ячейке записан О, 01 в ячейке записана 1; 00 -- в ячеHK(. отсутствует информация. Состояние

11 в процессе работы регистра в ячейке не возникает из-за перекрестной связи между цепочками ячейки.

Наборы значений на входах 12 соответствуют: 01 -- источник передает 0; 10 -- источник передает 1; 00 -- источник не передает информацию в регистр. Набор 11 — за(1 ре(це и.

Значение на управляющем входе 9 регистра соответствует: 1 — прием ник готов к приему информации из регистра; Π— приемник принял из регистра информацию.

Запись информации в ячейку 1.i »o входам 5 и 6 происходит тогда, когда в ячейке

1. (i — 1) записана информация, а в ячейках

1.(i+1) информация стерта или имеет значение, противоположное записываемой. Сти.рание информации в ячейке 1.(происходит тогда, когда в ячейке 1(i+1) записана та же информация, а в ячейке 1. (i — 1) информация стерта или имеет значение, противоположное записанной в ячейке 1,i.

Пусть в начальном состоянии информация в регистре отсутствует, т.е. значения на инверсных и прямых информационных входах ячеек памяти 00 и 11 соответственно.

Пусть также на входе 9 зафиксирована единица. Источник передает в регистр информацик), устанавливая на его входах 12, например, набор 01. Как только эта информация запишется в первую ячейку, на выходе 11 регистра появится значение О. Появление 1 на инверсном. информационном выходе ячейки открывает ключевой элемент 16 соответствующей цепочки, в результате управляющий и информационные входы цепочки закорачиваются между собой. Это означает, что пока управляющий вход данной цепочки (инверсный информационный выход соответствующей цепочки последующей ячейки) имеет значение О, регистр на изменение входа не реагирует, однако и изменение значения на управляющем входе невозможно при наличии О на информационном. Теперь источник может установить на входах 12 значение 00 для того, чтобы затем передать новую порцию информации. После этого информация переписывается из первой ячейки регистра во вторую, разрешая стирание информации в первой ячейке. Как только в первой ячейке регистра информация будет стерта, источник может записать в регистр следующук>. порцию информации, одновременно будет идти процесс переписи информации из второй в третью ячейку.

Таким образом, последовательная передача в регистр порций информации при фиксированном значении на его входе 9 продолжается до тех пор, пока не заполнится весь регис(р. При этом между двумя ячейками, хранящими соседние порции информации с одинаковыми значениями, будет находиться одна ячейка, в которой информация стерта, если же значение соседних порций информации различно, то они хранятся в смежных ячейках.

Пусть на входах 12 регистра зафиксирован набор 00, а в результате заполнения регистра информацией состояние его последней ячейки — 10. Получив эту информацию с выходов 10 регистра, приемник устанавливает на его входе 9 О, что вызывает стирание информации в последней ячейке. В результате, если в последней и предпоследней ячейках регистра записаны порции информации с различными значениями, появляется возможность переписи информации из предпоследней ячейки в последнюю, затем информация переписывается из ячейки. предп(ествующей предпоследней, и т.д. Как только информация в последней ячейке стерта, приемник может установить на вхо Iе 9 регистра 1, т.е. подготовиться к приему с,(едующей порции информации. Таким образом, последовательный прием информации пз регистра при зафиксированном наборе на его входах 12 продолжается до тех пор, пока весь регистр не будет очищен, т.е. во всех его ячейках не будет стерта информащ(я.

При одновременной работе источника и приемника информации процесс передачи ее протекает аналогично описанному.

Время записи (стирания) информации в ячейке паяти асинхронного последовательного регистр а составляет 2, где ь — задержка МДП-транзистора. Частота выполнения операции сдвига в регистре составляет

1(6< .

Число МДП-транзисторов, составляю(цих ячейку памяти предлагаемого регистра, 7. 17- 11

4 1

Составитель А. Дерюгин

Редактор Л. Лежнина Техред И. Верес Корректор С. Черни

Заказ 3487/49 Тираж 590 Подписное

ВНИИ!1И Государственного комитета CC(.Ð по делам изооретсний и огкрмтий

113035, Москва, Ж вЂ” 35, Раушскпя í !0, .ь 4 5

11роизводственно-полиграфическое предприятие, г. Ужгород. ул. 11роектпая. 4 по сравнению с прототипом уменьшено с 18 до 14.

Формула изобретения

Асинхронный последовательный регистр на МцП-транзисторах, содержащий ячейки памяти, каждая из которых состоит из двух симметричных цепочек из элемента ИЛИ—

НЕ и инвертора, вход которого соединен с вы ходом элемента ИЛИ вЂ” НЕ данной цепочки и первым входом элемента ИЛИ вЂ” НЕ другой цепочки данной ячейки памяти, второй вход элемента ИЛИ вЂ” НЕ каждой цепочки каждой ячейки памяти, кроме последней, соединен с выходом элемента ИЛИ вЂ” HE соответствующей цепочки следующей ячейки 15 памяти, а третий вход элемента ИЛИ вЂ” HE каждой цепочки ячейки памяти, кроме первой соединен с выходом инвертора соответствующей цепочки предыдущей ячейки памяти, причем выходы инверторов последней ячейки памяти являются информационными выходами регистра. отличающийся тем, что, с целью упрощения регистра, в каждую цепочку каждой ячейки памяти введены ключевые элементы, каждый из которых выполнен на ЧДП-транзисторе, сток, исток и затвор которого соединены соответственно с вторым и третьим входами и выходом элемента ИЛИ вЂ” НЕ данной цепочки, три llllвертора, входы первого и второго инверторов являются информационными входами регистра, а выходы соединены с третьими входами элементов ИЛИ вЂ” HE первой ячейки памяти, вход трет1»его инвертора является управляющим входом считывания регистра, а выход соединен с вторыми входами элементов ИЛИ вЂ” НЕ последней ячейки памяти, и элемент. ИЛИ вЂ” HE, входы которого соединены с выходами элементов ИЛИ вЂ” HE первой ячейки памяти, а выход является управляющим выходом записи регистра.