Устройство для преобразования непозиционного кода в позиционный код

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки и передачи цифровой информации для преобразования чисел из непозиционного кода в позиционный. Целью изобретения в Г HiFez является упрощение устройства. Уст- 1ройство содержит управляющий 1, тактовый 2, информационные 3.1,3.2,..., 3.k входы, регистр 4 сдвига, входные регистры 5.1,5.2,...,5.k, блок 6 счетчиков по модулю k, счетчик 7 по модулю mj, мультиплексор В, блок 9 памяти констант, сумматор 10 по модулю т|, функциональный преобразователь 11-, формирователь 12 переноса, блок 13 счетчиков по модулю р, блок 14 сумматоров по модулю р, первый 15, второй 16, третий 17 буферные регистры и выход 18 устройства. Введение регистра сдвига, блока счетчиков по модулю k, блока счетчиков по модулю р, блока сумматоров по модулю р, мультиплексора , функционального преобразователя и формирователя переносов позволяет сократить объем блока памяти констант. 1 ил. rvd оо

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

„„SU„„1410281 A1 (д!) 4 Н 03 М 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ASTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 41 5781 1/24-24 (22) 08.12i86 (46) 15.07.88. Бюл. В 26 (71) Научно-исследовательский инсти» тут прикладных физических проблем им. А.Н. Сенченко (72) Л.Н. Васнлевич, А.А. Коляда, В.В. Ревинский и М.Ю. Селянинов (53) 681.3 (088.8) (56) Авторское свидетельство СССР

В 1179546, кл. Н 03 М 7/00, 1985. (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ

НЕПОЗИЦИОННОГО КОДА В ПОЗИЦИОННЪ|Й

КОД (57) Изобретение относится к вычислительной технике и момет быть использовано в устройствах обработки и передачи цифровой информации для преобразования чисел иэ непоэиционного кода в позиционный. Целью изобретения является упрощение устройства. Уст ройство содержит управляющий 1, тактовый 2, информационные 3. 1,3.2,..., .

З.k входы, регистр 4 сдвига, входные регистры 5. 1,5.2,...,5.k блок 6 счетчиков по модулю k, счетчик 7 по модулю m> мультиплексор 8, блок 9 памяти констант, сумматор 10 по модулю и>, функциональный преобразователь

11 формирователь 12 переноса, блок

13 счетчиков по модулю р, блок 14 сумматоров по модулю р, первый 15, второй 16, третий 17 буферные регистры и выход 18 устройства. Введение регистра сдвига, блока счетчиков по модулю k блока счетчиков по модулю р, блока сумматоров по модулю р, мультиплексора, функционального преобразователя и формирователя переносов позволяет сократить объем блока памяти констант. 1 ил.

1410281 (Ю

Изобретение относится к вычисли гельной технике и может быть испольковано в устройствах обработки и пере (ачи цифровой информации для преоб5 азования чисел из непозиционного коа в позиционный.

Целью изобретения является упрощеие устройства.

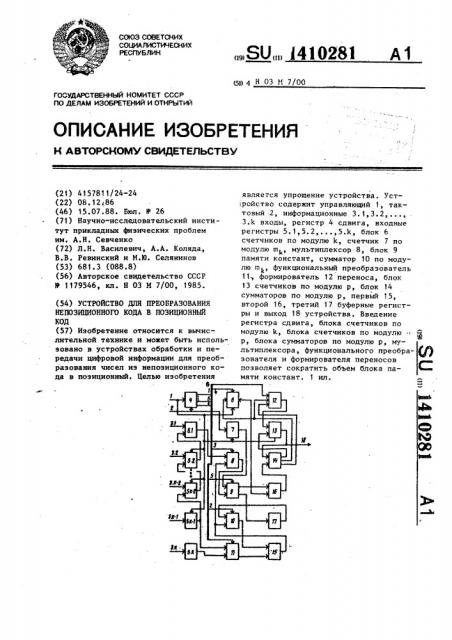

На чертеже представлена схема уст- 10 ойства преобразования непозиционноо кода в позиционный.

Устройство содержит управляющий 1, актовый 2, информационные входы 3.1, .2,...,3.k устройства, регистр 4 15 двига, входные ре.гистры 5, 1, 5.2,..., блок б счетчиков по модулю 1(, четчик 7 по модулю k мультиплексор блок 9 памяти констант, сумматор

10 по модулю m1 функциональный преоб-20 азователь 11, формирователь 12 переосов, блок 13 счетчиков по мо улю р, первый 15, второй 16, третий 17 буерные регистры и выход 18 устройства.

Регистр сдвига имеет разрядность

lk+2 бит, единичный вход триггера младшего (нулевого) разряда регистра сдвига 4 и нулевые входы триггеров стальных разрядов регистра сдвига 4 в совокупности составляют его уста- ЗО новочный вход, который подключен к управляющему входу 1 устройства, управляющий вход сдвига регистра сдвига

4 соединен с тактовым входом 2 устройства. Прямой и инверсный выходы младшего разряда регистра сдвига 4 являются соответственно его первым и вторым выходами, прямой выход (k-1)—, orо разряда регистра сдвига 4 является его третьим выходом, прямой и и 4р инверсный выходы k-oro разряда реги стра сдвига 4-являются соответствен но четвертым и пятым выходами регистра сдвига 4, прямой выход (1с+1)-ого. разряда регистра сдвига 4 является его шестым выходом. На каждом такте работы устройства по сигналу, подаваемому с тактового входа 2 устройства на вход управления сдвигом регистра сдвига 4, его содержимое сдвигается на один бит в сторону старших разрядов.

Разрядность i-oro входного регистра 5.i составляет в бит (i = 1,2,..., k), где b = (bi), bi = ) logjam (,55 через )x„f обоэ1тачается наименьшее целое число, не меньшее х; m » m

m 1, — основания модулярной системы счисления, являющиеся попарно простыми числами.

Блок памяти 9 для хранения констант обладает емкостью 2 Ь слов разрядностью n3l.og р + Ь1 бит; Т

=jlag kf =„„«)hi)

k) n — количество цифр р-ичного представления числа, n = )log (2M)f, M =

П тп, m — вспомогательный модуль, Сщп выбираемьлт из условий m в 7 k 2, m < т, 2.m и +k-2. В память блока 9 по адресу (i-1)+2 м; записывается набор

Т констант ; = Cx р х ° ° ° х в- ° (} (1) (1 I (;} (1 — цифры р-ичного пред »B ления числа M g, I М; 1, Х I I m j1

1-1 ° z Ь1 х (" ю ° У р цифры р-ичного представления числа

Х.M1, „, где

К,= (— )М; „Х щ;), i = 1,2,...,k-1 к1, = М%„X%(m„1 (1)

К =,П.пЧ, M «™р/т;, (2) е

Х, если Х (m

Х1- m1,, если Х1,, тп, через (х ) обозначается ближайшее к х целое число, Х; 0,1,... m..--1 ), 1

1,2,...,1с, (3 (i) 61

Цифры х, х ... х „, р-ичного представления числа снимаются с первого выхода блока памяти 9 для хранения констант, на втором выходе которого формируется величина R;

2,...,k..

Сумматор 10 по модулю тп1, может быть реализован с помощью постоянно" го запоминающего устройства емкостью

2 слов разрядностью Ь k бит (Ь 1, =

7. Sk

= ) 1ogrm1) в память которого по адресу Хт,+2 т 1, записывается константа в

Z = IX <+ Y (Х Y<6(0 1у ° ° ° ш 1).

Функциональный преобразователь реализуется на основе постоянного запоминающего устройства, обладающего ц(- 1+ т.1 емкостью 2 слов разрядностью

Ь1, бит (Ь1= )log m (, ) = k-1, k) ° г

В его память по адресу Хь,т+2 Х 1, записывается вычет о = t 1, + т,(ш, где Р =(— — fg .g / щ„) ш1, к-т, 1

14 10281

:Rk ) М Xkiш через У! обозначается наименьший неотрицательный вычет, сравнимый с величиной Y по модулю m.

Блок 14 сумматоров по модулю р содержит и сумматоров по модулю р с формированием признаков переполнения и равенства суммы вычету р-1. Выходы суммы признака переполнения v . и

1 признака Ф; равенства суммы вычету р-1 i-ого сумматора (i = 1,2,...,п) блока l4 являются соответственно пер- 15 вым, вторым и третьим выходами сум" матора, Первые выходы всех сумматоров блока 14 в совокупности образуют первый выход блока 14, вторые выходы сумматоров с первого по (п-1)-ый бло- 20 ка 14 в совокупности образуют второй выход блока 14; третьи выходы сумматоров со второго по (п-1)-ый в совокупности образуют третий. выход блока 14. 25

Блок 6 счетчиков по модулю k содержит п-1 счетчиков по модулю k. Входы обнуления всех счетчиков блока 6 объединены и являются входом обнуления блока 6. Счетные входы счетчиков по модулю k блока 6 в совокупности образуют счетный вход блока 6.

Блок 13 счетчиков по модулю р содержит и счетчиков по модулю р; счетные входы счетчиков блока 13 с треть3S его по и-ый в совокупности образуют счетный вход блока 13; информационные входы всех счетчиков блока 13 в совокупности образуют его информационный вход.

Формирователь 12 переносов служит для формирования переносов ь, в (j+1)-ый разряд р-ичного кода числа: ñ,0, где 6< — величина, подаваемая на первый вход формирователя

4 1 3° . ° ° ) i01IÇ ° ° ° 4"

Ч (d> д Ч ш. j = 1,2. ..,п-2, )-1 )

Формирователь 12 может быть реализован с помощью и-2 формирователей переносов и группы из и-2 двухвходо50 вых элементов И., Устройство работает следующим образом.

По сигналу f1 = 1, подаваемому с управляющего входа 1 устройства на установочный вход регистра сдвига 4, входы обнуления счетчика 7 по модулю блока 6 счетчиков по модулю k u блока 13 счетчиков по модулю р, а также на управляющие входы входных регистров 5.2,5.3.. .,5.k-1, в младший (нулевой) разряд регистра сдвига 4 записывается единица, а остальные его разряды обнуляются; счетчик 7 по модулю k и счетчики, входящие в состав блоков 6 и 13, обнуляются, модулярный код (х, х,..., х ) исходного целого числа Х из диапазона модулярной системы счисления D =

= ) -M -М+ 1, ...,М-1 через входы устройства 3. 1, 3. 2, ..., З.k записывается во входные регистры 5. 1,5.2. ..5.k; после чего начинается первый такт работы устройства; сигналы, 4 вырабатываемые соответственно на выходах с первого по шестой регистра сдвига 4, являются управляющими сигналами.

На первом такте работы на управляющий вход мультиплексора 8 с третьего выхода регистра сдвига 4 посту пает сигнал Ьз = О, в соответствии с чем содержимое х 1 первого входного регистра 5.1 через первый информационный вход мультиплексора 8 поступа" ет на первый информационный вход блока 9 памяти констант, на второй информационный вход которого с выхода счетчика 7 по модулю k поступает величина i = 0, на управляющий вход блока 9 памяти констант с пятого выхода регистра сдвига 4 поступает сигнал 6 = 1; из блока 9 памяти конс5 т. „ тант по адресу О + 2 Х, считывается набор констант V, = (х (, х(„ 1

°...х (,, R „) . при этом цифры х (1 х,...,х „ i р-ичного представления

Э 1 числа М М, „; Х,„, с первого

I выхода блока 9 памяти констант передаются во второй буферный регистр 16 через первый его вход (на второй вход второго буферного регистра 16 поступает нулевая информация, так как

6q = О), а вычет R запоминается в третьем буферном регистре 17. Одновременно с этим содержимые х „ входного регистра 5.k-1 и Х „ входного регистра 5.k поступают соответственно на первый и второй информационные входы функционального преобразователя

11, на управляющий вход которого с первого выхода регистра сдвига 4 подается сигнал 6,= 1, вычет Q формируемый на выходе функционального пре-, образователя 11 передается в первый буферный регистр 15 через второй его вход (на первый вход первого буфер1410281 н ro регистра 15 в это время поступае нулевая информация, так как ь = О) .

К оме того, на первом такте содержим е регистра входного 5.j пересылает- с т в регистр 5.j-1 (на управляющий в од входного регистра 5.j с управляего входа 1 устройства поступает с гнал Г< = О) для всех j = 2,3..

1; по сигналу Г2 = 1, поступающес тактового 2 входа устройства, содержимое регистра сдвига 4 сдвигается на один бит в сторону старших азрядов, а содержимое счетчика 7 по одулю k увеличивается на единицу, На втором такте работы устройства содержимое R1 третьего буферного реистра 17 поступает на первый вход умматора 10 по модулю m<, на второй ход которого подается величина Яо с 20

ыхода первого буферного регистра 15, умматор 10 по модулю m находит вы} ет Q„= (R<+ Q } m},, который запоминатся в первом буферном регистре 15 (2= 1, 6„ = О). Содержимое второго 25 уферного регистра 16 (набор цифр

-ичного представления (x, х (,, (1} (1}

11-1 х ) поступает на второй вход лока 14 сумматоров по модулю р, на

r ервый вход которого с выхода блока

3 счетчиков по модулю р поступает

«абор величины (у, у . ..,у „ 1 7, (1} (11 (1} ричем у = О, j = О, 1,...,n-1. Блок

4 сумматоров по модулю р, складывая о модулю р входные величины, на пер35

1 ом своем выходе формирует набор вы }етов (у(у(},...,у(>, где у

Ф у <1}+ х(1} (р, j = 0,1,...,n-1, ко}орый1 поступает на информационный ход блока 13 счетчиков по модулю р, 11«а счетный вход которого с выхода фор1«тирователя 12 переносов поступает на-..

i л(1} n(1} п (1}

i(op величин C(с,, т,..., p „„,7, где с (>= О; 1 = 3, 4,..., и . (О), Йа втором вьгходе блока 14 сумматоров

11то модулю р формируется набор двухзначных величин (11,, 411,..., tb1 „7 (1} (1}

: де 4f ° = Ц(у(+ х })}р), который nel

pepается на счетный вход блока 6 счетчиков по модулю k, при этом содержимое ()+1)-ого счетчика блока 6 увечивается на 1, если ы 1 (j = 9, (1}

1,...,n-2).

Параллельно с изложенным на вто ром такте работы на управляющий вход мультиплексора 8 поступает сигнал

6 = О, в соответствии с чем содер}кимое х первого входного регистра

5,1 поступает на второй информационный вход блока памяти 9, на первый информационный вход которого псдается содержимое i = 1 счетчика 7 по модулю k. Из блока памяти 9 (6 = 1) считывается набор констант V 2 =:(х (2) х 1,... х, R 27., при этом ц« фры

ИУ (2} хто, х т,..., х „, 1 р-ичного представления числа М2 }, 21М z }, 1Х2}т z передаются во второй буферный регистр 16 (44 = О), а вычет R q записывается в третий вспомогательный регистр 17.

Кроме этого,. на втором такте содержимое входного регистра 5.j пересылается в регистр 5.j-1 (Г1 = О) для всех

2,3,...,k-1; содержимое регистра сдвига 4 сдвйгается на один разряд в сторону старших разрядов, а содержимое счетчика 7 по модулю k увеличивается на единицу (Г2 = 1)..

На t-ом такте работы устройства (t = 3,4,...,k-1) содержимое R g третьего буферного регистра 17 поступает на первый вход сумматора 10 по модулю m}, на второй вход которого подается величина (с вьгхода первого буферного регистра 15; сумматор }0 по модулю ш находит вычет () 1 = — jR<,+ Я.(>1тп1,, который запоминается в первом буферном регистре 15 (62 = 1, 6„= О) . Содержимое второго буферного регистра 16 (набор цифр (х (} х (} ... х(} )р-ичного

О °, ° Р-1

-2 представления числа М

«Х g2(m („) поступает на второй вход блока 14 сумматоров по модулю р, на первый вход которого с выхода блока

13 счетчиков по модулю р поступает (+-1} (Ф-Ч (й-}J набор величин у, у... у „, «2 (И где у =!Х:х 1 (р, 1 = 0,1,..., !

) и-1. Блок 14 сумматоров по модулю р, складывая по модулю р входные величины,. на первом своем выходе формирует набор вычетов у, у,,у (ф}, (Ф} 1.e} (Ц f (1ii+ (Е- я}I е

11 1), которыи поступает на информационный вход блока 13 счетчиков по мо" дулю р. Так как на данном такте 6 =0,,то с выхода формирователя 12 на счетный вход блока 13 счетчиков по модулю р поступает набор величин ((2 } Гт, n). На втором выходе блока 14 сумматоров по модулю р формируется набор двухзначных величин (признаков пере(4-1} (e-1} (1-1) поннення1 (w I,w,,... ы „е 7, где м(= j(y 1. + х > )1р) (j

1410281

0,1,...,п-2), который передается на счетный вход блока 6 счетчиков по модулю k; в (j+1)-ом счетчике блока 6

С-i . (с-f» (Ю формируется величина иj = td е= представляющая собой сумму переполнений, произошедших при сложении по модулю р величин х(» х ® ... х (! » (j = 0,1,...,n-2), Параллельно с изложенным íà t-ом такте работы устройства на управляющий вход мультиплексора 8 поступает сигнал 6э = О, в со- ответствии с чем содержимое х перво1 го входного регистра 5.1 поступает на15 второй информационный вход блока 9, на первый адресный вход которого подается содержимое = t-1 счетчика 7 по модулю k. Из блока памяти 9 ((j<

1) считывается набор констант V y 20 (х >, х, ...,х, Rg при этом цифРы х, х „,..., х, передаются во.

ll-1 второй буферный регистр 16 (b4 = О), а вычет R< записывается в третий буферный регистр 17. Кроме этого на

t-ом такте содержимое входного регистра 5.j пересылается в регистр

5.j-1 (Г „ = О) для всех j = 2,3,..., k-1; содержимое регистра сдвига 4 сдвигается на один бит в сторону стар-30 ших разрядов, а содержимое счетчика

7 по модулю k увеличивается на единицу.

На (k-1)-ом такте работы устройства в первом буферном регистре !5 будет получен вычет Q < совпадающий с машинным интервальным индексом исходного числа Х.

Q1,,= Ik(X) =! XR1, 40

» j k ге R . — определяются формулами (1) и (2) (j = 1,2,...,k); Т»,(Х) =

)I k(X) 1„ где Т »(Х) — интервальный индекс числа Х, определяемый соот-45 ношением

%- .Х=gN;k, М. х)m;+ Т (Х) М

1а1

Ha k-ом такте работы устройства вы50 полняются действия, аналогичные описанным выше на тактах со второго по (k-1)-ый. Отличие лишь состоит в том, что на k-ом такте на управляющий вход мультиплексора 8 поступает сигнал by= 1, в соответствии с чем содержимое Q 1, = 21,(Х) первого буферного регистра 17 через второй информапионный вход мультиплексора 8 поступает на второй информационный вход блока памятй 9, на пеРвый информа ционный вход которого подается содержимое. i = k- f счетчика 7 по модулю

Из блока памяти 9 (6> = 1) считывается набор констант V k = C, К», ы,», ...,х „, Rk, при этом цифры х,, х,, (2 х "2 р-ичного кода чиста I (Х) х

I1- 1 хМ < „передаются во второй буферный регистр 15 (4 = О) .

На (k+1)-ом тахте работы устройства содержимое второго буферного регистра 15 (набор цифр (х », х ("»,..., (%» х „, )) поступает на второй вход блока

14 сумматоров по модулю р, на первый вход которого с выхода блока 13 счетчиков по модулю р поступает набор ве— личин (уь, у,,..., у,), где (2 2 (k» (О

»(-1 у . = х (p g = О, i и-1. Блок е=

14 сумматоров по модулю р, складывая по модулю р входные величины, на первом своем выходе формирует набор вычетов (у, у, ° ° °, у „Д где у; — у("» + х "!р (j = 0,1,...,п-f), ко1 торый поступает на информационный вход блока 13 счетчиков. Так как на данном такте 6 = О, то с выхода формирователя 12 на счетный вход блока 13 счетчиков по модулю р поступает набор л (» 2 д (» булевых величин (, "),..., 7 где,= О (I = 3,4,...,n). На втором выходе блока 14 сумматоров по модулю р сформируется набор двухзначнь с величин СИ» И 1,..., Ы „<7, где

М Ж (1» (d. = ((у, + х(») )р) () = 0,1,..., n4), который поступает на счетный вход блока 6 счетчиков по модулю k; в (j+1)-ом счетчике блока 6 формиру-! »с (f2 ется величина Г. = и, представляе= ющая собой сумму переполнений, произошедших при сложении по модулю р величин х(2, х »2...., х .» (j = 0,1, ...,n-2). Так как на данном такте на управляющий вход блока 6 с четвертого выхода регистра сдвига 4 поступает сигнал 6,2 = 1, то набор величин ((),, 721,..., Р 7 с выхода блока 6 счетчи1 ков по модулю k передается через второй вход во второй регистр 16 (6< = О) в котором будет записан набор величин (О, iо, 6i Н„ и . Вычет у î совпадает с младшей цйфрой х р-ичного кода

Ь числа X.

На заключительном (k+2) -ом такте работы устройства содержимое второго

1410281 егистра 16 (набор величин О, 9,, ..., рд ) поступает на второй вход лока 14 сумматоров по модулю р, на ервый вход которого с выхода блока

13 счетчиков по модулю р поступает набоР величин (x„y1 уй ° ° у,р-1 . лок сумматоров по модулю р, складыая входные величины, на первом свом выходе формирует набор вычетов 10

n n и

Хр Х) Xg p X g) ! У + 111 P 3 =,2,...,п 1, кото" !

ый поступает на информационный вход лока 13 счетчиков по модулю р. Велиина 4< 1 2,3;;...п-1 представлят собой неточное значение 1-ой цифы хр р-ичного кода числа Х, а велии ина х совпадает с истинным эначени1. м второй мпадшей цифры х1 р"чного ода числа Х, На втором и третьем вы-20 одах блока 14 сумматоров по модулю будут сформированы соответственно аборы признаков (ldll <, у„,) и р, d, р „,), поступающие на второй третьи входы формирователя 12, на 25 ервый вход которого с шестого выхода егистра сдвига 4 подается сигнал

6< =- 1. Формирователь 12 на своем выоде формирует набор значений переноов („, (,..., ю„„), где р;„ - пе- 30 и и енос в ()+1)-ый разряд р-ичного коа числа Х ь 1+1 = i, bg, 4 1+1 =

>1 Ы ° °, ф "ъ,4

1,2,...,n-2. Набор эначенйй переосов (2<,..., „,) поступает на четный вход блока 13 счетчиков по

35 одулю р; в результате коррекциисоержимого 1-ого счетчика блока 13 — 1,2,...,n-2) в нем будет получе()+1)-ая цифра х (+1 i х +! + +г 1 40

-ичного позиционного кода числа Х. скорые значения цифр X „ y<,...,õ „ „ цоступают на выход блока 13 .счетчиtcoa по модулю р и могут быть счита ы посредством выхода 18 устройства; 45

1 а этом процесс преобразования моду,1 ярного кода исходного числа в двоичйый код заканчивается.

Формула изобретения

Устройство для преобразования .не позиционного кода в позиционный код, содержащее Е входных регистров (где

k — число оснований тп -й непозицион ной системы счисления), первые входы .которых являются соответствующими информационными входами устройства, начетчик по модулю k, блок памяти контант, сумматор по модулю m> и буферные регистры, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, в него введены регистр сдвига, блок счетчиков по модулю k, блок счетчиков по модулю р (где р — основание позиционной системы счисления), блок сумматоров по модулю р, мультиплексор, функциональный преобразователь и формирователь переносов, первый— шестой выходы регистра сдвига соединены с управляющими входами соответственно функционального преобразователя, сумматора по модулю mk, мультиплексора, блока счетчиков по модулю блока памяти констант и формирователя переносов, выход первого входного регистра соединен с первым информационным входом мультиплексора, выходы j -ro входного регистра (j = 2,...,k-2) соединен с вторым входом (j 1)-го входного регистра., выход (1с-1)-го входного регистра соединен с вторым входом (k-2)-го входного регистра и с первым входом функционального преобразователя, выход

k=ro входного регистра соединен с вторым входом функционального преобразователя, выход которого соединен с первым входом первого буферного регистра, выход которого соединен с первым информационным входом сумматора по модулю m < и с вторым информационным входом мультиплексора, выход которого и выход счетчика по модулю k соединены соответственно с первым и вторым информационными входами блока памяти констант, первый и второй выходы которого соединены соответственно с первым входом второго буферного регистра и входом третьего буферного регистра, выход которого соединен с вторым информационным входом сумматора по модулю m1 выход которого соединен с вторым входом первого буферного регистра, выход блока счетчиков по модулю k соединен с вторым входом второго буферного регистра, выход которого соединен с первым входом блока сумматоров по модулю р, первый, второй н третий выходы которого соединены соответственно с информационным входом блока счетчиков по модулю р, объединенными первым входом формирователя переносов и счетным входом блока счетчиков по модулю k и вторым входом фор-, мирователя переносов, выход формирователя переносов соединен со счетным

1410281

Составитель О. Неплохов

Техред М. Ходанич

Редактор Н. Горват

Корректор О. Кравцова

Заказ 3497/58

Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул, Проектная, 4 входом блока счетчиков по модулю р, выход которого соединен с вторым входом блока сумматоров по модулю р и является выходом устройства, установочный вход регистра сдвига, управляющие входы j x входных регистров (j

0 2,...,k-1), входы обнуления счетчика по модулю k и блока счетчиков по модулю р объединены и подключены к управляющему входу устройства, вход сдвига регистра сдвига объединен со счетным входом счетчика по модулю k и подключен к тактовому входу устрой

1 ства.