Устройство для умножения

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при конвейерной обработке знакоразрядных чисел, позволяющей представлять операнды и получать результат их обработки последовательно старшими разрядами вперед. Целью изобретения является повышение быстродействия . Поставленная цель достигается тем, что в устройство для умножения , содержащее два элемента 1,2 задержки, знакоразрядный сумматор 3, группу операционных модулей 4, содержащих каждый по шесть триггеров 6-11, четыре элемента И-ИЛИ 12-15 и элемент 5 задержки, дополнительно вводятся четыре элемента НЕ 35-38, а в каждый операционный модуль - по четыре знакоразрядных полусумматора 39-42 с соответствующими связями. I ил., 2-табл. а

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (51) 4 G 06 F 7/49

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К А BTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 4179417/24-24 (22) 12.01.87 (46) 23.07.88. Бюл. Р 27 (71) Институт проблем моделирования в энергетике АН УССР (72) В.В.Аристов и Н.Н.Можчиль (53) 681.325(088.8) (56) Авторское свидетельство СССР

В 1256016, кл. G 06 F 7 /49, 1984.

Авторское свидетельство СССР

Р 1013946, кл. G 06 F 7/49, 1981. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ (57) Изобретение относится к вычислительной технике и может быть использовано при конвейерной обработке энакораэрядных чисел, позволяющей представлять операнды и получать результат их обработки последовательно старшими разрядами вперед. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что в устройство для умножения, содержащее два элемента 1,2 задержки, знакоразрядный сумматор 3, группу операционных модулей 4, содержащих каждый по шесть триггеров

6-11, четыре элемента И-ИЛИ 12-15 и элемент 5 задержки, дополнительно вводятся четыре элемента НЕ 35-38, . а в каждый операционный модуль — по четыре знакораэрядных полусумматора 39-42 с соответствующими связями. ! ил,, 2.табл.

1411733

ll0

В каждом модуле 4 седьмой вход

27 со:-д п ен через элемент 5 задержки с тактирующими входами третьего 8 и четвертого 9 триггеров модуля 4 и с первым выходом 28 модуля 4, Инфор- 35 мационные входы первого 6 и второго

7 триггеров соединены соответственно с первым 18 и вторым 19 входами модуля 4. Прямой выход первого триггера 6 соединен с первыми входами 40 первых групп первого 12 и второго 13 элементов И-ИЛИ, первые входы вторых групп которых соединены с прямым выходом второго триггера 7, Прямой выход третьего триггера 8 соединен с первыми входами первых групп третьего 14.и четвертого 15 элементов

И-ИЛИ, первые входы вторых групп которых соединены с прямым выходом четвертого триггера 9, Первый вход 18 модуля соединен с вторым входом первой группы третьепо элемента И-ИЛИ 14 и с вторым входом второй группы четвертого элемента

И-ИЛИ 15, Второй вход 19 модуля сое55 динен о вторым входом второй группы третьего элемента И-ИЛИ l4 и с вторым входом первой группы четвертого элемента И-ИЛИ 15, Выходы пятого 10

Изобретение относится к вычисли,тельной технике и может быть использовано при конвейерной поразрядной обработке операндов, представленных

5 в избыточной знакоразрядной системе счисления (ИЗСС) с 1,0,7.

Цель изобретения — повьппение быстродействия.

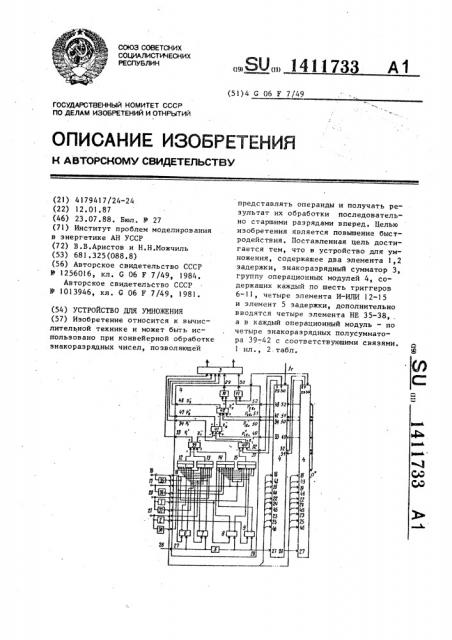

На чертеже представлена схема устройства для умножения.

Устройство содержит первый 1 и второй 2 элементы задержки, знако- разрядный сумматор 3, операционные модули 4, каждый из которых содержит элемент 5 задержки, шесть триггеров. 6 " 11, четыре элемента И-ИЛИ

l2 - 15. Причем первый 16 и второй

l? входы множимого устройства соединены соответственно с первыми 18 и . вторыми 19 входами модулей 4, первый

20 и второй 21 входы множителя устройства соединены соответственно с третьими 2" и четвертыми 23 .входами модулей 4 и через элементы 1 и 2 задержки соответственно с пятым 24 и шестым ?5 входами модулей 4, вход . 26 запуска устройства соединен.с седьмым входом 2? модуля 4 старшего разряда. 30 и шестого 11 триггеров соединены соответственно с вторым 29 и третьим

30 выходами модуля 4. Первый выход

28 модуля 4 каждого разряда, начиная со старшего, соединен с седьмым входом 27 модуля 4 разряда, младшего на единицу. Второй 29 и третий

30 выходы модуля 4 каждого разряда, кроме старшего., соединены соответственно с восьмым 31 и девятым 32 входами модуля, 4 разряда, следующего по старшинству, Второй 29, третий 30, четвертый

33 и пятый 34 выходы модуля 4 старшего разряда соединены соответственно с первым, вторым, третьим и четвертым входами знакоразрядного сумматора 3, выходы которого являются выходами устройства. Восьмой 31 и девятый 32 входы модуля 4 старшего разря-

pà соединены с входом нулевого потенциала устройства.

Кроме того, устройство содержит .четыре элемента НЕ 35 — 38, а в каждом модул" 4 по четыре знакоразряд ных полусумматора 39 — 42, причем входы первого 35, второго 36, третьего. 37 и четвертого 38 элементов 1Й соединены соответственно с первыми

18, вторыми 19, треть|ми 22 и четвертыми 23 входами модулей 4, а выходы — соответственно с десятыми 43, одиннадцатыми 44, двенадцатыми 45 и тринадцатыми 46 входами модулей 4, Шестой 47 и седьмой 48 выходы модуля .4 старшего разряда соединены со" ответственно с, пятым и шестым вхо-. дами знакоразрядного сумматора 3.

Четвертый. 33, пятый 34, шестой 47 и седьмой 48 выходы модуля 4 каждого разряда соединены соответственно с четырнадцатым, пятнадцатым, шестнадцатым и семнадцатым входами 49—

r э 2 модуля 4 следующего по стар." шинству разряда. Четырнадцатый, пят" . надцатый, шестнадцатый и семнадцатый входы 49 — 52 соответственно модуля 4 младшего разряда соединены с входом нулевого потенциала устройства, !

Причем в модуле 4-тактирующие вхс, ды первого 6 и второго 7 триггеров соединены с седьмым входом 27 модуля 4. Инверсный выход первого триггера 6 соединен. с вторыми входами вторых групп первого 12 и второго

13 элементов. И-ИЛИ, инверсный выход второго триггера 7 — -с вторыми вхо1411733

50 дами первых групп первого 12 и второго 13 элементов И-ИЛИ, инверсный выход третьего триггера 8 — с третьими входами вторых групп третьего 14 и четвертого 15 элементов И-ИЛИ, ин5 версный выход четвертого триггера

9 - с третьими входами первых групп третьего 14 и четвертого 15 элементов И-ИЛИ. Третьи входы первой группы первого элемента И-ИЛИ 12 и второй группы второго элемента И-ИЛИ 13 соединены с третьим входом 22 модуля 4, четвертый вход 23 которого сое- . динен с третьими входами второй груп- 5 пы первого элемента И-ИЛИ 12 и первой группы второго элемента И-ИЛИ 13, Четвертые входы второй группы первого элемента И-ИЛИ 12 и первой группы второго элемента И-HJIH 13 соединены с двенадцатым входом 45 модуля 4, тринадцатый вход 46 которого соединен с четвертыми входами первой группы первого элемента И-ИЛИ 12 и второй группы второго элемента И-ИЛИ 13. Де-25 сятый вход 43 модуля 4 соединен- с четвертыми входами второй группы ! третьего элемента И-ИЛИ 14 и первой. группы четвертого элемента И-ИЛИ 15, одиннадцатый вход 44 модуля 4 — с четвертыми входами первой группы третьего элемента И-ИЛИ 14 и второй группы четвертого элемента И-ИЛИ 15.

Информационные входы третьего 8 и четвертого 9 триггеров модуля 4 соединены соответственно с пятым 24 и. шестым 25 входами модуля 4. Первый, второй и третий входы первого знако" разрядного полусумматора 39 соединены с выходами соответственно первого, второго и третьего элементов

И-ИЛИ 12 — 14, а первый, второй и третий входы второго знакоразрядного полусумматора 40 — соответственно с выходом четвертого элемента И-ИЛИ 15, восьмым 31 и девятым 32 входами мо45 дуля 4. Первые выходы первого 30 и второго 40 знакоразрядного полусумматоров соединены соответственно с четвертым и пятым 34 выходами модуля 4. Первый, второй и третий входы третьего знакоразрядного полусумматора 41 соединены соответственно с вторыми выходами первого 39 и второго 40 знакоразрядных полусумматоров и четырнадцатым входом 49 модуля 4.

Первый выход третьего знакоразрядного полусумматора 41 соединен с шестым выходом 47 модуля 4, а первый, второй и третий входы четвертого знакоразрядного полусумматора 42 — соответственно с вторым выходом третьего знакоразрядного полусумматора 41, пятнадцатым 50 и шестнадцатым 51 входами модуля 4. Первый выход четвертого знакоразрядного полусумматора

42 соединен с седьмым выходом 48 модуля, второй выход четвертого знакоразрядного полусумматора 42 — с информационным входом пятого триггера 10. Семнадцатый вход 52 модуля 4 соединен с информационным входом шестого триггера ll, Элементы l, 2 и 5 задержки выполняют задержку на один такт.

Устройство работает следующим образом, По первым входам множимого 16 и множителя 20 поступают положительные коды. разрядов знакоразрядных операндов, по вторым входам 17 и 21 отрицательные (коды множимого А и множителя В), последовательно разряд за разрядом, начиная со старшего.

Результат на выходах устройства получается также последовательным знакоразрядным кодом, начиная со старшего разряда. Задержка, вносимая устройством„ - три такта. С входа 26 устройства на тактирующие входы триггеров 6 и 7 модуля 4 старшего (первого) разряда поступает импульс, определяющий занесение в первом такте старшего разряда множимого А„ на информационные входы триггеров 6 и 7 всех модулей поступают текущие значения положительных и отрицательных разрядов множимого, Далее, проходя по цепи, состоящей из последовательно включенных элементов 5 потактной задержки всех модулей, единичный импульс разрешает поочередное занесе" ние разрядов множимого в триггеры 6 и 7 модулей соответствующих разрядов.

На тактирующие входы триггеров 8 и 9 модулей 4 старшего разряда управляющий сигнал йоступает во втором такте (с выхода элемента 5 задержки модуля). На информационные входы триггеров 8 и 9 модулей всех разрядов последовательный код множителя В поступает задержанным на один такт элементами 1 и 2 задержки. Таким образом, первый разряд множимого записывается в триггеры

6 и 7 модуля первого разряда на

1411733

Таблица 1

Число Х

Знакораэрядное представление Х О(1) 1 0

Х 0(1) 0 1

1О

При знакораэрядном кодировании выражение (1) принимает вид:

15 (А В); = (А В) + + (атЬ1) + (атЬ! ) +

+ (а „bт) (А В). +

4 (А ° В) -+< +

20+(a; b) (2) Знакораз рядно е представление чи-. сел, характеризуемое ограниченной

25 глубиной переноса при суммировании, позволяет поразрядную обработку при умножении согласно выражению (2) выполнять на одинаковых модулях 4. При этом члены (А В); „ и (А В)1, поступают в качестве первого и второго слагаемого выражения (2) на входы 31 и 32 модуля i-го разряда с выходов

29 и 30 модуля 4 (i + 1)-го (младшего на единицу) разряда. Слагаемые (а;Ьт), (а„Ь ), (атЬ1)+ и (атЬ1)" формируются на выходах соответственно первого, второго, третьего и четвертого элементов И-ИЛИ 12 — 15 модуля 4 согласно выражениям (аЬ) =а".Ь а Ь ч (а, b ) = а+! Ь . - а.! - Ь (а Ь ) = ат Ь! а; Ь,. (ат - Ь1) = a+ Ь! ° a .b+; дуля 4 младшего разряда двух знако" разрядных .переносов Р,в„ и Р „ — на третьем 41 и четвертом 42 знакораз"

50 рядных полусумматорах модуля 4.

Полусумматоры 39 и 41 формируют значения положительного переноса P u отрицательной суммы Z при дЪух положительных х+, у+ и одном отрицательном х слагаемых, а энакоразрядные полусумматоры 40 и 42 производят формирование отрицательного переноса P и положительной суммы Z при двух отрицательных х, у и одпервом такте работы устройства, а первый разряд множителя — в триггеры 8 и 9 модуля первого разряда на втором такте, тогда же, когда и второй разряд множимого в соответствующие триггеры модуля второго разряда и т.д. Такая организация занесения позволяет, преобразовывая последовательный код операндов в па-, раллельный и запоминая его в триггерах 5 - 8, формировать значения а и Ь;, соответствующие состояниям триггеров 6 — 9 модуля i-ro разряда, позволяющие процедуру умножения поразрядно поступающих операндов свести к поразрядному суммированию в соответствии с выражением: (А В); = (А B);+„+ атЬ;+ а,.Ьтэ (1) где (А В); - значение i-го разряда произведения в текущем такте Т; (А ° В);, - значение (i + 1)-ro (младшего) разряда в предшествующем такте

Т-1

a» b - текущие значения разрядов множимого и множителя (в так те Т); а;, Ь; - состояния триггеров множимого и множителя в текущем такте Т.

При энакоразрядном кодировании в двоичной системе счисления с цифрами 1, О, 1 каждый разряд числа представляется совокупностью положительной и отрицательной частей в соответствии с табл. 1.

Члены с черточкой наверху — инверс° ные значения соответствующих сигналов, получаемые для текущих значений а и Ь. с выходов элементов

НЕ 35 — 38, для сигналов а и Ъ;— с инверсных выходов соответствующих триггеров.

Суммирование трех знакораэрядных чисел согласно выражению (2) производится параллельно на первом

39 и втором 40 знакоразрядных полусумматорах модуля 4, а формирование разряда с учетом поступающих иэ моа; -Ь "а+; Ь,.; (3)

v a;- Ь a1. b; (4)

-Ча b+,.а+ b!,1 ;(5) чат b+ . а+Ь;, (6) Входы

Выходы

7 ном .положительном х+ слагаемых (см. табл. 2).

Т а б л и ц а

1411733 однородности устройства н воэможности использования кодировки нулевого значения разряда совокупностью единичных сигналов положительной и отрицательной частей. х+/х у+/у х /х+

0 О

О 1

О.

О

1 О

1 1

О 0

О 1.

О

О

О

1 О

1 1

Математические знаки переменных, соответствующие входным и выходным сигналам знакоразрядных полусумма- . З0 торов, показань1 на чертеже.

Ф

Сигналы выходных переносов Р„, Р знакоразрядных полусумматоров 39—

42 модуля 4 поступают на выходы модуля 4 для использования их в качестве входных сигналов Р1 „, Р> „ в модуле следующего по старшинству разряда.. Положительное и отрицательное значения х-га разряда, сформированные на втором выходе четвертого зна- 40 коразрядного полусумматора 42 и на семнадцатом входе 52 модуля 4 по истечение времени, необходимого для работы полусумматоров модуля 4, в текУшем такте по синхРоимпУльсУ Ет 45 заносятся в триггеры 10 и 11. Сигналы с выходов триггеров 10 и ll модуля 4 старшего разряда, а также сигналы выходных переносов модуля 4 старшего разряда поступают на вход 50 трехвходового последовательного знакоразрядного сумматора 3, который формирует разряд за разрядом результат вычислений. Задержка, вносимая трехвходовым последовательным знакоразрядным сумматором, — два такта.

Дополнительный положительный эффект изобретения заключается в расширении области применения эа счет

Формула изобретения

Ъ

Устройство для умножения, содержашее первый и второй элементы задержки, знакоразрядный сумматор и и (n - число разрядов в перемножае-. мых операндах) операционных модулей, каждый из которых содержит элемент задержки, шесть триггеров и четыре элемента И-ИЛИ, причем первый и второй входы множимого устройства соединены соответственно с информационными входами первого и второго триггеров каждого операционного модуля, первый и второй входы умкожителя. уст- . ройства соединены соответственно с входами первого и второго элементов задержки, выходы которых соединены соответственно с информационными входами третьего и четвертого триггеров каждого операционного модуля, вход запуска устройства соединен с .входом элемента задержки операционного модуля старшего разряда> выходы пятого и шестого триггеров которого соединены соответственно с первым и вторым входами знакоразряднога сумматора, выход которого является выходом устройства, тактовый вход которого соединен с тактируюшими входаь и пятого и шестого триггеров каждого операционного модуля, выход элемента задержки k-ro операционного модуля (k = 1,..., n — 1) соединен с входом элемента задержки (k + 1)-го операционного модуля, причем в операционном модуле выход элемента задержки соединен с тактируюшими входами третьего и.четвертого триггеров, прямой выход первого триггера соединен с первыми входами первых rpyrfrr первого и второго элементов И-ИЛИ, первые входы вторых групп которых соединены с прямым выходом второго триггера, прямой выход третьего триггера соединен с первыми входами первых групп третьего и четвертого элементов

И-ИЛИ, первые входы вторых групп которых соединены с прямым выходом четвертого триггера, информационный вход первого триггера соединен с вторым входом первой группы третьего элемента И-ИЛИ и с вторым входом вто1411733

Редактор В. Петраш

- акаэ 3655/44 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4f5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 рой группы четвертого элемента И-ИЛИ, информационный вход второго триггера соединен с вторым входом второй группы третьего элемента И-ИЛИ и вторым

5 входом первой группы четвертого эле мента И-ИЛИ о т л и ч а ю щ е е с я

Ф тем, что, с целью повышения быстро,действия, оно содержит четыре элемен та НЕ, а каждый операционный модуль

,содержит четыре знакоразрядных полу, сумматора, причем первый и второй входы ! множимого первый и второй входы мно жителя устройства соединены соответственно с входами элементов НЕ с пер- 15 вого по четвертый, первые выходы зна,коразрядных полусумМаторов с первого по четвертый операционного модуля старшего разряда соединены соответственно с входами с третьего по шестой знакоразрядного сумматора, выходы пято,o и шестого триггеров, первые выходы знакоразрядных полусум маторов с первого по четвертый

l(k + 1)-го операционного модуля сое- 25 инены соответственно с первым и торым входами второго знакоразрядюго полусумматора, с первым вхоом третьего знакоразрядного полуумматора, с первым и вторым входаи четвертого знакоразрядного полу умматора и с информационным входом естого триггера k-го операционного . одуля, первый и второй входы второо знакоразрядного полусумматора, первый вход третьего знакоразрядного

1 олусумматора, первый и второй вхоы четвертого знакоразрядного полу умиатора и информационный вход шестого триггера п-ro операционного мо40

« уля соединены с входом нулевого по енщиала устройства, первый и второй входъ множителя устройства соедине ы соответственно с вторыми входами

Первой и второй групп первого эле45 1ента И-ИЛИ каждого операционного

Модуля, выходы элементов И с первого г(о четвертый соединены соответственНо с третьим входом второй группы т ретьего элемента И вЂ И, с третьим 1ходом первой группы третьего эле50

Составитель A. Кл

Техред М.Ходанич мента И-ИЛИ, с третьим входом второй группы первого элемента И-ИЛИ и с третьим входом первой группы первого элемента И-ИЛИ каждого операционного модуля, причем в операционном модуле вход элемента задержки соединен с тактирующими входами первого и второго триггеров, второй и третий входы первой группы первого элемента

И-ИЛИ соединены соответственно с вторым и третьим входами второй группы второго элемента И-ИЛИ, второй и третий входы второй группы первого элемента И-ИЛИ соединены соответственно с вторым и третьим входами первой группы второго элемента И-ИЛИ, третьи входы первой и второй групп третьего элемента И-ИЛИ соединены соответственно с третьими входами второй и первой групп четвертого элемента

И-ИЛИ, инверсный выход первого триггера соединен с четвертыми входами вторых групп первого и второго эле-. ментов И-ИЛИ, инверсный выход второго триггера соединен с четвертыми входами первых групп первого и вто- . рого элементов И-ИЛИ, инверсный выход третьего триггера соединен с четвертыми входами вторых групп третье- . го и четвертого элементов И-ИЛИ, инверсный выход четвертого триггера соединен с четвертыми входами первых групп третьего и четвертого элементов

И-ИЛИ, первый, второй и третий входы первого знакоразрядного полусумматора соединены с выходами соответственно первого, второго и третьего элементов

И-ИЛИ, третий вход второго знакоразрядного полусумматора соединен с выходом четвертого элемента И-ИЛИ, вто" рой и третий входы третьего знакоразрядного полусумматора соединены соответственно с вторыми выходами первого и второго знакоразрядных полусумматоров, второй выход третьего знакоразрядного полусумматора соединен с третьим входом четвертого знакоразрядного полусумматора, второй выход которого соединен с информационным входом пятого триггера. юев

Корректор Л, Пилипенко