Комбинационный сумматор

Иллюстрации

Показать всеРеферат

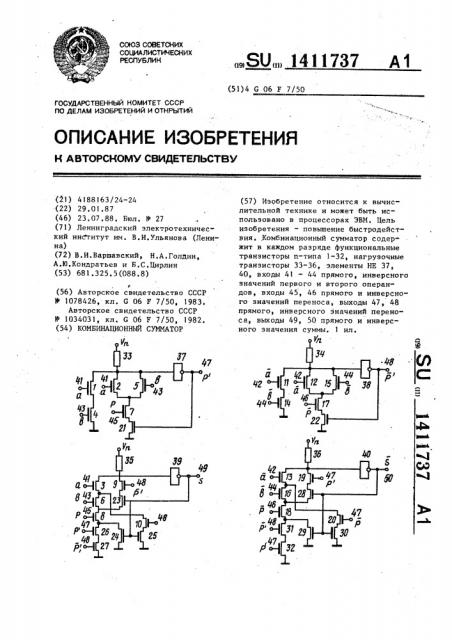

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ. Цель изобретения - повышение быстродействия . Комбинационный сумматор содержит в каждом разряде функциональные транзисторы п-типа 1-32, нагрузочные транзисторы 33-36, элементы НЕ 37, 40, входы 41-44 прямого, инверсного значений первого и второго операндов , входы 45, 46 прямого и инверсного значений переноса, выходы 47, 48 прямого, инверсного значений переноса , выходы 49, 50 прямого и инверсного значения суммы. 1 ил. с/) /Hffl П СдЭ

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51)4 С 06 Р 7/50

ОПИСАНИЕ ИЗОбРЕТЕНИЯ

Н A BTOPCHOMY СВИДЕТЕЛЬСТВУ а

92 Ч фЦ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4 88 63/24-24 (22) 29.0! .87 (46) 23.07.88. Бюл. Р 27 (71) Ленинградский электротехнический ин гитут им. В.И.Ульянова (Ленина) (72) В.И.Варшавский, Н.А,Голдин, А.Ю.Кондратьев и Б.С.Цирлин (53) 681.325.5(088.8) (56) Авторское свидетельство СССР

В 1078426, кл. С 06 F 7/50, 1983.

Авторское свидетельство СССР

Р 1034031, кл. 6 06 F 7/50, 1982. (54) КОМБИНАЦИОННЫЙ СУММАТОР

ÄÄSUÄÄ 1411737 А1 (57) Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ. Цель изобретения — повышение быстродействия. Комбинационный сумматор содержит в каждом разряде функциональные транзисторы и-типа 1-32, нагрузочные транзисторы 33-36, элементы НЕ 37, 40, входы 4! — 44 прямого, инверсного значений первого и второго операндов, входы 45, 46 прямого и инверсного значений переноса, выходы 47, 48. прямого, инверсного значений переноса, выходы 49, 50 прямого и инверсного значения суммы. 1 ил.

1t

1411737

Изобретение относится к вычислительной технике и может быть исполь1

, эовано в процессорах 3ВМ.

Цель изобретения — увеличение быстродействия, На чертеже представлена функциональная схема одного разряда комбинационного сумматора.

Комбинационный сумматор в каждом 10 ! разряде содержит функциональные транзисторы п-типа 1"32, нагрузочные транзисторы 33-36, элементы НЕ 3740, входы 41-44 (а, а и Ь, Ь} пря.мого и инверсного значений первого и второго слагаемых, входы 45 и 46 (р, р) прямого и инверсного значений переноса иэ предыдущего разряда, выходы 47 и 48 (р, р ) прямого и инверсного значений переноса в следующий разряд, выходы 49 и 50 (s, s) прямого и инверсного значений суммы ! данного разряда (сигналы завершения

| переходных процессов в сумматоре). (Сумматор работает следующим обра- 25 зом.

Инертное состояние схемы характе" риэуется значением 1 на всех ее вхо, дах и выходах: а = а = Ь = Ь = р р = р = р = з = з = 1. При этом 30 все .транзисторы 21-32 открыты.и, ес-! ли на входах сумматора устанавливается единичный рабочий набор: a = Ь = = р = 1 и а = Ь = р = О, то транзисторы 1"8 остаются открытыми, на входах элементов HE 37 и 39 сохраняется, 35 значение О, а на их выходах, т.е. выходах р и s - значение 1, а тран-, зисторы 11-18 закрываются, на входах элементов НЕ 38 и 40 появляются эна- 40 чения 1, а на их выходах, т.е. выходах р и s, — значения 0, которые закрывают транзисторы 22 и 28-30. При переходе схемы в инертное состояние значение. О на входе элемента НЕ 38 появляется только после того, как откроются транзисторы 11 и 14, т.е. после того, как в инертное состояние возвратятся входы а и Ь. После этого на выходе элемента НЕ 38 появляется значение

1, т.е. выходы р и р схемы оказываются в инертном состоянии, в результате чего открываются не только транзисторы 13,26 и 18, но и 31 и 32 и на входе элемента НЕ 40 появляется значение О, а на его выходе, .т.е. выходе s - значение 1, схема возвращается в инертное состояние.

Если на входах сумматора устанавливается нулевой рабочий набор: а =

= Ь р О и а = b = р = 1, то транзисторы 11-18 остаются открытыми, на входах элементов НЕ 38 и 40 сохраняются значения О, а на их выходах,. т.е. выходах р и s, — значение 1, а транзисторы 1-8 закрываются и на входах элементов НЕ 37 и 39 появляются значения 1, а на их выходах, т.е. выходах р и в, — значения О, которые закрывают транзисторы 21 и 23-25. При переходе схемы в инертное состояние значение О на входе элемента НЕ 37 появляется только после того, как открываются транзисторы 1 и 4, т.е. после того, как в инертное состояние возвращаются входы а и Ь. После этого на выходе элемента НЕ 37 появляется значение 1, — c ( т. е. выходы р . и р схемы. оказываются в инертном состоянии, в резуль" тате чего открываются не только транзисторы 3,6 и 8, но и 26 и 27 и на входе элемента НЕ 39 появляется зна" чение О, а на его выходе, т.е. выхо" де s - значение 1, схема возвращается в инертное состояние.

Если на входах сумматора устанав-, ливается рабочий набор, в котором значение 1 сохраняется на одном пря-. мом и, соответственно, на двух инверсных выходах, например а = b = р 1 и а = Ь р = О, то на входах элементов НЕ 38 и 39 сохраняются значения О,.а на их выходах, т.е.

-I выходах р и s, — значения 1, а на выходе элемента НЕ 37 появляется значение 1 и на его выходе, т.е. выходе р . — значение О. После

Ф этого закрываются транзисторы 19 и

20, на входе .элемента НЕ 40 появляется значение l, а на его выходе, т.е. выходе з - значение О. Эти зна" чения на выходах р и з закрывают транзисторы 21 и 28-30. При переходе в инертное состояние значение О на входе элемента НЕ 37 появляется только после того, как открываются транзисторы 1 и 4, т.е. после того, как в инертное состояние возвращаются входы а и Ь. После этого на выходе элемента НЕ 37 появляется значение 1, т.е. выходы р и р схемы оказываются в инертном состоянии, в результате чего открываются транзисторы 21 и 32. Значение О на входе. элемента НЕ 40 появляется после того, !

4!!7

3 как открываются транзисторы 13, 16 и !8, т.е. после того, как в инертное состояние возвращаются входы а, Ъ и р. В результате на выходе элемента HE 40, т.е. выходе з, появляется значение 1, схема возвращается в инертное состояние.

Если на входах сумматора устанавливается рабочий набор, в котором значение 1 сохраняется на двух прямых и одном инверсном входах, например а = Ь = р = и а = Ь = р - О, то на входах элементов HE 37 и 40 сохраняется значение О, а на их выходах, 5 т.е. выходах р и s — значения 1, на входе элемента НЕ 38 появляется значение 1, на его выходе, т.е. выходе р, — значение О. После этого закрываются транзисторы 9 и 10, на входе элемента НЕ 39 появляется значение 1, à íà его выходе, т.е. выходе s - значение О. Эти значения на выходах р и s закрывают транзисторы 22-25. При переходе в инертное состояние значение О на входе элемента НЕ 38 появляется только после того, как открываются транзисторы 11 и 14, т.е. после того, как в инерт" ное состояние возвращаются входы

30 а и Ь. После этого на выходе элемента НЕ 38 появляется значение !, т.е. выходы р и р схемы оказываются в инертном состоянии, в результате чего открываются,транзисторы 26 и 2? °

Значение О на входе элемента НЕ 39 появляется после того, как открыва:ются транзисторы 3,6 и 8, т,е. после того, как в инертное состояние возвращаются входы а, Ь и р. В результате на выходе элемента НЕ 39, т.е. вы" ходе s, появляется значение 1, схема возвращается в инертное состояние.

Таким образом, рабочее состояние выходов s и в суммы данного разряда .появляется только после того, как .все его входы (в том числе и переноса из предыдущего разряда) перейдут из инертного в рабочее состояние.

При этом рабочее состояние на выходах ( р и р переноса в следующий разряд могут вырабатываться и до этого (на нулевом и единичном рабочих наборах) °

В этом случае признаком завершения переходных процессов при переходе в рабочее состояние данного разряда 55 является переход в рабочее состояние выходов в и s суммы не только данного, но и следующего разрядов. Пере37 4 ход выходов з и s суммы данного разряда в инертное состояние происходит только после того, как на всех его входах установится инертное состояние и выходы р и p переноса в следующий разряд также перейдут в инертное состояние, т.е. по завершении в нем переходньм процессов.

Формула изобретения

Комбинационный сумматор, содержащий в каждом разряде десять.функцио" нальных транзисторов п-типа, четыре нагрузочных транзистора, причем затворы первого, второго, третьего функциональных транзисторов соединены с входом прямого значения первого операнда сумматора, затворы четвертого, пятого, шестого функциональных транзисторов соединены с входом прямого значения второго операнда сумматора, затворы седьмого и восьмого функциональных транзисторов соединены с входом прямого значения переноса сумматора, затворы девятого и десятого транзисторов соединены с вьмодом инверсного значения переноса сумма.тора, сток первого функционального транзистора соединен с истоком четвертого функционального транзистора, сток которого соединен с шиной нулевого потенциала сумматора, сток второго функционального транзистора соединен со стоком пятого функционального транзистора, сток третьего функ ционального транзистора соединен с истоком. шестого функционального транзистора,. сток которого соединен с истоком восьмого функционального транзистора,.о т л и ч а ю ш и и с я тем, что, с целью увеличения быстродействия, в каждый разряд введены четыре элемента НЕ и двадцать два функциональных транзистора п-типа, причем затворы одиннадцатого, двенад" цатого и тринадцатого функциональных транзисторов соединены с входом инверсного значения первого операнда сумматора, затворы четырнадцатого, пятнадцатого, шестнадцатого функциональных транзисторов соединены с входом инверсного значения второго операнда сумматора, затворы семнадцатого, восемнадцатого функциональных транзисторов соединены с входом инверсного значения переноса сумматора, затворы девятнадцатого, двадцато14! 1737

Составитель М, Есенина

Редактор В. Петраш Техред М,Ходанич Корректор Л. Патай

Заказ Зб55/44 Тираж 704

Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 го, двадцать первого, двадцать второго, двадцать третьего функциональных транэисторов соединены с выходом прямого значения переноса сумматора, стоки двадцать четвертого, двадцать пятого, двадцать шестого функциональных транзисторов соединены с выходом прямого значения суммы сумматора и выходом первого элемента НЕ, вход которого соединен с истоками третьего и девятого функциональных транзисторов и . через первый нагрузочный транзистор с шиной питания сумматора, затворы двадцать седьмого, двадцать восьмого, двадцать девятого функциональных транзисторов соединены с выходом инверсного значения переноса сумматора, затворы тридцатого, тридцать первого, тридцать второго функпиональ20 ных транзисторов соединены с выхо— дом инверсного значения суммы сумматора и выходом второго элемента НЕ, вход которого соединен с истоками тринадцатого, девятнадцатого функцинальных транзисторов и через второй агрузочный транзистор с шиной питаия сумматора, стоки четырнадцатого, вадцать первого, двадцать четвертоо, двадцать пятого, двадцать третьео, двадцать седьмого, двадцать девяого, тридцатого и тридцать первого ункциональных транзисторов соедине.ы с шиной нулевого потенциала суммаора, шина питания сумматора соединеа через третий нагрузочный транзис ор с истоками первого, второго, пяого функциональных транзисторов и ходом третьего элемента НЕ, выход

>, оторого соединен с затвором двадцать первого функционального транзистора, исток которого соединен со с тоКом седьмого функционального тран.1истора, исток которого соединен со

< током второго функционального тран:-1истора, сток третьего функционального транзистора соединен с истоком десятого функционального транэистора, сток которого соединен с истоком двадцать пятого функционального транзистора, сток девятого функционального транзистора соединен с истоком двадцать шестого функционального транзистора, сток которого соединен с истоком восьмого функционального транзистора, сток которого соединен с истоком двадцать четвертого функционального транзистора и двадцать второго функционального транзистора, сток которого соединен с истоком двадцать седьмого функционального транзистора, шина питания сумматора через четвертый нагруэочный транзистор соединена с истоками одиннадцато- го, двенадцатого, пятнадцатого функциональных транзисторов и входом четвертого элемента HF., выход которого соединен с затвором двадцать девятого функционального транзистора, исток которого соединен со стоком семнадцатого функционального транзистора, исток которого соединен- со стоками пятнадцатого и двенадцатого функциональных транзисторов, исток четырнадцатого функционального транзистора соединен со стоком одиннадцатого функционального транзистора, сток девятнадцатого функционального транзистора соединен с истоком тридцать второго функционального транзистора, сток которого соединен с истоком восемнадцатого и стоком шестнадцатого функционального транзистора, исток которого соединен со стоком тринадцатого и истоком двадцатого функционального транзистора, сток которого соединен с истоком тридцатого». функ-. ционального транзистора, сток восем" надцатого функционального транзис-. тора соединен с истоком тридцать первого и истоком двадцать восьмого функционального транзистора, сток которого соединен с истоком двадцать третьего функционального транзистора,