Многоканальное устройство переменного приоритета

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в системах прерьшания для уменьшения числа линий связи. Цель изобретения - упрощение устройства за счет уменьшения числа линий связи между каналами. Устройство содержит регистр сдвига, два триггера, два элемента И, а в канале - регистр, дешифратор, блок задержек, группу элементов И, элемент ИЛИ, элемент И. В устройство время задержки блока задержек каждого канала соответствует номеру канала, что позволяет регистру сдвига определять номера каналов по промежутку времени между посылкой импульса опроса, подаваемого на вход блока задержек каждого , и приходом на вход регистра сдвига импульсов , задержанных на блоках задержек каналов, имеющих запросы на прерывас ния, 1 ил.

„„Я1„1„„1411747 д 1

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

1511 4 С 06 Р 9/46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4165171/24-24 (22) 23.12.86 (46) 23.07.88. Вюл. И 27 (72) В.И. Макаров, С.И. Штанько и С.N. Кастерский (53) 681.325(088.8) (56) Авторское свидетельство СССР

Р 512470, кл. G 06 F 9/46, 1973.

Авторское свидетельство СССР

9 9058!9, кл. G 06 F 9/46, 1980. (54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА (57) Изобретение относится к вычислительной технике и может быть использовано в системах прерывания для уменьшения числа линий связи. Цель изобретения — упрощение устройства эа счет уменьшения числа линий связи между каналами. Устройство содержит регистр сдвига, два триггера, два элемента И, а в каждом канале " регистр, дешифратор, блок задержек, группу элементов И, элемент ИЛИ, элемент И.

В устройство время задержки блока задержек каждого канала соответствует номеру канала, что позволяет регистру сдвига определять номера каналов по промежутку времени между посылкой импульса опроса, подаваемого на вход блока задержек каждого кАнала, и приходом на вход регистра сдвига импульсов, задержанных на блоках задержек каналов имеющих запросы на прерыва1 ния. 1 ил.

141 l 747

Изобретение относится к вычислительной технике, в частности к системам прерываний, и может быть использовано в системах обработки информа5 ции для организации обмена по запросам каналов.

Цель изобретения — упрощение устройства за счет уменьшения числа линий связи между каналами. !О

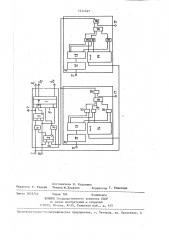

На чертеже приведена структурная схема устройства.

Устройство содержит регистр 1 сдвига, вход 2 опроса, триггер 3, элементы И 4 и S,òðèããåð 6, сигнальный вы- 15 ход 7, тактовый вхоц 8, информационные выходы 9, каналы 10, кодовые входы ll, регистр 12, дешифраторы 13, блоки 14 задержек, группу элементов

И !5„ элемент ИЛИ 16, запросные вхо- 20 ды 17, элементы И 18 и вход 19 сброса.

Устройство работает следующим образом.

Предварительно триггеры 3 и 6 и регистр 1 обнуляются, а сигналы с выхо- 25 дов триггера 6 приводят регистр 1 в режим последовательной записи.

В регистр 12 каждого канала 10 заносится двоичный код номера приоритета, который присваивается запросу ЗО данного канала 10. На одном из выходов каждого дешифратора 13 появляется сигнал, который поступает на один иэ соответствующих элементов И 15 группы, подготавливая их к срабатыванию.

В канале с приоритетом адин сигнал поступает на вход первого элемента

И 15 группы, в канале с приоритетом ! два — на вход второго элемента И 15 группы и т.д. 40

На вход 2 опроса подается импульс опроса, определяющий цикл работы устройства, а на входе 8 появляется серия импульсов синхронизации. Количество импульсов синхронизации в каждой се- 4,5 рии равно числу каналов.

Импульс опроса, определяющий нулевой такт первого цикла, поступает на первый вход элемента И 4, на втором входе которого находится нулевой сиг-50 нал с прямого выхода триггера 3. Кроме того, импульс опроса поступает в каждом канале 10 на вход блока !4 задержек. Время задержки каждого выхода блока 14 подобрано так, что время подачей импульса опроса и его приходом на информационный вход регистра

1 равно целому числу тактов синхронизации. Чем ниже приоритет канала, тем на большее число тактов должен быть задержан импульс опроса в этом . канале.

В канале с приоритетом один с первого выхода элемента задержки импульс поступает на первый элемент И 15 группы своего канала, а канале в приоритетом два — на второй и т.д.

Указанные элементы И 15 групп открыты сигналами с дешифраторов 13, поэтому задержанные в каждом канале на разные промежутки времени импульсы проходят через соответствующие элементы И 15 групп и через элементы

ИЛИ 16 появляются на входе элемента

И 18 своего канала.

Пусть сигналы запросов на прерывание имеются на входах 17 пятого и всех последующих каналов ° Тогда .элементы И 18 этих каналов открыты и на информационном входе регистра 1 появляется серия импульсов.с объединенного выхода канал6в 10, причем появление первого импульса совпадает с пятым тактом синхронизации на выходе 8.

Импульс с объединенного выхода каналов 10 поступает на вход элемента И 5 и на единичный вход триггера 3, но так как триггер 3 находится в нулевом состоянии, элемент И 5 открыт и импульс проходит на информационный вход регистра 1.

Так как триггер 6 находится в нулевом состоянии, то регистр 1 готов к последовательному приему импульсов.

В следующем такте синхронизации в последний разряд регистра 1 записывает-. ся единица, триггер 3 переходит в единичное .состояние и сигналом с инверсного выхода закрывает элемент И 5, поэтому импульсы от каналов с младшими приоритетами (импульсы от шестого и последующих каналов) на вход регистра 1 не попадают. С каждым последующим тактом синхронизации содержимое регистра l смещается по направлению к первому разряду. В момент формирования последующего импульса опроса (в нулевой такт второго цикла) единица находится в пятом разряде регистра 1.

Так как триггер 3 нах6дится в единичном состоянии, элемент И 4 открыт и сигнал опроса устанавливает триггер

6 в единичное состояние. Сигналы с выхода триггера 6 переводят регистр 1 в режим параллельного хранения. В одном из разрядов регистра 1 (в данном

1411747 случае в пятом) хранится единица, занесенная каналом, имеющим запрос с самым высшим приоритетом, причем номер разряда совпадает с приоритетом этого канала. Сигнал с выхода 7 требует перехода к подпрограмме обслуживания запроса от канала, приоритет определяется содержимым регистра 1.

После перехода к подпрограмме об- 1п служивания запроса на вход 19 подается сигнал сброса, устанавливающий триггеры Э и 6 и регистр 1 в нулевое состояние. 1Io окончании действия этого сигнала устройство готово к об- 15 работке следующих запросов. Смену приоритетов каналов целесообразно осуществлять при наличии сигнала на входе 19.

Формула изобретения

Многоканальное устройство переменного п1йюритета, .содержащее каналы, а в каждом канале регистр, дешифра- 25 тор, группу элементов И, элемент ИЛИ, элемент И, причем каждая группа кодовых входов устройства соединена с группой информационных входов регистра одноименного канала, группа выхо-1 у1 дов регистра каждого канала соединена с группой входов дешифратора своего канала, каждый выход дешифратора канала соединен с первым входом соотВетствующего элемента И группы caoer o 35 канала, выходы элементов И группы в каждом канале соединены с входами элемента ИЛИ своего канала, выход элемента ИЛИ соединен с первым входом элемента И своего канала, о т л и-40 ч а ю щ е е с я тем, что, с целью упрощения устройства за счет уменьшения числа линий связи между каналами, устройство содержит два триггера, регистр сдвига, первый и второй элементы И, а в каждом канале — блок задержек, причем вход опроса устройства соединен с первым входом первого элемента И, вход сброса устройства соединен с входами сброса первого и второго триггеров и регистра сдвига, выходы элементов И каналов объединены через монтажное ИЛИ и соединены с единичным входом первого триггера и с первым входом второго элемента И, второй вход которого соединен с инверсным выходом первого триггера, выход второго элемента И соединен с информационным входом регистра сдвига, прямой выход первого триггера соединен с вторым входом первого элемента И, выход которого соединен с единичным входом второго триггера, прямой выход которого соединен с входом управления записью регистра сдвига, вход управления сдвигом которого соединен с инверсным выходом второго триггера, прямой выход которого является сигнальным выходом устройства, тактовый вход которого соединен с тактовым входом первого триггера и регистра сдвига, выходы которого являются информационными выходами устройства, вход опроса устройства соединен с входом блока задержек всех каналов, каждый выход блока задержек соединен с вторым входом одноименного элемента И группы своего канала, второй вход элемента И каждого из которых соединен с одноименным запросным входом устройства, 1411747

Составитель М. Кудряшев

Редактор П. Гереши Техред М,Ходанич Корректор Г. Решетник

Заказ 3655/44

Тираж 704 Подписное

В11ИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Мо"ква, Ж-35, Раушская наб,, д, 4/5

Производственно †полиграфическ предприятие, г. Ужгород, ул. Проектная,, 4