Устройство для проверки программ на сбоеустойчивость

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике, может быть использовано для проверки устойчивости к сбоям программ ЦВМ, имеющих средства аппаратурного контроля, и является усовершенствованием изобретения по а.с. № 1205148. Цель изобретения - расширение функциональных возможностей за счет возможности получения количественной оценки достоверности проверки. В устройство введены формирователь длительности импульсов 5 и три счетчика 9, П и 16 импульсов, 2 ил. с tS

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (11) (51) 4 С 06 Р 11/26

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Мод 4иач

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ (61) 1205148 . (21) 4169504/24-24 (22) 14.11.86 (46) 23,07.88. Бюл. Ф 27 (72) В.П.Конищев, А.А.Андреев и А.Н,Малица (53) 681 ° 3(088 ° 8) (56) Авторское свидетельство СССР

У 1205148, кл. G 06 F 11/26, 1986. (54 ) УСТРОЙСТВО ДЛЯ ПРОВЕ РКИ ПРОГРАММ НА СБОЕУСТОЙЧИВОСТЬ (57) Иэобретение относится к цифровой вычислительной технике, может быть испольэовано для проверки устойчивости к сбоям программ ЦВМ, имеющих средства аппаратурного контроля, и является усовершенствованием иэобретения по а.с. 11 1205148. Цель иэобретения — расширение функциональных воэможностей эа счет воэможности получения количественной оценки достоверности проверки. В устройство введены формирователь длительности импульсов 5 и три счетчика 9, 11 и 16 импульсов. 2 ил. Pg

1411753

Изобретение относится к цифровой вычислительной технике, может быть использовано для проверки устойчивости к сбоям программ ЦВМ, имеющих сред-5 ства аппаратурного контроля и программную защиту от сбоев, организованную путем разбиения программ на ( контролируемые учас тки, допускающие повторное исполнение после сбоя, и является усовершенствованием изобретения по авт.св. У 1205148.

Цель изобретения — расширение функциональных возможностей устройства за счет обеспечения возможности 15 получения количественной оценки достоверности проверки.

Поставленная цель достигается тем, что подсчитывается общее число команд программы И„ и число команд про- 20 граммы 11, во время выполнения которых имитировался сбой, после чего оп ределяют достоверность проверки программы на сбоеустойчивость

Мс 25 р 1п

Кроме того, подсчитывается общее число запусков команд N,,адреса кои и торьж совпадают с адресами меченых команд. Время выполнения программы при определенном составе входной .информации можно определить из со( отношения (1,1 1,1 ) и где d — время выполнения команды

ЦВИ.

Вычитание величины И учитывает

1 повторное выполнение койанды контролируемого участка после имитации. 40 сбоя.

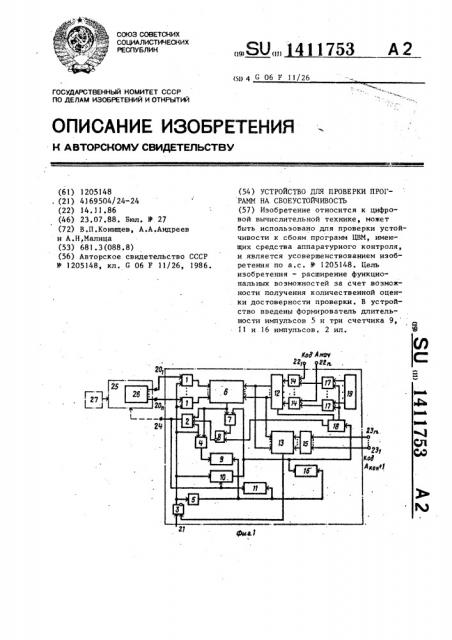

На фиг.1 представлена структурная схема устройства; на фиг.2 — схема таймера.

Устройство содержит первую группу элементов И 1,первый элемент И 2, второй триггер 3, второй элемент И 4, формирователь 5 импульсов, первую схему 6 сравнения, элемент ИЛИ 7, первый триггер 8, первый счетчик 9, .таймер 10, второй счетчик 11, сумматор

12, вторую схему 13 сравнения, группу элементов ИЛИ 14, первый регистр

15, третий счетчик 16, вторую группу элементов И 17, элемент 18 задержки, второй регистр 19, адресные входы

20„-20ц, где n — разрядность адреса

ЦВИ, вход 21 пуска, входы 22„-22 и установки начального адреса программы, входы 231-?3„ установки конечного адреса программы, выход 24 имитации сбоя устройства. Изображены ЦВИ 25 с регистром 26 адреса команд и имитатор 27 — входной информации.

Таймер (фиг.2) содержит счетчик

28 времени, включающий генератор 29 импульсов и счетчик 30,при этом генератор 29 импульсов содержит элемент НЕ 31, элемент 32 задержки, элемент И 33„ вход 34 запуска, а счетчик 30 содержит группу элементов И 35 и группу триггеров 36, обнуляющий вход 37 таймера; схему 38 сравнения, состоящую из элемента ИЛИ 39, группы элементов Й 40, группы элементов ИЛИ

41, группы элементов И 42, элемента

И 43, элемента 44 дифференцирования, потенциального 45 и импульсного 46 выходов равнозначности; регистр 47 с местными входами 48,-48 занесения„ местным обнуляющим входом 49 и группой триггеров 50, -а также элемент

И1ц1 51.

Устройство для проверки программ работает следующим образом.

В исходном состоянии триггеры 3 и

8 обнулены. Нулевой уровень с прямого выхода триггера 3 закрывает группу элементов И l и элементы И 2 и 4, а также блокирует работу таймера 10, Начальный адрес А и« программы, проверяемой на сбоеустойчивость, заносится по входам 22„-22 >через элементы ИЛИ 14 на предварительно обнуленный сумматор 12 а конечный, в качестве которого выбирается адрес пер" вой команды, выходящей за пределы програ А кои 1, — 0 входа» 23 123 в регистр 15., Единичный уровень с

h инверсного выхода триггера 8 присутствует на втором входе элемента И 2.

На регистр 19 заносится код шага сбоя (входы занесения на фиг.l не показаны), который равен,цлине команды в

ЦВ1",1.

Настройка таймера 10 осуществляется в зависимости от соотношения периода запуска программы или периода запуска имитатора входной информации

Тз и интервала време ы между двумя сбоями на одном и том же контролируемом участке, при котором программная защита от сбоев не классифицирует их как отказ. Если Т z Т, тай мер настраивается на выдачу сигналов через Т = Тс после его запуска, если же Т ь Тс, таймер настраивается на

3 14117 выдачу сигналов через Т =Т после его запуска. Код А ц подается с разрядных выходов сумматора 12 на вторые входы схемы 6 сравнения и на первые входы схемы 13 сравнения, на вторые входы которой поступает код A«„+1 с разрядных выходов регистра 15. Счетчики 9, 11 и 16 находятся в произвольном состоянии. 10

Устройство запускается сигналом, поступающим на вход 21 запуска, который переводит триггер 3 в единичное состояние. Из единичного перепада на прямом выходе триггера 3 формирователем 5 формируется импульс, который обнуляет счетчики 9, 11 и 16.

Единичный уровень с прямого выхода триггера 3 запускает таймер 10, поступает на третий вход элемента И,2, 20 на второй вход элемента И 4 и на вторые входы элементов И 1, разрешая прохождение потенциального кода адреса команды с разрядных выходов регистра 26 адреса команды ЦВМ 25 на пер-25 .вые входы схемы 6 сравнения.

При совпадении кодов на первых и вторых входах схемы 6 сравнения, последняя выдает сигнал, который проходит через элемент И 2.на выход 24 имитации сбоя, обьединяющийся с вы-! ходом схем аппаратурного контроля

ЦВМ 25 (не показан), через элемент

И 4 — на счетный вход счетчика 9 (подсчитывается N ) и через элемент

ИЛИ 7 — на единичный вход триггера 8.

Сигнал с выхода элемента И 2 поступает на счетный вход счетчика 11 (подсчитывается И ) и обнуляет счетчик таймера 10, синхронизируя его работу 40 с реальным периодом запуска программ.

Нулевой уровень с инверсного выхода триггера 8 закрывает элемент И 2.

Последующие совпадения содержимого регистра 26 адреса команд с кодом 45 адреса команды, поступающим на вторые входы схемы б сравнения (например, в: случае проверки циклического участка . программы), приводят к появлению на, выходе равнозначности схемы 6 сравне- 50 ния сигналов, количество которых подсчитано в счетчике 9. Сигналы при этом на счетный вход счетчика 9 приходят через элемент И 4. Значение счетчика 10 не изменяется, так как . 55 закрыт элемент И 2.

Если за время Т, на которое настроен таймер 10 совпадения кодов на входах схемы б сравнения не происходит, на выходе таймера 10 появляется сигнал, который переводит триггер 8 в единичное состояние, при этом нулевой уровень с инверсного выхода последнего закрывает элемент И 2., Сигнал с выхода таймера 10 поступает на счетный вход счетчика 16, работающего в режиме накопления (подсчитывается N„) и на вход элемента 18 задержки, где задерживается на время перевода триггера 8 в единичное состояние, после чего с первого отвода элемента 18 задержки используется для чтения шага сбоя из регистра 19 и подача кода шага сбоя через элементы И 17 и ИЛИ 14 на счетные входы сумматора 12. I

Задержанный на время переходных

/ процессов в сумматоре 12 сигнал с второго отвода элемента 18 задержки используется для реализации переносов в сумматоре 12. Задержанный на время реализации переносов в сумматоре 12 на время срабатывания схемы

13 сравнения и на время перевода триггера 3 в нулевое состояние, сигнал с выхода элемента 18 задержки переводит триггер 8 в нулевое состояние, при этом единичный уровень с его инверсного выхода поступает на второй вход элемента И 2. На вторые входы схемы 6 сравнения подается с разрядных выходов сумматора 12 код адреса очередной команды программы, Цикл работы повторяется.

При совпадении кода адреса очередной команды с сумматора 1 2 и кода (A1,on +i) с регистра 15 схема 13 сравнения выдает сигнал, который переводит триггер 3 в нулевое состояние.

При этом нулевой уровень с его прямого выхода останавливает таймер 10 закрывает группу элементов И 1 злементы И 2 и 4 и устройство завершает проверку программы на сбоеустойчивость. К этому времени в счетчике 11 подсчитано количество команд N во время выполнения которых удалось имитировать сбой, в счетчике 16 — общее число команд программы Nä, а в счетчике 9 — общее число запусков N> команд, адреса которых совпадают с адресами "меченых" команд.

Достоверность проверки программы на сбоеустойчивость можно предста5 )4117 вить отношением Р=Ис/N» а время работы определить иэ соотношения

Р (N>-N ) д ь, . где Л вЂ” время выполнения команды в ЦВМ 25. При этом для

ЦВМ с фиксированным рабочим тактом это истинное время, а для ЦЗМ с плавающим рабочим тактом - его оценка (в силу использования в этом случае в качестве dс величины, обратной среднему быстродействию ЦВМ).

Для проверки программ на сбоеус- . тойчивость на одной ЦВМ с использо( ванием предлагаемого устройства необходим имитатор 27 входной информации. (era запуск нетрудно сделать пе риодическим). Применение имитатора позволяет сравнить полученные результаты работы программы без подктпоченного и с подключенным устройст- 20 ! вом проверки программ на сбоеустойчивость. По значениям N и N ìîæíî судить не только о достоверности проверки программ на сбоеустойчивость, но и о качестве имитатора входной ин- 25 формации (учитывая тезис "прогонка каждой команды хотя бы один раз").

53 6

Формула изобретения

Устройство для проверки программ на сбоеустойчивость по авт.св.

9 1205148, о т л и ч а ю щ е е с я тем, что, с целью расширения Функцио" нальных возможностей устройства пу-. тем обеспечения воэможности получения количественной оценки достоверности проверки, в устройство введены формирователь импульсов, второй элемент И, первый, второй и третий счетчики, причем прямой выход второго триггера соединен с первым входом второго элемента,И и через формирователь импульсов — с входами установки в "0" первого, второго и третьего счетчиков, выход сравнения первой схемы сравнения соединен.с вторым входом второго элемента И, выход которого соединен со счетным входом первого счетчика, выходы первого элемента И и выход окончания временного интервала таймера соединены соответственно со счетными входами второго и третьего счетчиков.

1411753

Составитель И.Сигалов

Техред И.Дидык Корректор О.Кравцова

Редактор П.Гереши

Заказ 3663/45 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4