Устройство для вывода информации

Иллюстрации

Показать всеРеферат

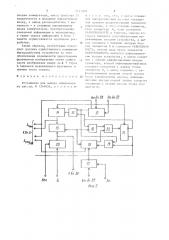

Изобретение относится к автоматике и вычислительной технике и может ,быть использовано в выходных устройствах универсальных ЭВМ или системах оперативной связи человека с вычислительной машиной. Цель изобретения - повышение быстродействия за счет сокращения времени редактирования выводимой информации. Поставленная цель достигается тем, что в устройство, содержащее блок памяти 1, дешифратор 2, распределитель импульсов 3, блок синхронизации 4, коммутатор 5, блок преобразования координат 6 и блок формирования адреса 7, введены триггер , блок элементов И, блок элементов РАВНОЗНАЧНОСТЬ и сумматор, что обеспечивает возможность осуществления редактирования информации путем сдвижки части изображения вверх или вниз и переноса удаленного фрагмента в нижнюю часть экрана 3 иЛо (/

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) 11807 A 2 (51) 4 G 09 G 1/08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 1 244656 (21) 4179369/24-24 (22) 09. 01.8 7 (46) 23.07.88. Бюл. № 27 (71) Московский инженерно-физический институт (72) О. Н. Цапко (53) 681.327(088.8) (56) Авторское свидетельство СССР № 1244656, кл. Г 09 G 3/12, 1984. (54) УСТРОЙСТВО ДЛЯ ВЫВОДА ИНФОРМАЦИИ (57) Изобретение относится к автоматике и вычислительной технике и может, быть использовано в выходных устройствах универсальных ЭВМ или системах оперативной связи человека с вычислительной машиной. Цель изобретения повышение быстродействия за счет сокращения времени редактирования вьг водимой информации. Поставленная цель достигается тем, что в устройство, содержащее блок памяти 1, дешифратор

2, распределитель импульсов 3, блок синхронизации 4, коммутатор 5, блок преобразования координат 6 и блок формирования адреса 7, введены триггер, блок элементов И, блок элементов

РАВНОЗНАЧНОСТЬ и сумматор, что обеспечивает возможность осуществления редактирования информации путем сдвижки части изображения вверх или вниз и переноса удаленного фрагмента в г нижнюю часть экрана. 3 ил.

3 14118 вверх он устанавливается в "1". Сигнал кадрового гасящего импульса, по— ступающий из блока 4 синхронизации на первый вход блока 7 формирования

5 адреса, устанавливает первый .12 и второй 14 счетчики и триггер 21 в состояние "0". С началом видимого хода кадра с выхода элемента И 31 на тактовый вход первого счетчика 12 посту-10 пают импульсы с периодом, равным длительности считывания одного слова из блока 1 памяти, Первый счетчик 12 имеет коэффициент пересчета, равный

2", и осуществляет пересчет количества слов блока 1 памяти, умещающихся в одной строке изображения. Сигналы с выхода старшего разряда первого счетчика 12 через первый элемент И 13 поступают на тактовый вход второго счетчика 14, осуществляющего пересчет строк изображения. Выходы второго счетчика 14 подключены к входам блока 15 сравнения, где осуществляется сравнение кода текущей строки с кодом Yz, поступающим с инверсных выходов второго регистра 20. При совпадении кодов блок 15 сравнения вырабатывает импульс сравнения, который через второй элемент И 16 и элемент

ИЛИ 22 перебрасывает по тактовому входу триггер 21 в состояние "1".

В режиме сдвижки изображения вверх на 4 Y строк состояние 1 на выходе триггера 8 разрешает прохождение кода

Y через блок элементов И 9 на первые о входы с уммат ор а 1 О.

Выход триггера 8 поступает на объединенные между собой первые входы блока элементов И 9 и объединенные между собой первые входы группы элементов РАВНОЗНАЧНОСТЬ 11.

На вторые входы группы элементов

И 9 поступает параллельный код с инверсного выхода второго регистра 20. 45

Таким образом, на выходе блока элементов И 9 образуется параллельный код

Y, который поступает на первые входы сумматора 10, Аналогично на вторые входы блока элементов РАВНОЗНАЧНОСТЬ

11 поступает параллельный код 4Y который в зависимости от состояния триггера 8 ("О" или "1") проходит параллельным кодом на выход в виде Ьу или Ь7 и поступает на вторые входы сумматора 10. Таким образом, на выхо55 де сумматора 10 устанавливается код ь Y который записывается в первый регистр 17 сигналом "Запись". При

07 раздвижке же изображения вниз, триггер 8 устанавливается в "О", запирает блок элементов И 9 и подключает к вторым входам сумматора 10 через блок элементов РАВНОЗНАЧНОСТЬ 11 код

Таким образом, на выходе сумматора 10 устанавливается код 47 и сигналом "Запись" заносится в первый регистр 17. Импульс сравнения с вы-. хода блока 15 сравнения производит запись выходного состояния первог о регистра 17 (Y + а7) при сдвижке или ьу при раздвижке) в счетчик 18 °

Счетчик 18 включает в себя m двоичных разрядов. "0" на инверсном выходе триггера 21 запирает первый 13 и второй 16 элементы И, а "1" на прямом выходе триггера 21 подключает выход первого счетчика 12 к тактовому входу счетчика 18 через третий элемент И 19. Счетчик 18 пересчитывает строки изображения до своего переполнения. Сигнал переполнения с выхода переполнения счетчика 18 через элемент ИЛИ 22 переводит триггер 21 обратно в состояние "0". Тем самым осуществляется возврат к пересчету строк вторым счетчиком 14. Выходы второго счетчика 14 и счетчика 18 образуют совместно с выходами первого счетчика 12 адреса считывания слов из блока 1 памяти. При этом, если прямой выход триггера 21, являющийся управляющим для коммутатора 5 адреса равен "О", то к блоку 1 памяти через коммутатор 5 подключаются выходы первого счетчика 12 и второго счетчика

14, а если прямой выход триггера 21 равен 1", то к входам блока 1 памяти подключаются выходы первого счетчика 12 и счетчика 18. Для этого прямой выход триггера 21 подключен к управляющему входу коммутатора 5. При подаче на коммутатор 5 адресов считывания слов выходы первого счетчика 12 образуют младшие разряды адреса, а выходы второго счетчика 14 строк или счетчика 18 — старшие разряды. Таким образом, осуществляется считывание информации из блока 1 памяти.

При этом выходы первого счетчика

12 и второго счетчика 14 подключаются к первым информационным входам коммутатора, выходы счетчиков 12 и 18 подключаются к вторым входам коммутаторов, выходы блока 6 преобразования координат параллельно подключаются к третьим и четвертым информационным

10 входам коммутатора, выход триггер". ? 1 подключается к младшему- управляю!.!ему входу, а выход распределителя 3 импульсов — к старшему управляющему входу коммутаторов. 11реобразование считанной информации в вкдеосигнал, а также запись информации в блок памяти осуществляется идентично устройству.

Таким образом, изобретение позво"ляет достичь существенного повышенкя быстродействия устройства за счет обеспечения возможности перестановки фрагментов изображения путем сдвига части изображения вверх на 4 У строк и переноса исключенного фрагмента в нижнюю часть экрана, Формула изобгет ения

Устр ойство для вывода информации по авт.св. 3313 1244656, о т л к ч а ю1!i с О Г я тем, что, с Iie I!E!7 повьп!!ения быстр О;1ействия з» с,eò сокрашенияя peMpi!3 ре; актирования Выводимой инфОрмацки, в пего 13 едены сумматор, блок элеме 3тов И, OJ!ок эJ.eментов

РА 31103ÈË".11k3ÑTh и триггер, Выходы ко"017 О г О я Вл я ю т Г я у! О и Гл нк т ел ь 13ыми уп

1>а вляк!3цлм3! Вх Ода ми устройства, а выход соединен с первь3ь33- входами блоков элементов И и элементов РАВНОЗНАЧНОГ:. 7> Е3Т0170Н вхОд OJIOKI. 0,31ементов

РАВНО ЗНАЧНОСТВ является информацио,— ным Входом устройства, а выход соедине!3 с первым кнформацконным входом сумматора, второй информационный вход которого по !Кпючен к в Ixоду блока

ЭЛЕМЕВТОВ И,,l ВЫХОД СОЕДИНЕН С КНфОР! Iа i>Ioklkib мк !3хОДам33 !3 TOP Ок г1>Уппы б..ioi;". !,.:017. 33!рова!3кя адреса информа-!

3>3о:!Eib!e выходы Второй Группь1 <Оторого

ООе!ИI!е!1ы с 13тopbIM x0,10м Олока элГ. ментов И.

1411807

М к

Составитель E. Конюшенко

Техред Л.Сердккова Корректор А. Обручар

Редактор С. Патрушева

Заказ 3657/47

Тираж 459

Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул, Проектная, 4