Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Целью изобретения является повышение точности контроля. Устройство содержит блок 1 модульной памяти, вьшолненньш из модулей I,-IM памяти, с адресными входами 2, информационными выходами 3, выходами 4 модуля 1 памяти, выходами 5 признаков многократных оши-. бок и выходами 6 признаков однократных ошибок, регистр 7 адреса с адресными входами 8 устройства, формирователи 9 и 10 четности, три элемента ИЛИ 11-13, три элемента И 14-16, группу элементов ИЛИ 17, две группы элементов И 18, 19, блок 20 коррекции с информащ онными выходами 21 устройства и выход 22 сигнала наличия некорректируемой ошибки. Каждый из модулей 1,1ц,., памяти содержит . накопитель, блок контроля по ходу Хэмминга и мультиплексор. Однократные ошибки корректируются блоками, контроля в каждом модуле 1 мп мяти. В модуле 1 памяти хранятся контрольные сигналы чбтности одноименных разрядов слов с одинаковыми адресами. Точность контроля повьшается за счет коррекции двойных ошибок , возникающих одновременно в любом одном модуле 1,-1 памяти, коррекции части тройных ошибок, возникающих в различных модулях памяти, и обнаружения четырехкратных ошибок с помощью формирователей 9, 10:четности , элементов И, ИЛИ и блока 20 коррекции. 1 з.п. ф-лы, 4 ил. а S (Л с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (11) 158 4 ii С 29 00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 409?704/24-24 (22) 24.07.86 (46) 23.07.88. Бюл. М - 27 (72) Н.Д.Рябуха и С.В.Корженевский (53) 681.327 (988.8) (56) Авторское свидетельство СССР

Ф 1149318, кл. G 11 С 29/00, 1984.

Авторское свидетельство СССР

Ф 1157575, кл. G 11 С 29/00, 1984 ° (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ (57) Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Целью изобретения является повышение точности контроля. Устройство содержит блок 1 модульной памяти, выполненный из модулей 1, -1,„ памяти, с адресными входами 2, информационными выходами

3, выходами 4 модуля 1„ памяти, выходами 5 признаков многократных ошибок и выходами 6 признаков однократных ошибок, регистр 7 адреса с адресными входами 8 устройства, формирователи 9 и 10 четности, три элемента

ИЛИ 11-13, три элемента И 14-16, группу элементов ИЛИ 17, две группы элементов И 18, 19, блок 20 коррекции с информационными выходами 21 устройства н выход 22 сигнала наличия некорректируемой ошибки. Каждый из модулей 1, -1„, памяти содержит накопитель, блок контроля по коду

Хэмминга и мультиплексор. Однократные ошибки корректируются блоками контроля в каждом модуле 1„ -1„, памяти. В модуле 1,„ памяти хранятся контрольные сигналы четности одноименных разрядов слов с одинаковыми адресами. Точность контроля повышается за счет коррекции двойных ошибок, возникающих одновременно в любом одном модуле 1, -1,„,памяти, коррекции части тройнйх ошибок, возникающих в различных модулях памяти, и обнаружения четырехкратных ошибок с помощью формирователей 9, 10 четности, элементов И, ИЛИ и блока 20 коррекции. 1 з.п. ф-лы, 4 ил.

1411834

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам.

Цель изобретения — повышение точ ности контроля.

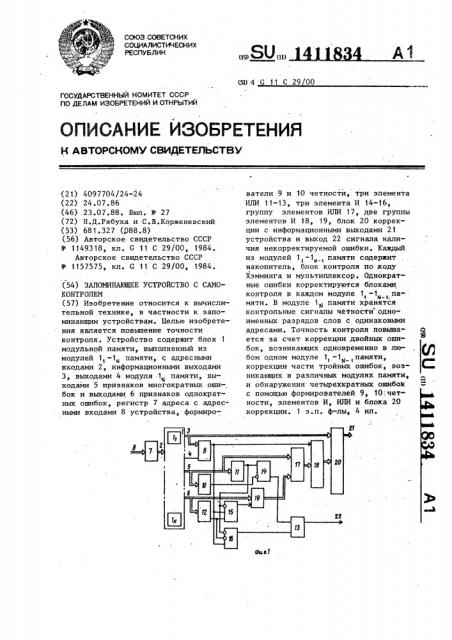

На фиг. 1 представлена функциональная схема предложенного устройства, на фиг. 2 — структурная схема блока модульной памяти, на фиг. 3 функциональная схема наиболее пред-! почтительного варианта соединения элементов ИЛИ группы, элементов И первой группы и блока коррекции, на !

:фиг. 4 — структура используемого корректирующего кода и принцип коррекции ошибок различной кратности, поясняющие работу устройства.

Устройство содержит (фиг. 1) блок

1 модульной памяти, выполненный из 20 модулей l -1д памяти, с адресными входами 2, информационными выходами

3, выходами 4 контрольного модуля

1„ памяти, выходами 5 признаков многократных ошибок и выходами 6 призна-25 ков однократных ошибок, регистр 7 адреса с адресными входами 8 устройства, первый 9 и второй 10 формирова тели четности, с первого по третий ! ,элементы ИЛИ 11-13, с первого по тре-30 тий элементы И 14.-16, группу элементов ИЛИ 17, первую 18 и вторую 19 группы элементов И, блок 20 коррекции с информационными выходами 21 устройства.и выход 22 сигнала наличия некорректируемой ошибки.

Каждый из модулей 1 -1, памяти содержит (фиг.2) накопитель 23, узел

24 контроля по коду.Хемминга и муль типлексор 25.

На фиг. 3 обозначены элементы

ИЛИ 17 -17я,, элементы И 18,-18,„ и сумматоры 20,-21„,,по модулю два в блоке 20 коррекции.

На фиг. 4 обозначены информационные разряды 26 -26 и контрольные разряды 26 ;26,„(где ш - число информационных разрядов, k — число контрольных разрядов слова) кода

Хемминга, применяемого для контроля каждого из 1, -i„ < Mopyaea памяти, и показаны девять вариантов расположения ошибок в информационных разрядах блока 1 модульной памяти.

Устройство работает следующим об,разом.

В накопителях 23 (фиг.2) модулей

1 -1 памяти хранятся закодированЙ-$ ные модифицированным кодом Хемминга п-разрядные слова (где и = т + 1с).

В модуле 1, (фиг. 1) памяти хранятся контрольные сигналы четности одноименных разрядов слов с одинаковыми адресами модулей 1,-1,„ памяти.

На выходы 3 модулей t — 1 (пася-1 ле возможной коррекции) выдаются вы бранные одноименные разряды всех модулей памяти. На выходы 4 выдается сигнал четности выданных на выходы 3 информационных разрядов. На выходы 5 выдаются сигналы обнаружения двойной ошибки, на выходы 6 выдаются сигналы о проведенной коррекции одиночной ошибки в модулях 1< †.1 1 памяти.

При считывании в каждом модуле

1 -1„ из накопителя 23 считывается и-разрядное слово, которое проверяется кодом Хемминга в узле 24. Прй возникновении двойной ошибки производится ее обнаружение и формирование сигнала двойной ошибки. Этот сигнал поступает на соответствующий выход

5. При,возникновении одиночной ошибки производится ее коррекция узлом

24 и формируется на выходе б сигнал о том, что произведена коррекция.

На выходы 3 каждого модуля 1 -1 памяти из считанных и-разрядов в соответствии с младшими разрядами адреса выдается только один из информационных разрядов, откорректирован". ный кодом Хемминга. Таким образом, при считывании на выходы 3 выдается слово из N-1 разрядов, по которым в формирователе 9 формируется сигнал четности, который складывается по модулю два с сигналом четности, поступакицим из модуля i ÷åðås выход

4. Результат сложения в виде сигнала ошибки поступает на входы элементов И 18 и разрешает выдачу в блок 20 сигналов коррекции.

При возникновении ошибок в модулях 1, -11 памяти могут быть следующие ситуации.

Одиночная ошибка в одном модуле памяти (1-й случай, фиг ° 4). Одиночная ошибка обнаруживается с.помощью узла 24 и корректируется кодом Хемминга. На соответствующий из выходов б выдается единичный сигнал, свидетельствующий о том, что произведена коррекция одиночной ошибки в одном модуле памяти. Поскольку ошибка ис равлена, то сигнал четности одно1834

55 з 141 именных разрядов всех модулей памяти на выходе формирователя 9 равен нулю, и сигналы коррекции в блок 20 не вьдаются. Аналогично производится исправление двойных, тройных, четырехкратных и ошибок большей кратности, располагающихся по одной в каждом модуле 1, — 1„, памяти (З-й, б-й, 7-й, 9-й случаи, фиг.4) .

Двойная ошибка в одном модуле памяти (2-й случай, фиг.4). Эта ошибка обнаруживается кодом Хемминга в узле 24. На соответствующий из выходов 5 выдается единичный сигнал, который через элемент ИЛИ 17 поступает на вход соответствующего элемента

И 18. Допустим, например, что на выходы 3 выдаются вторые разряды всех модулей 1< -1N памяти, при этом формирователь 9 сформирует единичный сигнал ошибки, который поступает на входы элементов И 18 и.разрешает выдачу в блок 20 сигналов коррекции.

В качестве сигналов коррекции в данном случае используются сигналы на выходах 5 о двойных ошибках; среди которых только .один сигнал равен единице. Этот единичный сигнал складывается в блоке 20 по модулю два с соответствующим информационным разрядом. В результате на выходы 21 выдается исправленное слово. Аналогично исправляется ошибка при считывании третьих разрядов всех модулей памяти. Если считываются разряды, в которых нет ошибки (например, шестые разряды), то сигнал ошибки на выходе формирователя 9 равен нулю, и коррекция в блоке 20 не производится. Таким образом исправляются все двойные ошибки, возникающие в каждом модуле 1< -1 <памяти.

Тройная ошибка. Допустим, что из трех ошибок две расположены в одном модуле памяти, а одна — в другом модуле памяти (5-й случай, фиг.4), тогда одиночная ошибка будет исправлена кодом Хемминга в узле 24, а двойная ошибка исправляется в блоке 20 как было ранее рассмотренр.

Предположим, например, что все три ошибки расположены в одном модуле памяти (4-й случай, фиг.4). Тройная ошибка кодом Хемминга в узле 24 обнаруживается, но распознается как одиночная, при этом возможна ложная коррекция. Однако при коррекции может быть скорректирован и один

40 из ошибочных разрядов. Предположиь<, что считываются вторые разряды из модулей 1 -1 и в результате провей денной коррекции, например, в пятом модуле памяти второй разряд исправлен, тогда сигнал ошибки на выходе формирователя 9 .равен нулю, и коррек ция в блоке 20 не производится. Если в результате проведенной коррекции исправлен какой-то другой разряд, то при считывании на выходе формирователя 9 сформируется единичный сигнал ошибки, который поступает на входы элементов И 18 и разрешает в блоке 20 коррекцию. В качестве сигналов коррекции в блок 20 в этом случае поступают сигналы с выходов

6, при этом на выходах 5 все сигналы равны нулю, и с выхода элемента

ИЛИ 11 нулевой сигнал подается на инверсный вход элемента И 15, на двух других входах которого присут" ствуют единичные сигналы с выхода элемента ИЛИ 12 и с выхода формирователя 9. На выходе элемента И 15 формируется единичнь<й сигнал, разрешающий выдачу через элементы И 19, элементы ИЛИ 17 и элементы И 18 сигналов коррекции с выходов 6 в блок

20. Среди этих сигналов только один

I сигнал, например, на выходе 6 пятого модуля 1 памяти равен единице, а остальные равны нулю. В. блоке 20 произойдет сложение по модулю два сигналов коррекции и информационных сигналов, считанных из блока 1. На

I выходы 21 выдается исправленное слово. Таким образом исправляются тройные ошибки. Среди всех возможных тройных ошибок, а их возможно всего

М,, где.(<<< «н}

« (где С„ — число сочетаний) . не ис-: правляется часть ошибок, располагающихся по три в одном модуле памяти.

Всего таких неисправимых ошибок М, где

Ма Cs N ° .

Например, при и = 63 и N = 64 из всех тройных ошибок не исправляются менее чем — 1OOr - 0 02

Таким образом, устройство позво" ляет исправлять все одиночные двойные и 99,97. тройных ошибок. l411834

Неисправимые четырехкратные ошибки возможны в том случае, если они располагаются в виде четырехугольника (8-й случай, фиг.4). Такие ошиб ;ки обнаруживаются по наличию одно временно двух сигналов на выходах 5 о двойных ошибках в двух модулях па-, яти. Обнаружение таких ошибок прозводится формирователем 10, элементом ИЛИ 11 и элементом И 14, при том с выхода элемента И 14 через лемент ИЛИ 13 на выход 22 выдается сигнал обнаружения некорректируемой шибки. Такой же сигнал формируется на выходе элемента И 16 в том случае, если формирователь 9 формиует сигнал ошибки, а на выходах 5

6 все сигналы равны нулю.

10

20 входу третьего элемента ИЛИ, выход которого является контрольным выхо30

50 о р м у л а изобретения

1. Запоминающее устройство с саоконтролем, содержащее блок модульой памяти, блок коррекции, первый ормирователь четности, первый элеент И и регистр адреса, входы котоого являются адресными входами устойства, причем выходы регистра адеса соединены с адресными входами блока модульной памяти, информацион. ные выходы которого подключены к входам первой группы первого формиро вателя четности и информационным входам блока коррекции, о т л и— ч а ю щ е е с я тем, что, с целью овышения точности контроля устройt ства в него введены второй формиро ватель четности, первая и вторая группы элементов И, группа элементов

ЙЛИ, с первого по третий элементы

ИЛИ, второй и третий элементы И, причем входы второй группы первого формирователя четности соединены с контрольными выходами сигналов четности блока модульной памяти, контрольные выходы признака многократной ошибки которого подключены к первым входам элементов ИЛИ группы, входам первого элемента ИЛИ и входам второго формирователя четности, выход которого соединен с первым инверсным входом первого элемента И, второй вход которого подключен к выходу первого элемента ИЛИ и первым инверсным вхо-" дам второго и третьего элементов И, выходы элементов ИЛИ группы подключены к первым входам элементов И первой группы, выходы которых соединены с входами сигналов разрешения блока коррекции, выходы которого являются информационными выходами устройства, контрольные выходы признака одиночной Ошибки блока модульной памяти подключены к первым входам элементов И второй группы и входам второго элемента ИЛИ, выход которого соединен с вторым прямьы входом второго элемента И и вторым инверсным входом третьего элемента И, выход которого подключен к первому дом устройства, второй вход третьего элемента ИЛИ соединен с выходом пер- вого элемента И, третьи прямые входы второго и третьего элементов И подключены к выходу первого формирователя четности и вторым входам элементов И первой группы.

2. Устройство по п.1, о т л и— ч а ю щ е е с я тем, что каждый модуль памяти блока модульной памяти содержит накопитель, мультиплексор и узел контроля по коду Хемминга, информационные входы и выходы которого соединены соответственно с информационными выходами накопителя и с информационными входами мультиплексора, выходы которого являются информационными выходами блока модульной памяти, выход признака многократной ошибки и выход признака одиночной ошибки узла контроля по коду Хемминга являются соответственно контрольным выходом признака многократной ошибки и контрольным выходом признака однократной ошибки блока модульной памяти, адресные входы накопителя и управляющие входы мультиплексора являются соответственно адресными входами старших разрядов и адресными входами младших разрядов блока модульной памяти.

1411834

Фиа2

Om

От

От

°

°

°

Dm

От фиг.З

1411834

В ЭФ еее 11ф

2 3 9 5 6 7 tn tnt m>2 m 8- Ю Ю*В

Фиг.0

Составитель Т.Зайцева

Редактор .С.Патрушева Техред M.ÄHäûê Корректор М.Демчик

Заказ 3661/49

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

Тираж 590 Подписное

ВНИИПИ Государственйого комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

11

fg

lg

lq

1у

2g у

lg

1)