Способ многоканального аналого-цифрового преобразования сигналов и устройство для его осуществления

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике и может использоваться в системах сбора информации от большого числа аналоговых датчнков. Изобретение позволяет повысить быст родействие. Это достигается тем, что оценку входных сигналов осуществляют ;В два этапа. На первом этапе определяют Н старших из F разрядов полной оценки входешх сигналов путем одновременного сравнения всех входных сиг- : налов со ступенчато .нарастапцим грубыми квантами /2 эталонньм сиг налом и запоминают по казвдому каналу значение уменывеяного на полкванта мвкс эталонного сигнала в момент его превьацения входного сигнала. На втором этапе осуществляют оценку оставшихся Р-Н младших разрядов путем поразрядного уравновешивания входных сигналов поочередно в каждом канале, начиная с уровней опорных напряжений, Iзаписанных в память на первом этапе, ;а в устройство для осуществления спо- |соба, содержащее аналоговые компара торы 8, мультиплексор 4, цйфроаналоговый преобразователь 7 блок 5 управления, введены постоянное запоминающее устройство 1, оперативное запоминшощее устройство 2, счетчик 6 импульсов, коммутатор 3 2 с. и 1 з.п. ф-лы, 2 ил. а в (Л с

СОЮЗ СОВаТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (Н) А1 (5))4 Н ОЗМ1 46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ . К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ.(21) 4104980/24-24 .(22) 29 ° 05.86 (46) 23 07.88. Бюль ?7

;(71) Институт теплофизики СО АН СССР (72) Е,ВБКожухова и В И.Титков (53) 681 ° 325(088.8) (56) Балакай В.Г. Интегральные схеиы

АПЦ и ЦАП. М.: Энергия, 1978, с 246247, рис 6 21.

Сенченко В.P. Многоканальный аналого-цифровой преобразователь, приборы и техника эксперимента, 1985, )(5 2 с.129-131 (54г СПОСОБ ННОГОНАНАПЬНОГО АНАЛОГО»

ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ СИГНАЛОВ И

УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ (57) Изобретение относится к иэмери» тельной технике и может искольэоватьЬ ся в системах сбора информации от большого числа аналоговых датчиков.

Изобретение позволяет повысить быстродействие. Это достигается тем, что оценку входных сигналов осуществляют

s два этапа. На первом .этапе окределяют Н старших иэ Р разрядов полной оценки входных сигналов путем одно временного сравнения всехвходных сиг" налов cD ступенчато .нарастакщим .грубыми квантаии U »„, /2. эталонными сиг.- налои н запоминают по каждому каналу значение уменьшенного на полквакта

U „ /2" эталонного сигнала s момент

его превышения входного сигнала. На втором этапе осуществляют оценку оставшихся Р-Н младших разрядов путем поразрядного уравновешивания входных сигналов поочередно в каждом какале, начиная с уровней опорных напряжений, :записанных в память на нервом этапе, .а в устройство для осуществления споЗ ,соба, содержащее аналоговые компара тари Б, иультнпленсор 4, пнфроенелого- (/) вый преобразователь 7, блок 5 управления, введены постоянное эапомн- С нающее устройство 1, оперативное запоминающее устройство 2, счетчик 6 импульсов, коммутатор 3 ° 2 с. и

1 s,n. ф-лы, 2 нл.

1411972

Изобретение относится к измерительной технике и может быть использовано в системах сбора информации от большого числа аналоговых датчиков.

Цель изобретения — повышение быстродействия.

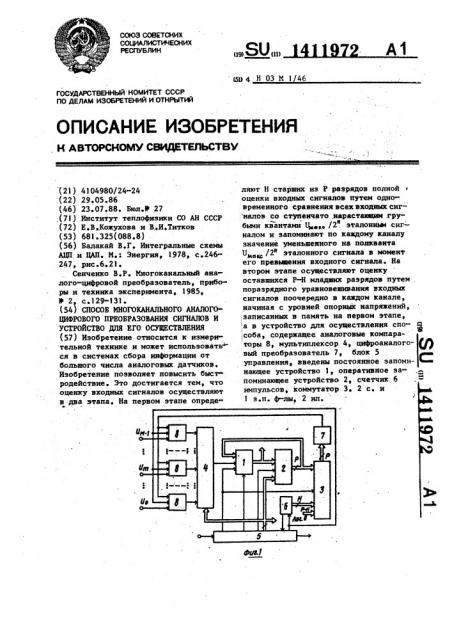

На фиг.1 приведена функциональная схема устройства; на фиг.2 - функциональная схема блока управления. 1О

Устройство содержит (фиг.1) постоянное запоминающее устройство (ПЗУ) оперативное запоминающее устройство (ОЗУ) 2, коммутатор 3, мульти-. плексор 4, блок 5 управления, счетчик 15 6 импульсов, цифроаналоговый преобразователь (ЦАП) 7, аналоговые компараторы 8. Блок 5 управления (фиг.2) выполнен на D-триггерах 9-13, элементе И 14, генераторе 15 импульсов, 20 счетчике 16 импульсов, мультиплексо-, рах 17 и 18, счетчике 19 импульсов, инверторе 20, мультиплекорах 21 и 22, элементе ИЛИ-НЕ 23, счетчике 24 импульсов, инверторе 25, счетчике 26 25 импульсов и элементе ИЛИ 27.

Устройство работает следующим образом.

Оценка значений входных сигналов производится s два этапа. На первом

30 этапе осуществляется оценка Н старших из Р разрядов полной оценки входных сигналов. Во время этого этапа на младшие н старшие входы ЦАП 7 поступают через коммутатор 3 соответственно 35 нулевой и выходной. коды счетчика 6, содержимое которого увегичивается на единицу в каждом такте преобразования по сигналу с второго выхода блока 5, В соответствии с содержимым 40 счетчика б на выходе ЦАП 7 вырабаты»-. вается ступенчато нарастающий грубыми квантами U /2" эталонный сигнал макс

Б„. Этот сигнал поступает на первые

:входы аналоговых компараторов 8 и 45 .сравнивается с измеряемыми сигналами

U - U поступающими на вторые входы аналоговых компараторов 8. Результаты этого одновременного сравнения всех входных сигналов с эталонным сигналом зпоминаются на время такта преобразования в соответствии с высоким уровнем сигналов на втором выходе блока, 5 на третьем входе аналоговых компараторов 8. Это позволяет55 совместить процесс установления следующего значения эталонного сигнала с процессом формирования содержимого ячеек ОЗУ 2 с помощью мультиплексора

4 и ПЗУ 1 в соответствий с предыдующим содержимьи ячеек ОЗУ 2 и результатами сравнений входных сигналов с текущим значением эталонного сигнала. В течение каждого такта преобразования блок 5 формирует на адресных входах мультиплексора 4 и

ОЗУ 2 последовательность двоичных номеров всех М каналов устройства, В соответствии с этой последовательностью номеров выходные сигналы аналоговых компараторов 8 поочередно поступают через мультиплексор 4 на третий адресный вход ПЗУ 1,, на первые адресные входы которого при этом поочередно поступает содержимое ячеек ОЗУ 2, а на его второй адресный вход поступает в течение всего первого этапа преобразования единич-! ный сигнал с первого выхода блока

5. При этом на информационные входы

ОЗУ 2 поступает содержимое старшей половины адресного пространства

ПЗУ 1, где хранится таблица состояний счетчика с остановом по условию нулевого значения на третьем адресном входе ПЗУ 1. В этом случае при поочередной подаче в течение каждого такта преобразования на первый и третий адресные входы ПЗУ 1, соответственно, предыдущего содержимого ячеек ОЗУ 2 и выходных сигналов компараторов 8 через мультиплексор 4 на выходах ПЗУ

1 формируются коды, которые поочередно записываются в .ячейки ОЗУ 2 по сигналам записи низкого уровня с четвертого выхода блока 5, что обеспе чивает реализацию многоканального счетчика с остановом по каждому каналу в момент превышения эталонным сиг. налом U входного сигнала (в момент перехода выходного сигнала аналогово го компаратора из единичного состоя» ния в нулевое). При этом в ячейку ОЗУ

2 с номером соответствующего канала записываются в каждом такте преобразования цифровые эквиваленты текущих значений эталонного сигнала U увеличенные на полгрубого кванта

/2" до момента, пока эталонный мь кс сигнал меньше входного сигнала этого канала и цифровой эквивалент уменьЭ н щенного на полкванта 11, „ /2 значения эталонного сигнала U в момент превышения эталонным сигналом входного сигнала этого канала, начиная с этого момента и до конца первого этапа, Это позволяет за время 2 t< где н

3 1411

t+ — время одного такта преобразования, одного прохода эталонного сигнала от нуля до максимума произвести оценку Н старших из P разрядов полной 5 оценки входных сигналов и запомнить в ячейках ОЗУ 2 цифровые эквиваленты эталонных сигналов, с которых следует начинать поразрядное уравновешивание входных сигналов поочередно в каждом 10 канале для получения P-разрядных цифровых эквивалентов входных сигналов путем уточнения P-H miapmrx разрядов на втором этапе преобразования.

На втором этапе преобразования 15 на адресных входах мультиплексора

4 и ОЗУ 2 поочередно устанавливаются коды всех М номеров каналов через время, равное P-Н тактам, в течение которого определяются значения Р-Н 2р младших разрядов цифрового эквивален.: та входного сигнала заданного канала.

При установке кода номера очередного канала на адресных входах мультиплек сора 4 и ОЗУ 2 содержимое ячейки 25

ОЗУ 2 с номером этого канала поступает на первые адресные входы ПЗУ и на .входы ЦАП 7 через коммутатор 3. При этом на выходе ЦАП7

; устанавливается эталонный сигнал равный значению уменьшенного на полкванта Б „ /2" эталонного сигнала в момейт его превьппения входного сигнала этого канала на первом этапе преобразования. И с этого уровня напряжения начинается поразрядовое уравновешивание входного сигнала выходным сигналом ЦАП 7 с помощью компаратора этого канала, мультиплексора

4, ОЗУ 2, ПЗУ 1 и коммутатора 3.

При этом на информационные входы

ОЗУ 2 поступает в соответствии с нулевым сигналом с первого выхода блока 5 на втором адресном входе ПЗУ

1 содержимое младшей половины адрес- 45 ного пространства ПЗУ 1, где хранится таблица состояний регистра последовательного приближения. В этом случае при подаче в тактах преобразования на первый и третий адресные входы ПЗУ 1 соответственно предыдущего содержимого ячейки ОЗУ 2 с номером заданного канала и выходного сигнала аналогового компаратора этого канала через мультиплексор 4 на выходах

ПЗУ 1 формируется код в соответствии

55 с этой таблицей состояний регистра последовательного приближения, кото ., рый заносится в эту же ячейку ОЗУ 2

972 по сигналу записи низкого уровня с четвертого выхода блока 5, что обес-. печивает реализацию функции регистра последовательного приближения, причем с начальной установкой в свое для каждого канала состояние в соответствии с содержимым ячеек ОЗУ 2, записанным на первом этапе. Это позволяет произвести поочередное уравновешивание входных сигналов и определить значения P-Н младших разрядов их цифровых эквивалентов за время второго этапа М)Р-H)t

Таким обращом, суммарное время первого и второго этапов преобразования всех М входных сигналов определяется выражением (2 .+ М(Р-Н11 и по сравнению с известным способом быстродействие предлагаемого повьппается в Р/(Р-1оя (М/2)) раз.

Ф о р м у л а и з о б р е т е н и я

1. Способ многоканального аналого" цифрового преобразования сигналов, заключающийся в формировании старших разрядов выходного кода и последующем формировании младших разрядов, выходного кода путем поразрядного уравновешивания входных сигналов соответствующими уровнями компенсирующего сигнала поочередно в каждом канале, отличающийся тем, что, с целью повьппения быстродействия, при формировании старших разрядов вы- ходного кода входные сигналы одновременно во всех каналах сравнивают с эталонным ступенчато-нарастающим сигналом, величина ступени которого соответствует весу младшего из группы старших разрядов выходного кода, опре ,деляют момент превышения эталонным ступенчато-нарастающим сигналом входного сигнала в каждом канале и форми"" руют в каждом канале код, соответствующий этому значению эталонного сту пенчато-нарастаюшего сигнала, уменьшенному на половину величины ступени эталонного ступенчато-нарастающего сигнала, и запоминают его, запомненный код в каждом канале затем преоб« разуют в соответствующую аналоговую величину и используют в качестве начального уровня компенсирующего сигнала при формировании младших разрядов выходного кода соответствующего

)4119?2

М Fnt, 1og (M/ln 2) канала, причем оптимальное значение количества старших разрядов выходного

Ent, logz(M/1n 2) при 1оц

Knt (log>(M/1n 2)1 + 1 при где Н вЂ” количество старших разрядов;

M " количество каналов.

2. Устройство для многоканального налого-цифрового преобразования игналов, содержащее M аналоговых омпараторов, где М - число каналов реобразователя, первые входы которых бъединены и соединены с выходом ифроаналогового преобразователя, втоой вход каждого аналогового компаатора является соответствующей ходной шиной, выходы аналоговых комараторов соединены с соответствующи- 2О и информационными входами мультилексора, блок управления, первый ход которого является шиной "Пуск", т л и ч а ю щ е е с я тем, что, целью повышения быстродействия, него введены постоянное запоминаю ее устройство, оперативное запоминаюее устройство, счетчик импульсов и оммутатор, выходы которого соединеы с соответствующими входами цифро»

30 налогового преобразователя, первые

«формационные входы коммутатора оразряцно объединены с первыми адресыми входами постоянного запоминаю его устройства и соединены с соотетствующими выходами оперативного, апоминающего устройства, адресный ход коммутатора объединен с вторым адресным входом постоянного запоминающего устройства и соединен с пер- 4О дым выходом блока управления, вторые

Информационные входы коммутатора являются тиной логического нуля, третьи ф нформационные входы коммутатора ф оединены с соответствующими информационными выходами счетчика импульсов, выход переноса которого соединен с вторым:входом блока управления, вто ой выход которого соединен с третьими фходами. М аналоговых компараторов и входом суммирования счетчика импуль сов, третий и четвертый выходы блока правления соединены соответственно

4 входом разрешения выборки постоянно; о запоминающего усФройства и входом

"*Запись-чтение" оперативного запомиНающего устройства, пятый выход блока правления является шиной готовности результата, шестые выходы блока кода связано с количеством каналов соотношением

1ор; М р Еп1 log (М/lп 2) управления соединены с соответствующими адресными входами мультиплексора и оперативного запоминающего устройства и являются шинами двоичных номеров каналов, причем выход мультиплексора соединен с третьим адресным входом постоянного запоминающего устройства, выходы которого соединены. соответственно с информационными входами опера-. тивного запоминающего устройства и являются выходными шинами.

3. Устройство по п.2, о т л и ч аю щ е е с я тем, что блок управления выполнен на пяти D-триггерах, элементе И, элементе ИЛИ, элементе

ИЛИ-НЕ, генераторе импульсов, четырех счетчиках импульсов, четырех мультиплексорах, двух инверторах, выход первого инвертора является пя тым выходом блока управления, вход объединен с первым информационным входом первого мультиплексора и соединен с выходом переноса первого счетчика импульсов, вход суммирова ния которого соединен с выходом второго мультиплексора, первые информационные входы второго и третьего мультиплексоров являются шиной логического нуля, вторые информационные входы второго и третьего мультиплексоров, первый информационный вход четвертого мультиплексора вход второ" го инвертора, входы стробирования первого и второго D-триггеров объединены и соединены с выходом переноса второго счетчика импульсов, вход суммирования которого объединен с вторыми информационными входами первого и четвертого мультиплексоров соединен с выходом переноса третьего счетчика импульсов, вход суммирования которого соединен с выходом элемента

И, первый вход которого соединен с выходом генератора импульсов,, второй вход — с прямым выходом третьего

D-триггера, инверсный выход которого соединен с первым входом элемента

ИЛИ, входы установки третьего, перво го, четвертого, второго и пятого

D-триггеров объединены и являются

1 первым входом блока управления, информационные входы третьего, четвер) 411972

Составитель А.Титов

Редактор А.Ворович Техред М.Дидык Корректор N.Øàðoøè

Заказ 3673/56 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская- наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 того и первого D-триггеров являются шиной логического нуля, вход стробирования третьего D-триггера соединен с выходом элемента ИЛИ-НЕ, входом стробирования четвертого D-триггера и является вторым входом блока управления, третьим выходом которого является инверсный выход первого 9< триггера, прямой выход четвертого 10

D-триггера соединен с информационными входами второго и пятого D-триггеров, вход стробирования которого соединен с выходом второго инвертора, а вы ход - с адресным входом третьего муль-15 типлексора, прямой выход второго Dтриггера соединен с первым входом элемента ИЛИ-HE адресными входами первого, второго и четвертого мультиплексоров и является первым выходом блока управления, вторым и четвертым выходами которого являются соответственно выходы третьего мультиплексора и элемента KTH второй вход которого соединен с выходом четвертого мультиплексора, шестыми выходами блош-. ка управления являются соответственно информационные выходы четвертого счетчика импульсов, выход переноса которого соединен с вторым входом элемента ИЛИ-НЕ, а вход суммирования — с выходом первого мульиплексора.