Преобразователь кода в код

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах для обработки цифровых данных. Изобретение позволяет без дополнительных аппаратурных затрат и нзменени11 структуры устройства преобразовывать параллельные коды произвольного вида, ЧТО обеспечивает расширение области .использования преобразователя. Преобразователь содержит счетчик I импульсов, два блока 2и 4 памяти, блок 3 сравнения кодов и блок 5 управления , состоящий из четырех триг. геров, четырех элементов, дешифратора , счетчика импульсов и генератора импульсов. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК ()9) (И) (5)) 4 Н 03 М 7 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21 ) 4060432/24-24 (22) 23.04.86 (46) 23.07.88. Бюл. У 27 (72) В Д. Баландина, Э. И. Данипов, И.В.Караванченко и Г.М.Кобяков (53) 681.325(088.8)(56) Авторское свидетельство СССР и 1162052, кл. Н 03 M 7/00, 1984.

Авторское свидетельство СССР.

1(1167737, кл. Н 03 М 7/00, 1984. (54) ПРЕОБРАЗОВАТЕЛЬ КОДА В КОД (57) Изобретение относится к вычислительной технике и может быть использовано в устройствах для обработки цифровых данных. Изобретение L позволяет без дополнительных аппара-турных затрат и изменений структуры устройства преобразовывать параллельные коды произвольного вида, что обеспечивает расширение области использования преобразователя. Пре образователь содержит счетчик 1 импульсов, два блока 2 и 4 памяти, блок 3 сравнения кодов и блок 5 уп- . равления, состоящий из четырех триггеров, четырех элементов, дешифратора, счетчика импульсов и генератора импульсов. 2 ил.!

4!!979

Изобретение относится к вычислительной технике, а именно к преобразователям информации, и может быть спользовано в устройствах для обраотки цифровых данных.

Цель изобретения — упрощение пребразователя и расширение области

ro использования за счет возможноти преобразования параллельных !О одов произвольного вида.

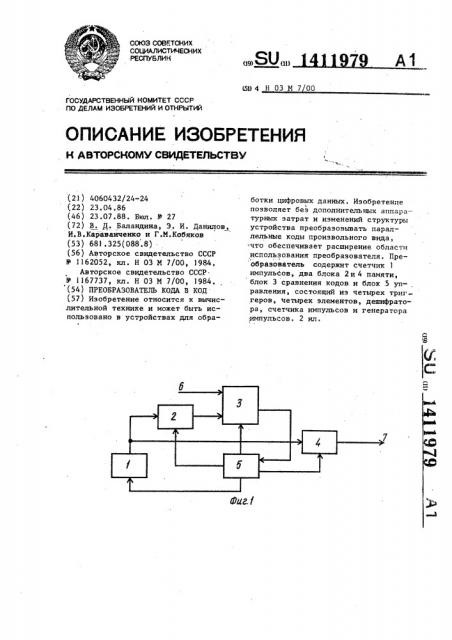

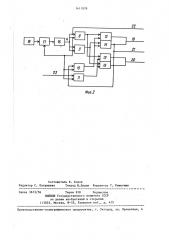

На фиг. 1 приведена блок-схема реобразователя параллельного кода, а фиг. 2 — функциональная схема блоа управления. 15

Преобразователь параллельного кода одержит счетчик 1 импульсов, первый лок 2 памяти, блок 3 сравнения коов, второй блок 4 памяти и блок 5 управления, вход 6 и выход 7. 20

Блок 5 управления состоит из первого, второго, третьего и четвертого триггеров 8-11, первого, второго, третьего и четвертого элементов И .12-15, дешифратора 16, счетчика 17 25 импульсов и генератора 18 импульсов, На фиг. 2 позициями 19-22 и 23 обозначены первый, второй, третий, четвертый выходы и вход блока 5 управления.

Блоки 2 и 4 памяти — перепрограмми-30 руемые постоянные запоминающие устрой. ства (ЗУ), В блок 2 записаны все воз,можные входные коды, в блок 4 — по тем же адресам записаны соответствующие им выходные коды, 35 . Счетчик 1 формирует адреса блока

2 и блока 4.

Блок 5 формирует сигналы управле; ,ния элементами преобразователя, так дешифратор 16 под воздействием генератора 18 и счетчика 17 задает длительность сигналов управления блока 2 и блока 4 и формирует тактовые импульсы для счетчика 1 и триггеров

8 и 9, формирующих сигналы считывания (СЧ) и выбора кристалла (ВК) для блоков 2 и 4. Элементы И 12 и

14 формируют сигналы СЧ и ВК для, блока 2, а элементы И 13 и 15 формируют сигналы СЧ и ВК для блока 4 °

На выходах элементов И !2 и 14

:формируются сигналы управления (считывания) блока 2, соответственно

СЧ и ВК, 55

На выходах элементов. И 13 и 15 формируются сигналы управления (считывание блока 4, соответственно

СЧ и ВК).

Преобразователь работает следующим образом.

При подаче текущего значения входного кода на блок 3 сравнения кодов блок 5 управления на выходе дешифратора !6 формирует тактовые импульсы (ТИ) для счетчика 1, а на выходах элементов И 12 и 14 сигналы управления (считывания) блока

2:генератор 18 импульсов, счетчик

17 и дешифратор 16 организуют выдачу импульсов, задающих длительности сигналов управления блоков 2 и 4, а триггеры 8 и 9 формируют эти сигналы и по разрешению с триггера 10 сигналы СЧ и ВК с элементов И 12 и

14 поступают на вход управления блока 2.

Для формирования сигналов СЧ и ВК блоков 2 и 4 нужно четыре импульса

Nl, N2, N3 и N4 с дешифратора 16, которые бы обеспечили заданные временные соотношения сигналов СЧ и ВК, отражающие конкретные особенности элементной базы и режимы работы преобразователя.

Для формирования сигнала СЧ используются Nl и N4 импульсы (по импульсу 1!! формируется передний фронт СЧ, а по импульсу N4 задний фронт). N2 и N3 импульсы участвуют в формировании сигнала ВК (по.импульсу N2 формируется передний фронт

ВК, а по импульсу N3 — задний фронт).

N4 импульс определяет конец цикла считывания и по нему же происходит сброс триггеров 10 и 11 и счетчика 17 блока 5 управления, Кроме того, сигнал ВК блока 2 является стробирующим импульсом (СТРОБ) для блока 3 сравнения, который разрешает сравнение кодов, поступающих на блок

3 ° Сигнал ВК блока 2 подтверждает пуск блока 2 в отсутствие равенства кодов на блоке 3 сравнения кодов.

Счетчик 1 последовательно переключает ячейки памяти блока 2, начиная с первой, и на блоке 3 сравнения каждое значение кода, считанное с блока

2, сравнивается с данным входным кодом до тех пор, пока не будет равенства этих кодов (блок 5 управления каждый раз вместе с новым адресом блока 2 формирует сигналы СЧ и

ВК блока 2).

В случае равенства кодов в блоке

3 сравнения по сигналу Равенство" з

14 блок 5 управления на выходе элементов И 13 и 15, по разрешению с триггера ll формирует сигналы: СЧ и ВК блока 4 (аналогично сигналам СЧ и ВК блока 2). Происходит считывание выходной информации с блока 4 по адресу, равному адресу блока 2 в момент равенства, т.е. по заданному входноу коду на выходе преобразователя сформирован новый код— результат преобразования.

Формула изобретения

Преобразователь кода в код, содержащий счетчик импульсов, выходы которого соединены с. адресными входами первого блока памяти, о т л ич а ю шийся тем, что, с целью упрощения преобразователя и расширения области его использования sa счет возможности преобразования параллельных кодов произвольного вида, в преобразователь введены блок сравнения кодов, второй блок памяти и блок управления, содержащий триггеры, элементы И, дешифратор, счетчик импульсов и генератор импульсов, выход которого соединен с информационным входом счетчика импульсов, выход которого соединен с входом дешифратора, выходы которого соответственно соединены с первыми и вторыми входами первого и второго триггеров, выход

11979, первого триггера соединен с первыми входами первого и второго элементов

И, выход второго триггера соединен с первыми входами третьего и четвертого элементов И, выход третьего триггера соединен с вторыми входами первого и третьего элементов И, выход четвертого триггера соединен с

1р .вторыми входами второго и четвертого элементов И, второй .вход первого триггера объединен с первыми входами. третьего н четвертого триггеров и с установочным входом счетчика импуль1 сов блока управления, выходы первого и третьего элементов И соединены с управляющими входами первого блока памяти, выходы второго и четвертого элементов И соединены с управляющими входами второго блока памяти, второй вход третьего триггера подключен к выходу третьего элемента И и объединен с входом стробирования блока сравнения кодов, выход которо25 ro соединен с вторым входом четвертого триггера, выход первого блока памяти соединен с первым входом блока сравнения кодов, адресный вход второго блока памяти подключен к выходу счетчика импульсов, вход которого объединен с первым входом первого триггера блока управления, :.второй вход блока сравнения кодов является входом преобразователя, вы-ход второго блока памяти является выходом преобразователя.

1411979

Составитель Б. Ходов

Редактор С. Патрушева Техред М.Дидык Корректор Г. Решетник

Заказ Зб73/56

Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий о ква Ж-35 Раушская наб., д. 4/5

113035, М с

Производственно-полиграфическое предприятие, r. р д, у

Ужго о л. Проектная, 4