Цифровой растровый индикатор

Иллюстрации

Показать всеРеферат

Изобретение относится к радио технике. Цель изобретения - повьшение быстродействия. содержит матричный.блок 3 памяти,ЦАП 5,видеоконтрольный блок 6,генератор 9 развертки , коммутатор 10 адреса и пре образователь 11 координат. Введены входной буферный блок 1 памяти, блок 2 постоянной памяти, выходной регистр 4, регистр 7 обратной связи И распределитель 8 импульсов. Работа устр-ва основана на функционировании двух независимых рабочих циклов: записи поступающей с РЛС информации в блок 3 и непрерывного выхода его содержимого на зкран блока 6. Движение антенны РЛС от угла азимута +90° через 0° до - -270 и обратно, В зависимости от того, в каком полу кадре сканирует антенна, РЛС вырабатывает признак, к-рый поступает на 1-й управляющий вход блока 2. Он м.б. равным, например, для левого полукадра логич. О, для правого - 1. Тактовые сигналь;, выр абатьюаемые P. flC, поступают на синх ров ходы . распределителя 8 и преобразователя 11. Распределитель 8 формирует последовательности импульсов,, Эти налы, управляют приемом инфо рмацни в блок 1, регистр 4 и регистр 7 и оргапоочередный доступ в блок 3 каждого .функционального цик.па через коммутатор 10. l -й доступ предназначен для вывода содержимого 3 на экран блока 6 через регис;тр 4 и ЦАП 5, - для записи 1шформации в блок 3. Цикл вьшода информации из блока 3 на экран блока 6 осуществляется , по строкам или столбцам, адрес гс-рых формируется генератором 9 синнронно с тактами представления I то доступа. 3 ил. СЛ

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИ(РЕСПУБЛИК .

„„SU,;„1412461 А 1 (51) 5 (Ol $7/12

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЬ Й КОМИТЕТ СССР

f10 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (46) 23.06.93. Бюл. р 23 (21) 4114899/09 (22) 04.09.86 (72) И.Г.Кашин, !О.А.Мануйлов и Э.А.!Онгблют (56) Патент США У 4106021, кл. 343.5, 1978.

Авторское свидетельство СССР

Ф !111111, кл. 0 01 $ 7/!2, 1983. (54) ЦИФРОВОЙ РАСТРОВЬИ HHQHKATOP (57) Изобретение относится к радиотехнике. Цель иэобретения - повышение быстродействия. Устр-во содержит матричный. блок 3 памяти,ЦАП 5,видеоконтрольный блок б,генератор 9 развертки, коммутатор 10 адреса и преобразователь 11 координат. Введены входной буферный блок 1 памяти, блок 2 постоянной памяти, выходной регистр 4, регистр 7 обратной связи и распределитель 8 импульсов, Работа устр-ва основана на функционировании двух независимых рабочих циклов: записи поступающей с РЛС информации

s блок 3 и непрерывного выхода его содержимого на экран блока 6. Двив кение антенны РЛС от угла азимута

+90o через 0 до +270О и обратно, В зависимости от того, в каком полукадре сканирует антенна, РЛС выраба тывает признак, к-рый поступает на

-1-й управляющий вход блока 2. Он м.б. равным, например, для левого полукадра логич. "0", для правого"1". Тактовые сигналь, вырабатываемые Р. ПС, поступают на синхровходы . распределителя 8 и преобразователя

ll. Распределитель 8 формирует по» следовательности импульсов„ Эти сиг налы управляют приемом информации в блок 1, регистр 4 и рЕгистр 7 и организуют поочередный доступ в блок 3 каждого..функционального цик.па через коммутатор 10. l-й доступ предназначен для вывода содержимого блока 3 ни экран блока 6 через регистр 4 и ЦАП 5 ° 2-й — для записи информации в блок 3. Цикл вывода информации иэ блока 3 на экран блока 6 осуществляе.тся. по строкам или столбцам, адрес к-рых формируется генератором 9 синiсронно с тактами представления l ro ,доступа. 3 ил.

1412461

Изобретение относится к радиотех- ет на своих выходах последавательйосяике и может быть использовано йри ти импульсов согласно временной диапроектированни устройств отображения грамме, представленной на фиг.2. Эти информации, например устройств ото- 5 сигналы управляют приемом информации бражения самолетных метео- и обзорных ва входной буферный блок памяти радиолокационных стаяций (РЛС). выходной регистр 4 и регистр обратной

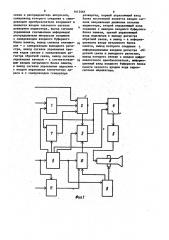

Целью изобретения является павы связи 7 и организуют поачередный шение быстродействия. доступ в матричный блок памяти 3 кажНа фиг.! представлена структурная 10 дага функционального цикла через электрическая схема устройства; на коммутатор !О адреса. Первый доступ фиг.2 - эпюры напряжений на выходах . предназначен для выхода содержимого распределителя импульсов; на фиг.3 - .матричного блока памяти 3 на экран таблица состояний блока постоянной видеокантрального блока 6 через памяти. 15 выходной регистр 4 и ЦАП 5, второй

Цифровой растровый индикатор со- доступ - для записи информации в держит (см.фиг.1) входной буферный . матричный блок памяти 3 блока постоблок памяти I блок постоянной памяти яннай памяти 2.

2, матричный. блок памяти 3, выходной . Цикл записи информации в матричный регистр 4, цифроаналоговый преабраза-20 блок памяти 3 реализован следующим ватель (ЦАП) 5, видеаконтрольный образом, блок 6, регистр обратной связи 7, Коды видеосигналов отдельных уча " распределитель 8 импульсов генера- стков векторов дальностей принимаются тор 9 развертки, коммутатор 10 идре- в РЛС ва входной буферный блок памя са и преобразователь 11 координат, 25 ти 1. Одновременно с этим на выходе

Работа устройства основана на преобразователя 11 координат фармиФункционировании двух независимых руются адреса данных участков в пря рабочих циклов: записи (обновления) . маугольных координатах по асям Х и У, поступающей с РЛС информации в матрич. которые вычисляются преобразовате» ный блок памяти 3 и непрерывного 30 лем 11 для каждого участка к моменту выхода его содержимого на экран . их приема, согласна кодам углов аэи- электронно- лучевой трубки (ЭЛТ) виде мута, поступающим с РЛС на его инокоитральнога блока 6. Дальнейшее, формационный вход в начале развертпояснение принципа рабаты индикатора ки векторов дальностей. В течение ха» проводится для движения антенны РЛС 35 да развертки очередного участка век .. от угла азимута +90 через 0 до тара дальности согласно фиг.2 распре+270 и обратно, т.е, хода антенны делитель 8 импульсов вырабатывает справа налево v. слева направо. Таким управляющие сигналы, пад воэдействиобразом, каждый кадр сканирования ем которых производится обработка и состоит иэ двух полукадрав - левого 40 запись в матричный блок памяти 3 ии» и правого соответственно. В зависи- Формации, полученной н записанной

NocTH oT трго, в каком полукадре во входном буферном блоке памяти 1, сканирует антенна,, РЛС вырабатывает в конце развертки предыдущего участ признак, который поступает на первый ка вектора,Для этого сначала из управляющий вход блока постоянной 45 ячейки матричного блока памяти 3 по памяти 2. Он может быть равным, на- .. адресу, поступающему с выхода преоб пример, для левого палукадра лагичес- разователя II координат и вычисленнокому "0", для правого - "1". . му им за время развертки также предо.

Тактовые сигналы, вырабатываемые дущего участка вектора дальности, РЛС в ходе развертки векторов даль» 50 считывается информация в регистр настей на отдельные участки, количес» обратной связи 7, которая была зане тва которых в ходе развертки каждого сена в данную ячейку ранее при другам вектора равно количеству участков, значении азимута. Данная информация иа ко орые разбивается его длина, кроме кода видеосигнала содержит код что определяется требуемой точностью 5g признака хода антенны, при котором

РЛС и дальностью ее действия, посту- оиа формировалась s РЛС и заппсыва; пают на синхровходы распределителя лась в-матричный блок памяти 3. Блок

8 импульсов и преобразователя ll постоянной памяти 2 формирует на свакоординат. Распределитель 8 формнру ем выходе из двух имеющихся на ега

1412461 входах кодов видеосигналов, поступавших с входного буферного блока памяти 1 и.регистра обратной связи 7 ° а также текущего признака направления 5 движения антенны РЛС информацию по следующему алгоритму: если признаки хода антенны, текущий и считанный из матричного блока памяти 3 в регистр обратной связи 7, совпадают, 10 т.е. обе единицы или оба нуля, то из двух кодов видеосигналов выбирает ся более приоритетный, например, имеющий максимальное значение. В про- тивном случае на выход блока посто- 15 янной памяти 2 подается значение кода видеосигнала с входного буферноГо блока памяти 1, т.е. вновь поступивщее (см.фиг.3, пример алгоритма вы деления максимального сидеосигнала 20 с двумя уровнями градации - "0" и

"1". В реальном случае уровней градации {интенсивностей) видеосигнала может быть четыре и более)..

При наступлении представления очередного второго доступа информация с выхода блока постоянной памяти эа писывается в выбранную ячейку матричного блока памяти 3. Вместе с кодом видеосигнала в ячейку матричного блока памяти 3 заносится также текущий признак кода антенны РЛС. На этом процесс обработки и записи кода видеосигнала участка вектора дальности заканчивается и распределитель 8 импульсов прекращает выдачу сигналов на входной буферный блок памяти 1, выходной регистр 4 и регистр обратной связи 7 и ждет импульса начала нового участка. С его приходом описанный процесс повторяется. Таким образом, эа время хода полукадра в матричный блок памяти 3 занесется информация всех векторов дальностей сканирования антенны РЛС в преобразовайных прямоугольных координатах.

Причем при записи в одну и ту же ячейку матричного блока памяти 3 информации групп участков видеосигналов от одного или нескольких соседних векторов дальностей, возникающей вследствие преобразования систем координат, будет произведен отбор и запись в данную ячейку более приоритетного сигнала иэ данной группы.

В течение следующего полукадра информация в ячейках матричного блока па,мяти 3 сменится.

Цикл вьгвода информации иэ матричного блока памяти 3 на экран видеоконтрольного блока 6 осуществляется по строкам или столбцам, адрес которых формируется генератором 9 развертки синхронно с тактами представления первого доступа согласно фиг.2 формируемыми непрерывно распределителем 8 импульсов. Для непрерывной подачи видеосигнала на ЦАП 5, считываемого из матричного блока памяти 3, он предварительно записывается в выходной регистр 4 по сигналам с выхода распределителя 8 импульсов. Выход ЦАП

5 управляет яркостным каналом видеоконтрольного блока 6, а .аналоговый выход сигнала развертки генератора

9 - отклонением луча ЭЛТ, Таким образом, на прямоугольном растре ЭЛТ видеоконтрольного блока 6 формируется изображение, аналогичное изображению на экране индикатора кругового обзора в пределах аэимуталь о о о ного угла +90 — 0 - +270

Таким образом, в предлагаемом индикаторе прием информации с РЛС осуществляется непрерывно, по мере сканирования антенны, с непосредст. венной записью ее в матричный блок памяти 3 вне зависимости от работы генератора 9 развертки. формула изобретения

Цифровой растровый индикатор, содержащий матричный блок памяти, коммутатор адреса, преобразователь . координат, вщ еоконтрольный блок, генератор развертки и цифроаналоговый преобразователь, выход которого соединен с информационным входом видеоконтрольного блока, вход отклоняющей системы которого соединен с ана» логовым выходом сигнала развертки генератора развертки, информационный вход преобразователя координат явля» ется входом кода азимута индикатора, а выход соединен с первым информационным входом коммутатора адреса, второй информационный вход которого соединен с цифровым адресным выходом генератора развертки, а выход " с адресным входом матричного блока памяти, отличающийся тем, что, с целью повышения быстродейст» вия, введены входной буферный блок . памяти, блок .постоянной памяти, вы" ходкой регистр, регистр обратной

5 1412461 6 связи и распределитель импульсов, развертки, первый управляющий вход сиихровход которого соединен с синх блока постоянной является входом сигровходом преобразователя координат и . нала направления двиаеиня антенны является входом тактового сигнала индикатора., второй управляющий вкод развертки индикатора, выход. сигнала . соединен с выходом входного буферного

5. управления считыванием информацнФ блока памяти, третий управляющий распределителя импульсов соединен вход подключен к выходу регистра с синхровходом входного буферного обратной связй, а выход - и информабЛока памяти, выход сигнала считыва . п ционному входу матричного блока ния с сннхровходом выходного реги- памяти, выход которого соединен с стра, выход сигнала управления при". информационными входами регистра,об ема кодов связан с синхровходом ре- ратной связи и выходного регистра, гнстра обратной связи, выход сигнала : выход которого связан с входом цнфро . управления записью - с соответствую- yg аналогового преобразователя, информа-, щнм входом матричного блока памяти, ционный вход. входного буферного блока а выход сигнала управления адресами - памяти является входом кода видеос входом управления коммутатора ад- сигйала индикатора, реса и с синхровходом генератора

1412461

Составитель Д.Певцов

Редактор И,Кузнецова Техред.А.Кравчук Корректор Г.Ренетник

Заказ 2377

Тираж Подписное

В11ИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская иаб., д. 4lS

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4