Электрометрический вольтметр

Иллюстрации

Показать всеРеферат

Изобретение может быт использовано при измерении малых токов и больших сопротивлений. Электрометрический вольтметр (ЭМВ) содержит источник 3 опорного напряжения, входные шины (Ш) 2, 4, 23, интегратор 1., компаратор 14, блок (в) 16 управления и обработки информации, Б 6, 8 выборки и хранения, ключи 7, 10, фильтр 5 нижних, частот, сумматор 1 1 , 3,. инвертор 9, аналого-цифровой преобразователь 12. ЭМВ имеет повьшенную точность измерений. 6 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМ У СВИДЕТЕЛЬСТВУ

Ех

ГОСУДАРСТВЕННЫИ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21 ) 41 25085/24-21 (22) 25.09.86 (46) 30,07.88, Бюл. В 28 (72) А.А. Володкевич и К.С. Высоцкий (53) 621.325(088.8) (56) Авторское свидетельство СССР

9,1370580, кл. G Ol R )9/12, 1986. (54 } ЭЛЕКТРОМЕТРИЧЕСКИЙ ВОЛЬТМЕТР (57) Изобретение может быть использовано при измерении малых токов и (19) 1И)

15Р 4 G 01 В 19/00// G 01 В 19/12 больших сопротивлений. Электрометрический вольтметр (ЭМВ) содержит источник 3 опорного напряжения, входные шины (Ш) 2, 4, 23, интегратор

1., компаратор 14, блок (Б) 16 управления и обработки информации, Б 6, 8 выборки и хранения, ключи 7, 10, фильтр 5 нижних частот, сумматор 11, 13, инвертор 9, аналого-цифровой пре.образователь 12. ЭМВ имеет повышенную точность измерений. 6 ил.

1413538

Изобретение относится к измерительной технике и может быть использовано при измерении малых токов и больших сопротивлений.

Цель изобретения — повышение точности измерений.

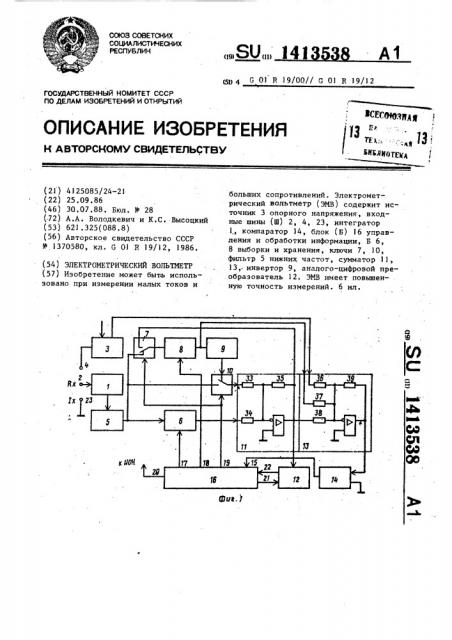

На фиг. 1 представлена схема электрометрического вольтметра1 на фиг,2— пример реализации блока управления 1О и обработки информации (БУОИ); на фиг. 3 — пример построения схемы управления, входящей в состав БУОИ; на фиг, 4 — пример построения схемы микропроцессорного контроллера 15 (МПК) БУОИ1 на фиг. 5 и 6 — времен-. ные диаграммы работы устройства.

Электрометрический вольтметр (фиг. 1) содержит интегратор 1 малых токов, вход которого подключен 20 к входной шине 2, источник 3 опорных напряжений (ИОН), первый выход которого подключен к входной шине 4, подключенный к выходу интегратора фильтр 5 нижних частот, к выходу которого подключены первый блок 6 выборки и хранения и через ключ 7 второй блок 9 выборки и хранения, связанный через инвертор 9 с одним иэ входов ключа 10, сумматор 11, один иэ двух входов которого подклю" чен к выходу ключа 10, другой — к выходу блока 6 выборки и хранения, а выход — к входу аналого-цифрового преобразователя (AI3I) 12 и к одному из трех входов сумматора 13, компаратор 14, подсоединенный к одному из входов (15) БУОИ 16 с управляющими выходами 17-21 и входом 22 от

АЦП 12 и входную шину 23. Второй 40 вход сумматора 13 подключен к выходу блока 8 выборки и хранения, а третий;вход — к ИОН 3.

ИОН 3 выполнен по схеме преобразо. вателя с умножением напряжения и 45 предназначен для формирования опорных уровней напряжений 0,1, 1, 10, 100 и 1000 В при измерении сопротивления постоянному току. Выходные напряжения снимаются с высоковольтнОго 50 делителя и коммутируются с помощью реле на шину 4, а напряжение 10 В постоянно подключен к третьему входу сумматора 13.

Блоки 6 и 8 выборки и хранения выполнены на базе двух операционных усилителей по инвертирующей схеме.

БУОИ 16 может быть выполнен, как показано на фиг. 2, и содержит ИПК

24, оперативное запоминающее устройство (ОЗУ) 25, постоянное запоминающее устройство (ПЗУ) 26, счетчик

27, формирователь 28 временных интервалов (ФВН), интерфейс 29, схему 30 управления, дешифратор устройства 31 и блок 32 индикации и клавиатуры.

ОЗУ 25 предназначено для запоминания данных цифрового преобразования и хранения промежуточных результатов при выполнении программы измерения.

ФВИ 28 выполнен на БИС программируемого таймера.

Интерфейс 29 формирует сигнал управления режимом работы устройства (режим измерения тока или сопротивления), команду "Запуск", управляющие сигналы для ИОН 3, а также передает в шику данных команду "Знак" из. схемы 30 управления и выполнен на БИС программируемого параллельного интерфейса.

Дешифратор 31 обеспечивает выбор . адресуемого MIK 24 устройства:ИПК 24, ОЗУ, 25, ПЗУ 26, счетчика 27, ФВИ 28, интерфейса 29, блока 32 индикации и клавиатуры.

Блок 32 индикации и клавиатуры обеспечивает функционирование устройства в целом и отображает результаты измерения.

Примеры реализации ИПК 24 и схемы

30 управления приведены соответственно на фиг. 3 и 4.

МПК 24 производят централизованное управление всеми узлами и блоками устройства и осуществляет процесс цифровой обработки информации.

Схема 30 управления обеспечивает управление блоками устройства, с помощью которых производится дискретизация напряжения интегратора 1 (блоки

6 и 8, ключи 7 и 10), и выполнена на интегральных микросхемах средней степени интеграции с малым энергопотреблением, Сумматоры 11 и 13 выполнены на ба эе операционных усилителей и содержит также резисторы 33-35 (сумматор

11) и 36-39 (сумматор 13).

На фиг. 5 приведены диаграммы работы устройства в режиме измере" ния тока: а — форма сигнала на управляющем входе блока 6 выборки и хранения; б — форма сигнала на управляющем входе блока 8 выборки и хранения, в — форма сигнала на вы14135

dU — — I

dt С

40 ходе 21 БУОИ 6; r — форма сигнала

"Знак" на выходе схемы 30 управления; д — диаграмма 1 — сигнал на выходе интегратора 1 (иа диаграмме ин- . 5 вертирован), диаграммы 2 и 3 — сигналы на выходах блоков 6 и 8, е— форма сигнала на выходе сумматора 11.

На фиг. 6 приведены диаграммы работы устройства в режиме измерения 1О сопротивления: а — форма сигнала "3aпуск" на выходе интерфейса 29 БУОИ

16; б — форма сигнала на выходе компаратора 14; в — форма сигнала на управляющих входах блоков 6 и 8, r — - !5 диаграмма I — сигнал на выходе интегратора l (на диаграмме инвертирования), диаграмма 2 — сигнал на выходе блока, д — форма сигнала ка выходе сумматора 11, е — форма сигнала 20 на выходе сумматора 13, ж — форма сиг-. нала на выходе R схемы 30 управления БУОИ 16.

В режиме измерения тока источник измеряемого тока подключается между входными шинам 2 и 23. Управление всеми узлами устройства осуществляет

БУОИ 16. При этом вход блока 8 через ключ 7 подсоединяется к фильтру 5, а инвертор 9 через ключ 10 подключается к входу сумматора 11 (фиг. !).

При поступлении измеряемого тока Т на вход интегратора l на его выходе появляется линейно изменяющееся напряжение (фиг. 5д, диаграмма 1) ско35 рость изменения которого прямо пропорциональна величине тока: где С вЂ” измерительный конденсатор в цепи обратной связи интегратора I.

Блоки 6 и 8 осуществляют дискретизацию выходного напряжения интегратора 1 через интервал времени pt„ (фиг. 5д, диаграммы 2 и. 3), величина которого задает БУОИ 16 (в данном случае 100 мс) по выходам 17 и 18

50 (фиг. 5а,б) и определяется из условий определения минимально возможного приращения напряжения pU (зависит от уровня шумов входных цепей

55 интегратора 1), необходимого быстродействия выдачи данных, помехоустойчивости устройства (интервал дискретизации должен быть кратным периоду

38

4 помехи, в частности напряжению питающей сети)

Выделение напряжения д11, амплитуда которого прямопропорциональна

Ф

C aU величине измеряемого тока (I х

dt эа интервал времени д t„ осуществляет сумматор ll с коэффициентом передачи

К в моменты времени ht, (фиг. 5е),-С помощью интегрирующего АЦП 12 и счетчика 27 БУОИ 16 производится измерение величины К 4U в моменты времени д1, определяющие время интегрирования АЦП 12, которое должно быть крат но периоду помехи, в частности напряжению питающей сети, и выбирается в.зависимости от необходимого быстродействия и точности измерения (в данном случаем 20 мс). Время Dt (фиг.5a) задается ФВИ 28 по выходу 21 БУОИ 16 после установления блоков 6 и 8 в режиме хранения.

Результат измерения тока определяется как полусумма двух соседних результатов аналого-цифрового преобразования К bU„v К 4U;+, .

- Для правильного определения полярности измеряемого тока (отрицательного либо положительного) схемой 30 управления по выходу "Знак" формируется соответствующий сигнал (фиг.5г) который анализируется в момент времени дС, МПК 24: при наличии уровня "1" на интервале bt, (фиг. Sr) знак результата измерения АЦП инвертируется, при наличии "О" знак результата измерения АЦП сохраняется.

Так как результат измерения А определяется при сложении двух соседних данных . А; и А;,, АЦП 12, которые имеют разную полярность, то на процесс измерения адаптивные погрешности (напряжение смещения и его временной и температурный дрейф) не оказывают влияния."

-(-А;+Есм)+(А;- +Есм)

У„

2 где Е „, — суммарное напряжение смещения интегратора 1, фильтра 5, блоков

6 и 8, инвертора 9, сумматора 1) с учетом знака и коэффициентов передачи соответствующих звеньев.

На фиг. 5д показана смена полярности напряжения на выходе интегратора (диаграмма I), вызванная иэме1413538 нением полярности входного тока, на фиг. 5е отображены соответствующие изменения в сигнале на выходе сумматора Il.

В режиме измерения сопротивления

Измеряемый объект В„подключается между входными шинами 2 и 4. При этом от ИОН 3 подается одно из измери " тельных напряжений U (например, 0,1, 1, IO 100 или 1000 В), значения которого устанавливается по управляющему выходу 20 БУОИ 16. Уровнем "1" по выходу 19 подключается вход сумматора Il.÷åðåç ключ 10 к фильтру 5 нижних частот, а вход блока 8 через ключ 7 — к выходу сумматора 11.

В исходном состоянии блоки 6 и 8 находятся в режиме слежения. Блок 6 инвертирует выходной сигнал интегратора 1 (фиг. 5), который суммируется с прямым сигналом интегратора (фиг. 5д), Резисторы 33 и 34 равны по величине, а на выходе сумматора

11 присутствует напряжение смещения

Е, обусловленное совместным действием напряжений смещения блока 6 и сумматора )1. Сумматор 13 произво-. дит суммирование напряжений с блока 8 и сумматора ll, и влияние напряжения смещения Е ослабляется в

m раз (m — коэффициент передачи сумматора 11, определяемый соотношением резисторов 35, 33 и 34, в данном случае m = 100), т.е. устраняется аддитивная составляющая погрешности. С второго выхода ИОН 3 на третий вход сумматора !3 подается опорное напряжение U „ (например, lO В), .устанавливайщее компаратор

14 в состояние "О" по входу 15, Напряжение и резисторы 36-38 определя ют порог срабатывания компаратора 14.

Процесс измерения начинается по команде "Запуск" (фиг. 6а), генерируемой MIIK 24 через интерфейс 29.

При этом БУОИ 16 по выходам )7 и 18 (фиг. 6в) переводит блоки 6 и 8 в режим хранения.

Сумматор 11 производит выделение приращения напряжения ЬБ, которое сравнивается сумматором 13 с фиксированным напряжением U, при достижении которого срабатывает компаратор 14 (фиг, 5б)

Одновременно с приходом команды запуск на выходе В схемы 30 управления БУОИ 16 появляется информацион- ный импульс (фиг. 6ж), измерение длительности которого производится счетчиком 27 ° Считывание информации из счетчика производится KIK 24 по окончании информационного импульса (момент фиксации уровня срабатывания компаратора 14), Интервал времени от начала работы устройства (прихода команды "Запуск" ) до срабатывания компаратора является информационным и прямопропорционален величине измеряемого сопротивления R„, 5

tO 4 м t u

= К вЂ” — у

U. где К вЂ” суммарный коэффициент передачи тракта блока 6 и сумматоров

il и 13.

Для уменьшения случайных помех, повышения помехоустойчивости в режимах измерения тока и сопротивления

БУОИ )6 выполняет цифровую фильтрацию сигнала путем усреднения N реэультатов измерения. При этом в зависимости от диапазона измерения и условий применения постоянная времени . изменяется в пределах от О,) до )00 с (устанавливается оператором через блок 32 индикации и клавиатуры). а

Формула из обретения

Электрометрический вольтметр, содержащий источник опорного напряжения, соединенный с первой входной шиной, интегратор, своим входом соединенный с второй входной шиной, третью входную шику, подключенную к общей шине, последовательно соеди40 денные компаратор, блок управления и обработки информации и первый блок выборки -и хранения, первый ключ, первый вход которого соединен с вторым входом первого блока выборки и хранения, отличающийся тем, что, с целью повышения точности измерений, в него введены фильтр нижних частот, первый сумматор и последовательно соединенные второй блок выборки и хранения, инвертор, второй ключ, второй сумматор и аналогоцифровой преобразователь, выход которого подключен к, второму входу, а второй вход — к второму выходу блока управления и обработки информации, третий, четвертый и пятый выходы которого подключены соответственно к источнику опорного напряжения, к первому входу второго блока выборки и ъ

1413538

1О

+50

Фиг.2 хранения и к управляющим входам обоих плеч, первые входы которых объединены и подключены к выходу фильтра нижних частот и к второму входу первого блока выборки и хранения, второй вход первого ключа соединен с первым входом первого сумматора и с выходом второго сумматора, выход первого ключа подключен к второму входу второго блока выборки и хранения, выход которого .соединен с вторым входом первого сумматора, третий вход которого подключен к источнику опорного напряжения, а выход — к первому входу компаратора, второй вход которого подключен к общей шине, при этом выход интегратора подсоединен к входу фильтра нижних частот, а выход первого блока выборки и хранения — к второму входу второго сумматора.

1413538

14l 3538

1413538! 4! 3538

Со с тавитель Е . Ефимо в

Техред Л. Олийнык

Редактор А. Огар

Корректор С, Черни

Тираж 772

ВПИИПИ Государственного комитета СССР по делам изобретений и открытий

)13035, Москва, 8-35, Раушская наб., д. 4/5

Заказ 3778/47

Подписное

Производственно-полиграфическое предприятие, r. ужгород, ул. Проектная, 4