Устройство для вычисления функций двух аргументов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и позволяет расширить класс решаемых задач за счет вычисления функций, не представляемых в виде произведения функций первого и второго аргументов. Устройство содержит регистры первого 1 и второго 2 аргументов, блок 3 синхронизации , блок 4 памяти, в котором хранятся логарифмы модулей и знаки коэффициентов аппроксимации мультиплексоры 5 и 3, блок 6 памяти, в котором хранятся логарифмы приращений первого и второго аргументов, буферные регистры 7 и 11, сумматоры 9 и 10, блок 12 памяти, который осуществляет потенциирование с основанием два, комбинационный сдвигатель 13, управляемый инвертор 14 и накапливающий сумматор 15, формируняций результат вычислений. 1 з.п,ф-лы, 3 шт. (Л с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (50 4 G 06 F 7/544

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21 ) 41 60877/24-24 (22) 15.12. 86 (46) 30.07,88. Бюл. У 28 (71) Воронежский технологический институт (72) Ю.П.Барметов, С.А.Боев и Ю.И,Евтеев (53) 681. 325 (088. 8) (56) Авторское свидетельство СССР

N- 1191917, кл. С 06 F 15/31, 1983.

Авторское свидетельство СССР

М 1123034, кл. G 06 F 15/20, 1983. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ ДВУХ АРГУМЕНТОВ (57) Изобретение относится к вычислительной технике и позволяет рас: ширить класс решаемых задач эа счет

„„Я0„„1413626 А1 вычисления функций, не представляемых в виде произведения функций первого и второго аргументов. Устройст" во содержит регис ры первого 1 и второго 2 аргументов, блок 3 синхронизации, блок 4 памяти, в котором хранятся логарифмы модулей и знаки коэффициентов аппроксимации, мультиплексоры 5 и 3, блок 6 памяти, в котором хранятся логарифмы приращений первого и второго аргументов, буферные регистры 7 и 11, сумматоры 9 и 10, блок 12 памяти, который осуществляет потенциирование с основанием два, комбинационный сдвигатель 13 управляемый инвертор 14 и накапливающий сумматор 15, формирующий результат вычислений. 1 з.п.ф-лы, 3 ил.

1413626

Р(х9у) а z,, +a „; д х +a; д х +а >,ду+

+ а, -.ду+ à, д хду9 (1) где х=х;+дх9у-=у; + a у, (х; 9 у;) — начальная точка участка аппроксимации; коэффициенты аппр окс ими 50 рующего многочлена, зависящие от аппроксимируемой функции и начальной точки (х,у),в окрестйости

Изобретение относится к вычислительной технике, предназначено для вычисления функций двух переменных и может быть использовано в цифро5 вых быстродействующих специализированных вычислительных устройствах информационно-измерительных систем, систем управления.

Цель изобретения — расширение класса решаемых задач эа счет вычисления функций, не представляемых в виде произведения функций первого и второго аргументов.

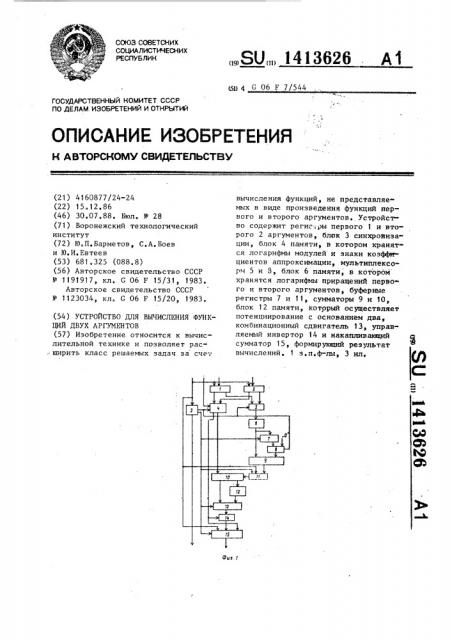

На фиг. 1 изображена функциональная 15 схема предложенного устройства; на фиг.2 и 3 — функциональные схемы комбинационного сдвигателя и блока синхронизации, соответственно.

Устройство содержит регистры пер- 20 вого 1 и второго 2 аргументов, блок 3 синхронизации, первый блок 4 памяти, мультиплексор 59 второй блок 6 памяти, первый буферный регистр 7, мультиплексор 8, первый и второй сумматоры 9 и 25

1 10, второй буферный регистр 11, третий блок 12 памяти, комбинационный сдвигатель 13, управляемый инвертор

14, накапливающий сумматор 15. Комбинационный сдвигатель 13 (фиг.2) содер.30 жит блок 16 постоянной памяти, группу мультиплексоров 1 / и регистр 18.

Блок 3 синхронизации (фиг.3) состоит из генератора 19 импульса и двоичношестиричного счетчика 20.

Устройство вычисляет значения функции в заданной точке (х, у) путем кусочно-квадратичной аппроксимации исходной функции полиномом которой осуществляется аппроксимация.

Значения коэффициентов А

О,1 9 ° ° ° 9

aS . Определяются либо методом наименьших квадратов иэ условия минимизации суммы квадратов погрешностей, либо же из условий минимизации максимальной погрешности. Коды х.,дх и

1 у,, ду формируются соответственно ,старшими и младшими разрядами аргументов.

Чтобы исключить операции умножения выражение (1) преобразуют к виду ф g ("О1

Р(х у) sign(a ) 2 +sign, «о, С„.). coy,дх3 (а, ) х 2 2

1„

ГЕ 2(2, ) " "

2, + (е.,(.„>9 е.,дч)

+sign(a> 2

C ro«(+,,) +< to<<»3

+sign(aq,„) х 2

+ еО „(a<;)iloq28x+4<8 3

+sign(a ; ) 2 (2) Логарифмы модулей коэффициентов и знаки коэффициентов хранятся в первом блоке 4 памяти, логарифмы дх, dy — во втором 6. Коды аргументов заносятся в регистры 1 и 2.

Устройство работает следующим образом.

При занесении первого и второго аргументов в регистры 1 и 2 строб занесения, поступающий по входу запуска устройства, обнуляет накапливающий сумматор 159 регистр 11 и счетчик 20 блока 3 синхронизации.

Одновременно с подачей на входы устройства аргументов или несколько ранее на вход задания функции устройства выставляется код вычисляемой функции. Из блока 4 памяти считывается логарифм модуля нулевого коэффициента в виде целой части со знаком и положительной дробной части и пересылается на вход первого слагаемого сумматора 10, на вход второго слагаемого которого из регистра 11 подается код нуля, дробная часть значения логарифма модуля нулевого коэффициента поступает в блок 12 памяти, из которого антилогарифм дробной части пересылается по информационному входу в комбинационный сдвигатель 13. г.сли целая часть логарифма положи3 i 4136 тельная и отлична от нуля, Koll, антилогарифма сдвигается на группе мультиплексоров 17 влево на число позиций, равное целой части логарифма, если отрицательная — сдвиг производится вправо.

С целью уменьшения количества мультиплексоров 17 в группе сдвиг выполняется в два приема: в течение положительного полутакта синхросигна10 ла, поступающего на старший разряд адресного входа блока 16 постоянной памяти, на выходы мультиплексоров 17 пересылается младшая часть формируемого числа, заносится в регистр 18

15 и с выходов этого регистра поступает на выход сдвигателя 13 (младшие разряды); в течение отрицательного полутакта на выход мультиплексоров проходит старшая часть, подаваемая не20 посредственно на выход сдвигателя 13.

Приведенный таким образом к форме с фиксированной запятой код нулевого коэффициента, проходя управляемый ин?5 вертор 14, либо инвертируется, если знак коэффициента, поступающий с второго выхода блока 4 памяти на управляющий вход инвертора, равен единице (коэффициент отрицательный), либо остается без изменений при нулевом знаковом разряде. Так как накапливающий сумматор 15 в момент занесения аргументов был обнулен, нулевой коэффициент просто записывается во внутренний регистР накапливающего сумма- 35 тора 13 положительным фронтом синхросигнала, поступающего на его стробовый вход.

Параллельно с преобразованиями нулевого коэффициента мультиплексор 40

5 пропускает на адресный выход блока .6 памяти код младшей части первого аргумента, с блока 6 памяти считывается логарифм по основанию два младшей части аргумента и это значе- 45 ние поступает на вход второго слагаемого сумматора 9 и информационный вход буферного регистра 7. На вход ! первого слагаемого сумматора 9 мультиплексор 8 подает код нуля. Лога- 50 рифм младшей части первого аргумента, проходя через сумматор 9 положительным фронтом синхросигнала, заносится в буферный регистр 11.

Этот же положительный фронт синхросигнала увеличивает код счетчика

20 на единицу, что приводит к изменению адреса блока 4 памяти и управляющего кода мультиплексоров 5 и 8.

26 1

С первого выхода блока 4 памяти считывается код логарифма модуля первого коэффициента и в сумматоре 10 складывается с логарифмом младшей части первого аргумента, поступающим с регистра 11, причем дробная часть получается всегда положительная, а целая может быть как положительной, так и отрицательной.

Логарифм дробной части потенциируется в блоке 12 памяти, сдвигается комбинационным сдвигателем !3 и суммируется в накапливающем сумматоре

15 с учетом знака, поступающего на управляющий вход инвертора 14, со значением нулевого коэффициента.

Б это же время мультиплексор 5 пропускает на выход младшую часть первого аргумента, а мультиплексор 18код с выхода регистра 7, и на выходе сумматора 9 образуется удвоенный код логарифма младшей части первого аргумента, что соответствует логарифму квадрата этого числа. Полученное значение фиксируется в регистре 11 и на следующем такте суммируется с логарифмом второго коэффициента. Таким образом, процесс повторяется, с той лишь разницей, что на каждом новом такте синхросигнала с блока 4 памяти считывается логарифм модуля следующего коэффициента, мультиплексор 5 на третьем и четвертом тактах пропускает код младшей части второго аргумента, на пятом и пестом — младшей части первого аргумента, мультиплексор 8 на третьем такте пропускает код нуля, а на четвертом, пятом и шестом - код с выхода регистра 7. После прохождения шести тактов синхросигнала в накапливающем сумматоре 15 сформируется значение вычисляемой функции, а еди-. ничный код в старшем разряде счетчика

20 запретит работу генератора 19 им пульсов, что расценивают как признак готовности результата, Таким образом, введение новых блоков и связей позволяет реализовать алгоритм кусочно-квадратичной аппроксимации, приемлемый для множества. гладких функций двух переменных, включающего в себя более узкое подмножество функций с разделяющимися аргументами, и, таким образом, решить поставленную задачу о расширении класса вычисляемых функций.

1413626

Ф <> р м у л а и з о б р е т е н и я

1. Устройство для вычисления функций двух аргументов, содержащее регистры первого и второго аргументов, два мультиплексора, два буферных регистра, три блока памяти, первый сумматор, накапливающий сумматор, комбинационный сдвигатель, блок синхронизации, информационные входы регистров первого и второго аргументов являются входами первого и второго аргументов устройства соответственно, выход старших разрядов регистра первого аргумента соединен с первым адресным входом первого блока памяти, выход первого буферного регистра соединен с первым информационным входом первого мультиплексора, выход кото- 20 рого соединен с входом первого слагаемого первого сумматора, выход которого соединен с информационным входом второго буферного регистра, выход третьего блока памяти соединен с ин- 25 формационным входом комбинационного сдвигателя, выход накапливающего сумматора является выходом результата устройства, первый выход блока синхронизации соединен с вторым адресным входом первого блока памяти и управляющими входами первого и второго мультиплексоров, второй выход блока синхронизации соединен с входами синхронизации первого и второго буферных регистров, комбинационного сдвигателя и накапливающего сумматора, о т л и ч а ю щ е е с я тем, что, с целью расширения класса решаемых задач за счет вычисления функций, не

40 представляемых в виде произведения функций первого и второго аргументов, в него введены второй сумматор и управляемый инвертор, информационный вход и выход которого соединены с выходом комбинационного сдвигателя и информационным входом накапливающего сумматора соответственно, выход

1 старших разрядов регистра второго ар-. гумента соединен с третьим адресным входом первого блока памяти, первый выход которого соединен с входом первого слагаемого второго сумматора, вход второго слагаемого которого соединен с выходом второго буферного регистра, выходы дробной и целой частей результата второго сумматора соединены с адресным входом третьего блока памяти и входом управления величиной сдвига комбинационного сдвигателя соответственно, второй выход первого блока памяти соединен с управляющим входом управляемого инвертора и с входом переноса накапливающего сумматора, выходы младших разрядов регистров первого и второго аргументов соединены с первым и вторым информационными входами второго мультиплексора, выход которого соединен с адресным входом второго блока памяти, выход которого соединен с информа- —, ционным входом первого буферного регистра и входом второго слагаемого первого сумматора, второй информационный вход перого мультиплексора соединен с входом логического нуля устройства, вход запуска которого соединен с входами записи регистров первого и второго аргументов и с входами сброса блока синхронизации, второго буферного регистра и накапливающего сумматора, выход признака окончания цикла блока синхронизации является выходом признака готовности результата устройства.

2. Устройство по п,i, о т л и ч аю щ е е с я тем, что,с целью увеличения числа вычисляемых функций, четвертый адресный вход первого блока памяти является входом задания функции устроиства.

141 362б

Составитель А. Ушаков

Техред Л.Олийнык Корректор M.Ïîæo

Редактор M.Kåëåìåø

Подписное

Тираж 704

Заказ 3787/52

В11ИИПИ Государственного комитета СССР по делам изобретений и открьггий

113035, Москва, И-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4