Фазовый синхронизатор

Иллюстрации

Показать всеРеферат

СОЮЗ СО8ЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

И) 4 Н 03 К 5/135

ВСЕГОЮЗИФ Я!

3 „ .,13

ЙЫЛНОТЕ1(А

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCMOlVIV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1309279 (2!) 4206971/24-21 (22) 23.01 .87 (46) 30. 07.88. Бюл. N 28 (72) С.А.Колесов, Ю.В.Соколов, В.В.Бовырин и В.Г.Семенов (53) 621.374 (088.8) (56) Авторское свидетельство СССР

N 1309279, кл. Н 03 К 5/135, j10.01.86. (54) ФАЗОВЫЙ СИНХРОНИЗАТОР (57) Изобретение относится к устройствам импульсной техники и может быть использовано в качестве элемента временной привязки периодического сигнала к внешнему .асинхронному сигналу в системах синхронизации,;SUÄÄ 1413708

ЭВМ. Цель изобретения — повышение точности синхронизации — достигается за счет учета тока производных входного и ортогонального к нему сигналов в момент синхронизации, что обеспечивает надежность синхронизации ЭВМ. Фазовый синхронизатор содержит входные шины 1 и 19, элемент

2 задержки, аналоговые запоминающие устройства 3 и 4, устройства 5 и 6 выделения модуля, компараторы 7

l1, D-триггеры 12, 13 и 14, коммутаторы 15, 16 и 17, выходную шину

18. Устройство обеспечивает высокую точность и позволяет получить относительную погрешность фазовой синхро ниэации менее 1Х что на два порядка выше, чем у прототипа. 1 ил.

1413708

Изобретение относится к элементам импульсной техники, может приме-. няться в качестве элемента временной привязки периодического сигнала к внешнему асинхронному в системах синхронизации ЭВМ и является усовершенствованием известного по авт. св. 9 1309279.

Цель изобретения — повьппение точ- 10 ности синхронизации за счет учета тока производных входного и ортогонального к нему сигналов в момент синхронизации, что обеспечивает надежность синхронизации ЭВМ. 15

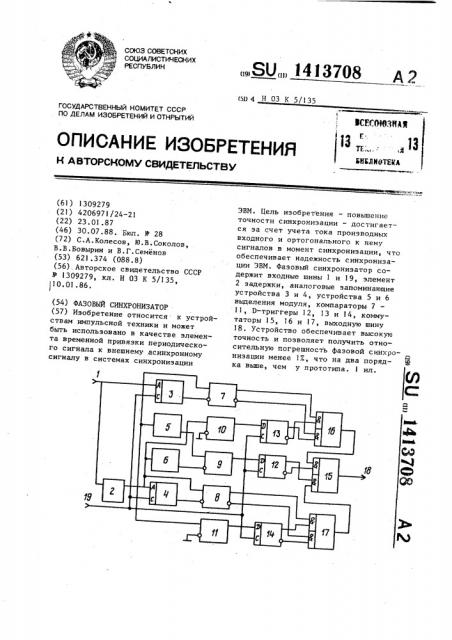

На чертеже приведена электрическая структурная схема фазового синхронизатора.

Фазовый синхронизатор содержит первую входную шину 1, элемент 2 за- 20 держки, первое и второе аналоговые запоминающие устройства АЗУ 3 и 4, первое и второе устройства 5 и 6 ,выделения модуля УВМ, первый, второй, третий, четвертый и пятый компарато- 25 ры 7 — 11, первый, второй и третий

П-триггеры 12 — 14, первый, второй и третий коммутаторы 15 — 17, выходную шину 18 и вторую входную шину 19. ,Первая входная шина 1 соединена со 30 входом элемента 2 задержки, с аналоговым входом первого АЗУ 3, со входом первого УВМ 5 и с прямыми входами первого и пятого компараторов 7 и 11. Вторая входная шина 19 соединена со входами синхронизации первого и второго АЗУ 3 и 4 и С-входами первого, второго и третьего D-триггеров 12 — 14. Выход элемента 2 задержки соединен с аналоговым входом вто- 40 рого АЗУ 4, со входом второго УВМ 6 и с прямыми входами второго и четвертого компараторов 8 и 10. Выходы первого и второго УВМ 5 и 6 соединены соответственно с прямым и инверсным входами третьего компаратора 9, выход которого соединен с D-входом первого Э-триггера 1 2. Инверсный вход четвертого компаратора 10 соединен с общей шиной выход — с D-входом вто9

50 рого D-триггера 13. Инверсный выход пятого компаратора 11 соединен с общей шиной, выход — с Р-входом третьего D-триггера 14. Инверсные входы первого и второго компараторов 7 и 8 соединены с выходами соответственно

59 первого и второго АЗУ 3 и 4. Выходная шина 18 соединена с выходом первого коммутатора 15, первые входы первого и второго конъюнкторов ко торого соединены соответственно с инверсным и прямым входами первого

D-триггера 15. Вторые входы первого и второго конъюнкторов первого коммутатора 15 соединены с выходами соответственно второго и третьего коммутаторов 16 и 17. Инверсный и прямой выходы второго D-триггера 13 соединены с первыми входами соответственно первого и второго конъюнкторов второго коммутатора 16 ° Прямой и инверсный выходы третьего D-триггера 14 соединены с первыми входами соответственно первого и второго конъюнктоу ров третьего коммутатора 17. Вторые входы первого и второго конъюнкторов второго коммутатора 16 соединены соответственно с прямым и инверсным выходами первого компаратора 7. Вторые входы первого и второго конъюнк-i торов третьего коммутатора 17 соединены соответственно с прямым и инверсными выходами второго компаратора 8.

Устройство работает следующим образом.

На шину 1 поступает гармонический сигнал

2п

U = А cos — — t"

Т после прохождения элемента задерж" ки, время задержки которого составляет t > = Т/4, сигнал имеет вид:

2Р

Ug= А cos (— -t + — -)

Т 2

2я

А sin — -й.

Т

Сигналы U< и U поступают на входы УВМ 5 и 6, на выходах которых соответственно формируются сигналы—

IU, и 1V,l, На выходе компаратора 9 присутствует уровень "1" ("0") в те моменты времени, когда скорость изменения сигнала U больше (меньше), чем U, . На -выходах компараторов 10 и 11 формируется уровень "1" ("0") в те моменты времени, когда мгновен", ные значения U< и U больше (меньше) нуля. Учитывая, что U = U u

U1 -Ug, логические уровни напряжений на выходах компараторов 10 и

11 соответствуют мгновенным знакам производных U< и U .

В некоторый момент времени на шину 19 приходит асинхронный сигнал, 1413708

Формула изобретения

Составитель А.Соколов

Редактор H.Ãîðâàò Техред И.Дидык Корректор Л.Пилипенко

Заказ 3793/56 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1)3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

3 по которому на выходах АЗУ 3 и 4 фор" мируются уровни напряжений U и U< соответственно, равные мгновенным значениям напряжений 1 и 2 в этот момент времени, Эти напряжения поддерживаются на инверсных входах компараторов 7 и 8 в качестве опорных.

D-триггеры )2 — 14 в этот момент .времени фиксируются в состояниях, 10 соответствующих логическим уровням на их D-входах. На выходах компараторов 7 и 8 формируются импульсные периодические сигналы, фронты переключения KQTopblx соответствуют мо- 15 ментам пересечения напряжениями )) и Ug опорных уровней U< и U<, Коммутаторы 16 и 17 в соответствии с управляющими напряжениями, поступающими с выходов В-триггеров 13 и 14, пропускают сигналы с выходов компараторов 7 и 8 так, чтобы на вы ходах коммутаторов 16 и 17 сформировался первый после упомянутого момента времени положительный фронт. 25 ...Коммутатор 15 в соответствии с управляющими напряжениями с выходов

D-триггера 12 пропускает на шину 18 сигнал с выходов компараторов 7 и 8, переключаемых сигналом с большой скоростью изменения.

Таким образом, устройство отличается высокой точностью фазовой синхронизации. При использовании устройства-прототипа относительная погрешность фазовой синхронизации с учетом того, что "рабочими" являются лишь положительные фронты выходного сигнала, может достигать 25Й.

Предлагаемое устройство позволяет получить относительную погрешность фазовой синхронизации менее JX, Фазовый синхронизатор по авт. св. Р )309279, о т л и ч а ю щ и й— с я тем, что, с целью повышения точности, в него введены четвертый и пятый компараторы, второй и третий

D-триггеры, второй и третий коммутаторы, выполненные в виде двойного элемента И-ИЛИ, причем прямой вход четвертого компаратора соединен с вы" ходом элемента задержки, инверсный вход — с общей шиной, выход — с

D"âõîäîì второго D-триггера, инверсный и прямой выходы которого соединены с первыми входами соответственно . первого и второго конъюнкторов второго коммутатора, С-вход — с С-входом . первого D-триггера и с С-входом третьего D-триггера, прямой и ин" версный выходы .которого соединены с первыми входами соответственно первого и второго конъюнкторов третьего коммутатора, D-вход — с выходом пятого компаратора, прямой вход которого соединен с входом элемента задержки, инверсный вход — с общей шиной, при этом прямой и инверсный выходы первого,и второго компараторов через соответственно первые и вторые конъюнкторы соответственно второго и третьего коммутаторов соединены с вторыми входами соответст» венно".первого и второго конъюнкторов первого коммутатора.