Преобразователь постоянного напряжения в многоступенчатое квазисинусоидальное

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике , точнее к преобразователям постоянного напряжения в переменное с квазисинусоидальной или ступенчатосинусоидальной формой выходного напряжения . Цель - повысить надежность работы преобразователя, т.е. исключить возможность сбоев и аварийных ситуаций в работе преобразователя при f скачкообразном изменении напряжения 1 на выходе преобразователя. Для этого в преобразователь введены блок 1 формирования программных сигналов, имеющий выход кода программной синусоиды, выход тактовых импульсов, выход нулевого сигнала, выход управления полярностью , аналого-цифровой преобразователь 2, блок 3 сравнения кодов, имеющий для кодовых входа, выход приоритета числа на первом входе, выход приоритета числа на втором входе, две схема 4 и 5 совпадения, М блоков 7-9 управления ячейками. При появлении сигнала об отклонении выходного напряжения от программного значения на соответствующий вход (суммирующий или вычитающий) реверсивного счетчика 6 поступают тактовые импульсы и выходное напряжение изменяется дискретно до тех пор, пока рассогласование не будет ликвидировано . 9 ил., 1 табл. (Л ел 00 00 Ф1/Г/ Vtta

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„„SU» 1415380 А1 (51)4 Н 02 М 7/48

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2 1) 4063663/24-07 (22) 28.04;86 (46) 07.08.88, Бюл. Р 29 (7.2) И.А. Швынденков, 0.А. Романюха и Ю.А. Середа (53) 621.316. 727 (088.8) (56) Авторское свидетельство СССР

Ф 1246300, кл, Н 02 М 7/48, 1985.

Авторское свидетельство СССР

У 748743, кл. Н 02 М 7/537, 1980. (54) ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ В ИНОГОСТУПЕНЧАТОЕ КВАЗИСИНУСОРЩАЛЬНОЕ (57) Изобретение относится к электротехнике, точнее к преобразователям постоянного напряжения в переменное с кваэисинусоидальнай или ступенчатасинусоидальнай формой выходного напряжения. Цель — повысить надежность работы преобразователя, т.е. исключить возможность сбоев и аварийных ситуаций в работе преобразователя при скачкообразном изменении напряжения 1 на выходе преобразователя. Для этого в преобразователь введены блок 1 формнравания программных сигналов, имеющий выход кода программной синусоиды, выхац тактовых импульсов, выкод нулевого сигнала, выход управления полярнастью, аналого-цифровой преобразователь 2, блок 3 сравнения кодов, имеющий для кодовых входа, выход приоритета числа на первом входе, выход приоритета числа на втором входе, две схема 4 н 5 совпадения, Г1 блоков 7-9 управления ячейками.

При появлении сигнала об отклонении выходного напряжения от программнога значения на соответствующий вход (суммирующий или вычитающий) реверсивного счетчика 6 поступают тактовые импульсы и выходное напряжение изменяется дискретно до тех пор, пока рассогласование не будет ликвидирована. 9 ил., 1 табл.

1415380

Изобретение относится к электротехнике, н частности к преобразователям постоянного напряжения н переменное с квазисинусоидальной или ступенчато-синусоидальной формой, и может быть использовано в установках гарантированного питания потребителей переменного тока, системах автономного электроснабжения, высокоточном электроприводе.

Цель изобретения — поньппение надежности работы преобразователя постоянного напряжения в квазисинусоидальное, 15

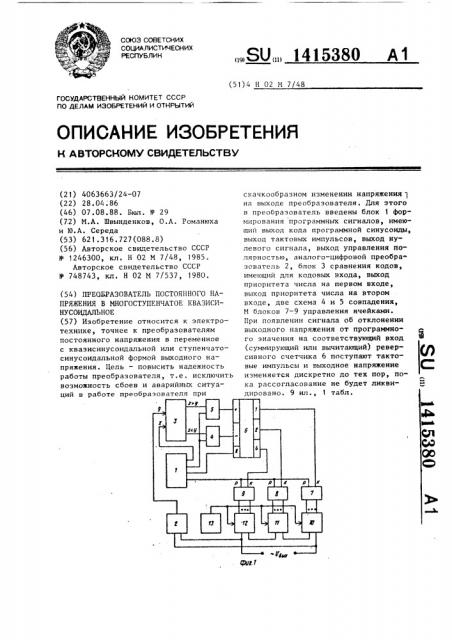

На фиг. 1 приведена функциональная схема преобразователя с тремя силовыми ячейками; на фиг ° 2 — функциональная схема блока формирования программных сигналов; на фиг. 3 и 4 блоки управления силовыми ячейками; на фиг. 5-6 — функциональные схемы силовых ячеек; на фиг. 7 — силовая часть преобразователя, состоящая иэ трех силовых ячеек; на фиг. 8 — табли-25 ца переключений ключей, на фиг. 9 временные диаграммы работы ключей.

В состан преобразонателя (фиг. 1) входят блок 1 формирования программных сигналов, аналого-цифроной преобразователь 2, блок 3 сравнения кодов, дне днухнходовые схемы 4 и 5 совпадения, ренерсивный счетчик 6, блоки 7-9 управления ячейками, силовые преобразовательные ячейки 10-12, а также источник 13 постоянного тока. 35

Блок 1 формирования программных сигналов имеет выход кода программной синусоиды, выход тактовых импульсов, выход нулевого сигнала, выход управления полярностью, аналого-цифровой преобразователь 2 входом подключен к выходу преобразонателя, блок 3 сравнения кодов первым кодовым входом подключен к выходу аналого-цифрового преобразователя 2, 45 вторым кодовым входом подключен к выходу кода программной синусоиды блока 1, выходом приоритета числа на перврм входе подключен к первому вхотду первой схемы 4 совпадения, выход кото-5О рой подключен к нычитающему входу реверсивного счетчика 6,выходом приоритета числа на втором входе — к первому входу второй схемы 5 совпадения, выход котоРой и, лклю ен к суммирующему входу реверсивного счетчика 6, блоки 7-9

JJHpQBJlL ния ячейками первыми входами (P) подl . (Рч нь! к BblxoJIv р яраBJIb ния полярн гl к б:iокB 1 BTophlMII l- õ,i;Iÿìè (К) подключены к соотнетстнующим разрядам кодового выхода ренерсивного счетчика 6, а ныходами, число которых равно числу ключей н силовых ячейках 10-12, подключены к управляющим входам соответствующих ключей силовых ячеек 10-12, выход тактовых импульсов блока 1 подключен к вторым входам схем 4 и 5 совпадения, выход нулевого сигнала блока 1 подключен к обнуляющему входу (К) реверсивного счетчика 6, силовые ячейки 10-12 силовыми входами подсоединяются к источнику 13 постоянного тока, а их силовые выходы соединены последовательно и образуют ньгход преобразователя в целом.

Преобразователь работает следующим образом.

На выходе кода программной синусоиды блока 1 (фиг. 1) формируется код х, значение которого в каждый момент времени пропорционально мгновенному значению программной ступенчатоаппроксимированной синусоиды, Код х непрерывно поступает на второй вход блока 3 сравнения кодов на первый нход которого непрерывно поступает с выхода АЦП 2 код у, значение которого в каждый момент времени пропорционально мгновенному значению напряжения на выходе преобразователя.

Коды х и у непрерывно сравнивают в блоке 3 сравнения кодов. Если х ) у, т.е ° напряжение на выходе преобразователя меньше программного значения, то с выхода приоритета числа на втором входе блока 3 сравнения кодов разрешающий сигнал (х ) у, на фиг. 1) поступает на первый вход второй схемы 5 совпадения, при этом тактовые импульсы с выхода тактовых импульсов блока 1 начинают поступать на суммирующий вход реверсивного счетчика 6.

В реверсивном счетчике 6 начинается суммирование тактовых импульсов, значение кода на выходе реверсивного счетчика 6 возрастает, в блоках

7-9 управлениях ячейками формируются цепи включения и выключения соответствующих ключей силовых ячеек

10-12, напряжение на выходе преобразователя возрастает пропорционально возрастающему коду на выходе реверсивного счетчика 6 до тех пор, пока не достигнет программного значения, т.е. пока не стан т х=-у.

Если н какой-то и м .нт времени напряжение на н.....:;. преобразователя

1415380 синусоиде. Разряд (М+1)-и выходного кода ПЗУ 17 образует выход управления полярностью. В этом разряде записан код управления полярностью выходного напряжения — силовых ячеек, Выход переполнения (+Р) счетчика (6 образует выход нулевого сигнала.

Объем счетчика 16 S = 2, где N —K число разрядов выходного кода счетчика 16, должен быть равен или не превышать число адресов ПЗУ 17.

В таблице приведены номера адресов ПЗУ 17 и значения записанных в эти адреса значений кодов при условии, что в качестве ПЗУ 17 выбрано

ПЗУ объемом 256"4, что удовлетворяет рассматриваемой схеме с тремя силовыми ячейками (M = 3).

Номера адресов

ПЗУ (вход

ПЗУ) 0 0 1

0 0 1

1 0 1

0-2

3-8

9-14

15-20

0 1

0 1 1

0 1

1 1 1

0 больше программного значения, т.е. у ) х, тогда разрешающий сигнал с выхода приориета числа на первом входе блока 3 сравнения кодов поступает на первый вход первой схемы 4 совпадения, при этом тактовые импульсы с выхода блока 1 начинают поступать на вычитающий вход реверсивного счетчика 6, происходит уменьшение кода на выходе реверсивного счетчика 6 и пропорционально ему напряжения на выходе преобразователя до тех пор, пока не будет х=у.

Таким образом, выходное напряжение постоянно догоняет программное значение. При этом выполняются задачи формирования требуемой формы выходного напряжения и стабилизации его величины (действующего значения).

Для устранения каких-либо непредвиденных процессов в работе по окончании каждого периода программной синусоиды с выхода нулевого сигнала блока 1 сигнал нулевого значения про- 26 граммной синусоиды поступает на обнуляющий вход (R) реверсивного счетчика

6 и переводит его в состояние 0-0.

На фиг. 2 приведена функциональная схема блока 1 формирования программных сигналов, В состав блока 1 формирования программных сигналов входят: задающий генератор 14, выход которого является выходом тактовых импульсов и через делитель 15 частоты подключен к счетному входу счетчика 16, кодо35 вый выход которого подключен к адресному входу программируемого запоминающего устройства 17 (ПЗУ), причем

ПЗУ 17 имеет не менее M+1 разрядов

40 выходного кода, где M — число силовых ячеек преобразователя и число разрядов управляющего кода на выходе реверсивного счетчика 6.

Блок 1 работает следующим образом.

В исходном состоянии счетчик 16

45 обнулен. С выхода задающего генератора 14 тактовые импульсы с частотой поступают на выход тактовых импульсов блока 1 и на вход делителя

15 частоты, с выхода которого тактовые импульсы с частотой Г = Г /kg, где kg — коэффициент деления, поступают на счетный вход счетчика 16.

Первые M разрядов выходного кода

ПЗУ 17 образуют выход кода программной синусоиды. В этих разрядах записывается код, соответствующий программной ступенчато-аппроксимируемой

21-27

28-36

37-48

49-78

79-90

91-99

100-106

106-112

113-118

119-124

125-127

128-130

131 — 136

Значение разрядов кода (выход ПЗУ) Х1 Х2 ХЗ лярность) 1 1

1 1

1 1

1 4

0 1

0 1

0 1

0 1

0 0

0 0

Номера адресов

ПЗУ (вход пзу) "1

Х7 (полярность) Х1

1 О О

1 О О

О 1 О

1 О

1 О

1 О О

1 1 О

О 1 О

1 О

О О

О О

О О

О О

О

При этом счетчик 16 имеет объем

S = 2 = 256, т.е. N = 8.

Вариант блока управления ячейкой (фиг. 3) приведен для случая, когда силовая ячейка выполнена по схеме однофазного мостового инвертора на транзисторах с обратными диодами и трансформаторным выходом. Блок состоит иэ двух двухвходовых элементов И 1819, овского элемента ИЛИ 20 и одного элемента НЕ 1, имеет два входа К и P и четыре выхода, на которых реализуются логические функции: F1 = k.р; F g = k.р, 3

Вариант блока управления ячейкой (фиг. 4) приведен для случая, когда силовая ячейка выполнена по схеме с шунтированием первичной обмотки трансформатора. Блок имеет цва входа

К и P и три выхода, на которых реалиеуютсл логические функции F, = k Р;

F = k p; Fz = (k p)(k p) = k.

Приведенный пример блока состоит из элемента HE 22, двух двухвхоловых

137-142

143-148

149-155

156-164

165-176

177-206

207-218

219-227

228-234

235-240

241-246

247-252

253-255

Продолжени таблицы!

Значение разрядов кода (выход ПЗУ) 15380

6 элементов И 23-24, двухвходового элемента И-НЕ 25.

Силовая ячейка (фиг. 5), вь,полне на по мостовой схеме и включает выходной трансформатор 26, обратные диоды 27-30, транзисторные ключи

31-34.

Функции управления транзисторными ключами: для транзисторного ключа

31 F „ = k р, для транзисторного ключа 32 F = К Р, для транзисторного ключа 33 F< = р, для транзисторногп ключа 34 F3 = р.

Силовая ячейка с устройством шунтирования первичной обмотки трансформатора (фиг. 6) включает выходной трансформатор 35 со средней точкой в первичной обмотке, два транзисторных ключа 36-37, формирующих выходное напряжение, транзисторный ключ 38 диоды 39-42, образующие элемент 43 шунтирования первичной обмотки трансформатора. Функции управления ключами: транзисторного ключа 36 F> = ki p, транзисторного ключа 37 F < = k p, транзисторного ключа 38 элемента 43 шунтирования первичной обмотки трансформатора Г =

Силовая часть преобразователя (фиг. 7) состоит из трех силовых ячеек, включенных параллельно по входу (по цепи питания) и последовательно— по выходной цепи. В состав силовой части преобразования входят силовые ключи 44-55, причем ключи 44-47 вхо" дят в первую силовую ячейку, ключи

48-51 — во вторую, ключи 52-55 — в третью, выходные трансформаторы 5658, причем трансформатор 56 входит в первую ячейку, трансформатор 57— во вторую, трансформатор 58 — в третью; обратные диоды 59-70, причем диоды 59-62 входят в первую ячейку, диоды 63-66 — во вторую, диоды 6770 — в третью.

На фиг. 8 изображена таблица переключений ключей 44-55, а на фиг. 9— временные диаграммы, поясняющие работу преобразователя (фиг. 7) и принцип формирования внглодного напряжения.

Технико-экономическая эффективность предлагаемого изобретения заключается в повышении надежности выполнения преобразователем его главной функции — обеспечения потребителей электрической энергией переменного тока требуемог» нида и качества.

Предлагаемое изобретение позволя- с ет повысить надежность работы преоб- с разователя, надежность обеспечения P электроэнергией переменного тока за- с данного качества потребителей, под- 5 р ключенных к выходу преобразователя. ч

А требование бесперебойности электро- к снабжения является одним из основных ж требований в электроприводе в систе- с

10 мах автономного электроснабжения от- в ветственных потребителей. Ф

Формула изобретения

Преобразователь постоянного напряжения в мгогоступенчатое квазисинусоидальное, содержащий ш параллельно соединенных силовых трансформаторных ячеек, каждая из которых представляет собой однофазный инвертор с трансформаторным выходом, реверсивный счетчик в качестве формирователя управляющего кода, о т л и— ч а ю шийся тем, что, с целью повьппения надежности работы, введены блок формирования программных сигналов, имеющий выход кода программного синусоидального напряжения, выход тактовых импульсов, выход сигнала, соответствующего концу полупериода синусоидального напряжения, выход сигнала управления полярносгью, аналого-цифровой преобразователь, входом подключенный к выходу преобразователя, блок сравнения кодов, первым входом подключенный к выходу аналогоцифрового преобразователя, вторым входом — к выходу кода программного синусоидального напряжения блока формирования программных сигналов, выход приоритета числа на первом входе блока сравнения кодов подключен к первому входу первого блока совпадения, выход которого подключен к вычитающему входу реверсивного счетчика, выход приоритета числа на втором входе блока сравнения кодов подключен к первому входу второго блока совпадения, выход которого подключен к суммирующему входу реверсивного счетчика, вторые входы блоков совпадения соединены с выходом тактовых импульсов блока формирования программных сигналов, m блоков управления силовыми трансформаторными ячейками, первые входы которых подключены к выходу сигнала управления полярностью блока формирования программных сигналов, вторые входы — к оответствующим кодовым выходам реверивного счетчика, выходы, число котоых равно числу ключей в силовой транформаторной ячейке, подключены к упавляющим входам соответствующих клюей, выход сигнала, соответствующего онцу периода синусоидального напряения блока формирования программных игналов, подключен к обнуляющему ходу реверсивного счетчика, блок ормирования программных сигналов выполнен в виде задающего генератора, выход которого является выходом актовых импульсов блока и через делитель

15 частоты подключен к счетному входу счетчика блока формирования программных сигналов, кодовый выход которого подключен к адресному входу программируемого запоминающего устрой20 ства, имеющего не менее ш+1 разрядов выходного кода, причем в ш разрядах, образующих выход кода программного синусоидального напряжения блока формирования программных сигналов, 25 записаны значения программного кода, соответствующего мгновенным значениям ступенчато-аппроксимированного синусоидального напряжения, а в (m+1)-м разряде, образующем выход блока формирования программных сигналов, записан сигнал управления полярностью выходного напряжения силовых трансформаторных ячеек, выход пе-. реполнения счетчика блока формирова35 ния программных сигналов образует выход сигнала, соответствующего концу периода синусоидального напряжения блока формирования программных сигналов, для силовых трансформатор40 ных ячеек, выполненных с шунтированием первичных обмоток или в виде однофазного мостового инвертора на полностью управляемых ключах с обратными диодами, блоки управления име45 ют два входа и три выхода, сигналы на которых формируются в соответствии со следующими логическими функциями:

I „= k р, Г=kр, 50 F> = (k. p) (k. Ð) = k где р — сигнал на выходе сигнала управления полярностью блока формирования программных сигналов;

55 k — - сигнал на соответствующем выходе реверсивного счетчика, причем первые выходы блоков управления подключены к управляющим входам ключей, формирующих полуволну одной

1и 15380 налов; код/ п&гюаг первостью

Юуюе8ой

baOd аллюр

Vny bCbi полярности выходного напряжения, вторые — к управляющим входам ключей, формирующих полуволну другой полярности, третьи — к управляющим входам блоков шунтирования первичных обмоток трансформаторов, или два входа и четыре выхода, сигналы на которых формируются в соответствии со следующими логическими функциями, 10

F,=kp;

F -=kp;

Р = р;

Fg = р, где p — сигнал на выходе сигнала управления полярностью блока формирования программных сигсигнал на соответствующем выходе реверсивного счетчика, I причем первый и второй выходы каждого блока управления соединены с управляющими входами ключей анодной группы, а третий и четвертый выходы — с управляющими входами ключей катодной группы.

Юых.

Раг. 7

Цп

1 z f s f f 1 в f 10 и rzisíа1вrr1в ifzuzrzzzszizsznzrznzfsn ада а i111 1110000 адддаааод Рада ад даддогаддааоuuuuuuurllrrlrnunu дддд Рдддддда 000111111111111111

1r r1111I r r l11r l u nnnnn0unu0unnn

00110011100110аддаодаадаааддад

unnuunuuunnnnnunurrnu1rlndlrun

000 00 00 Р 0 д 000 д à1 111 11111111 111

rir r r r I rill r I I I I 00000000uuun000 а 1 п 10101 D 1 0 1 0 10 0 n D à 00 д à 00 00 п да дддд dnuuu nаддддд 10 101010101010

fS

Рдадаnддunuд 00011 r 1 r 1111111111

r r1l r i r r r r l 11r 1ааааааааааааааа

1415380 и,(ra

u»„

Составитель А.Меркулова

Техред А.Кравчук

Корректор Г.Решетник

Редактор С.Патрушева

Заказ 3882/53

Ilp(и- в .IcTBE нн< — и< пигрпфич гк, е предприятие, г. Ужгород, уп. 11роектная, 4

lg ФФ

Ig ФХ

Ь

lg 47 Ф a+ (ФО с,а с sz

i g П

Тираж 665 Поппнсное

ВПИИ11И Госупарственного комитета СССР п< делам изобретений и открытий!

13035, Москп;., Hi-35, Раушская наб., д. 4/