Фазовый детектор

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и обеспечивает расширение динамического диапазона фазового детектирования. Фазовьш детектор содержит усилитель-ограничитель 1, двухполупериодный преобразователь фзза-код 2, ЦАП 5, дифференцирующий блок 7, диоды 8, 9, инвертор 10, триггер . 1I, электронный ключ (ЭК) 12 и сумматор 14. Двухполупериодный преобразователь фаза-код 2, на который по пгине 3 подается опорное напряжение , а по шине 4 - счетные импульсы, осуществляет преобразование фазовых сдвигов поступающего фазомодулированного сигнала в цифровой код. Этот код преобразуется в аналоговый сигнал , амплитуда которого определяется значением зталонного напряжения, поступающего по тине 6. Дифференцирующий блок 7 дифференцирует фазовые переходы сигнала через ноль. Напряжение с триггера 11 управляет работой ЭК 12. При сигнале 1 триггера 11 через ЭК 12 на сумматор 14 подается отриц. эталонное напряжение, поступающее по шине 13. Сумматор 14 формирует демодулированный сигнал. 4 ил. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5D 4 Н 03 D 3/20

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, К А8ТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4094727/24-09 (22) 24.07.86 (46) 07.08.88. Вюл. У 29 (72) .Н.A. Марцинковский, В.А. Пономарев и С.В. Сурков (53) 621.376.55(088.8) (56) Авторское свидетельство СССР

В 1171970, кл. Н 03 D ТЗ/00, 29.06.83. (54) ФАЗОВЫИ ДЕТЕКТОР (57) Изобретение относится к радиотехнике и обеспечивает расширение динамического диапазона фазового детектирования. Фазовый детектор содержит усилитель-ограничитель 1, двухполупериодный преобразователь фаза-код 2, ЦАП 5, дифференцирующий блок 7, диоды 8, 9, инвертор !О, триггер,ll, электронный ключ (ЭК) 12

„„Я0„„1415415 д 1.и сумматор 14. Двухполупериодный преобразователь фаза-код 2, на который по шине 3 подается опорное напряжение, а по шине 4 — счетные импульсы, осуществляет преобразование фазовых сдвигов поступающего фазомодулированного сигнала в цифровой код. Этот код преобразуется в аналоговый сигнал, амплитуда которого определяется значением эталонного напряжения, поступающего по шине 6. Дифференцирующий блок 7 дифференцирует фазовые переходы сигнала через ноль. Напряжение с триггера 11 управляет работой ЭК 12. При сигнале "1" триггера

11 через ЭК 12 на сумматор 14 подает- с

К> ся отриц. эталонное напряжение, поступающее по шине 13. Сумматор 14 формирует демодулированный сигнал.

4 ил.

14154! 3

Изобретение относится к рлди мерительной технике, в частности к устройствам демодуляции флзомодулировлнных сигнллов, девилция фазы ко5 торых не превьиялет «+2 и, л спектр закона флзовой модуляции узкополосный.

Цель изобретения — расширение динамического дилплзонл фазового детектировлиия. 10

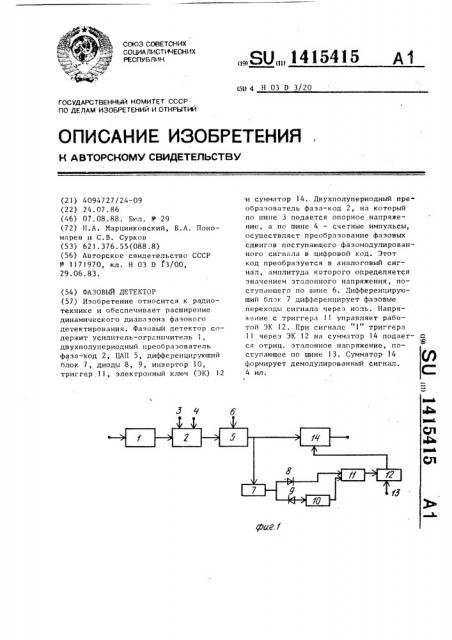

На фиг. 1 приведена структурная электрическая схема флзового детектора; нл фиг. 2 — фазовая характеристика преобразователя фаза-код; на фиг. 3 флзовля характеристика фаэо вого детектора ; на фиг. 4 — временные диаграммы фазового детектора.

Фазовый детектор содержит усилитель-ограничитель 1, двухполупериодный преобразователь 2 фаза-код, шийу

3 опорного напряжения, шину 4 счетных импульсов, цифроаналоговый преобразователь 5, шину 6 эталонного напряжения, дифференцирующий блок 7, первый 8 и второй 9 диоды, инвертор 25

10, триггер 11, электронный ключ 12, шину 13 отрицательного -этллонногс напряжения, сумматор 14.

Фазовый детектор рлблтлет следующим Образом. 30

Флзомодулировлнный сигнал, имеющий флзовую модуляцию с синусоидальной огиблющей, поступает нл вход усилителя-огрлничителя l. Прямоугольный сигнал с выхода усилителя-ограничителя 1 поступает нл вход двухполупериодного преобразователя 2 флзл-код.

На второй вход с шины 3 поступает

-горное ллпряжение. Цл третий вход пвухполупериодного преобразователя- 2 40 с шины 4 поступают счетные импульсы.

Двухполупериодный преобразователь 2 фазл-код осушествляет преобразование фазовых сдвигов Ф11-сигнала в цифроВой код (фиг. 2) при этом частота 45 счетных импульсов, поступающих с шины 4, определяет дискрет измерения фазы сигнала. Цифровой сигнал с выхода двухполупериодного преобразователя 2 фаза-код поступает на вход

50 цифролнллогового преобразователя 5, где он пре ->бразуется в аналоговый сигнал. Величина эталонного напряжения, поступлющего нл другой вход преобразолл ля 5 по шине 6, определяет амплитуду выходного напряжения пре55 образовлтеля 5.

Дифференцирующий блок 7 осуществляет дифференцирование (фиг. 4б) фа . пых переходов ФМ-с.и нала «e;. ; нуль (фиг. 4л) .

Положительный импульс проходит через диод 8, поступает на вход установки в единицу триггера 11, отрицательный импульс проходит через диод

9, инвертор IO, поступает на другой вход триггера ll и устанавливает его в нулевое состояние. Импульс с выхода триггера ll (фиг. 4в) поступает на управляющий вход электронного ключа

12. В интервале времени действия управляющего импульса триггера II на выходе электронного ключа 12 формируется импульс (фиг. 4г), амплитуда которого определяется значением напряжения, поступающего с шины 13 на вход электронного ключа 12.

Сигналы с выходов электронного ключа 12 и преобразователя 5 поступают нл входы сумматора 14, на выходе которого формируется демодулированный сигнал (фиг. 4д).

Ф о р м у л а и з о б р е т е н и я

Фазовый детектор, содержащий последовательно соединенные цифроаналоговый преобразователь и сумматор, выход которого является выходом фазового детектора, а также последовательно соединенные триггер и электронный ключ, выход которого соединен с другим входом сумматора, и дифференцирующий блок, о т л и ч а ю шийся тем, что, с целью расширения динамического диапазона фазового детектирования, в него введены усилитель-ограничитель, вход которого является входом фазового детектора, двухполупериодный преобразователь фаза-код, первый и второй диоды и инвертор, причем усилитель-ограничитель через двухполупериодный преобразователь фаза-код соединен с входом цифроаналогового преобразователя, другой вход которого является входом эталонного напряжения фазового детектора, а выход соединен с входом дифференцирующего блока, выход которого соединен с анодом первого и катодом второго диодов, катод первого диода соединен с входом установки в единицу триггера, а анод второго диода через инвертор соединен с входом сброса в ноль триггера, второй и третий входы двухполупериодного преобразователя фаза-код являются входом

14154!5 опорного напряжения и входом, счетных импульсов фазового детектора соответственно, а другой вход электронного ключа является входом отрицательногс эталонного напряжения фазового детектора.!

4l 54! 5

Составитель A. Колосов

Редактор Н, Бобкова Техред Л.Олийнык

Корректор 0 ° Кравцова

Заказ 3886/55

Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

ll3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4