Устройство циклового фазирования аппаратуры передачи двоичных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к технике передачи дискретной информации. Цель изобретения - расширение функциональных возможностей путем обеспечения циклового фазирования при неравномерно распределенной синхрокомбинации . Устр-во содержит блок стробирования 1, блок сравнения 2,решающий блок 5, блок памяти 6, В устр-во введены ключ 3, триггер 4, счетчики 7,9 и дополнительный блок сравнения 8.Во время работы происходит сравнение поступающих с входа двоичных сигналов с элементами синкрокомбинации через расстояния, считьгааемые из блока памяти 6. При этом счетчик 7 определяет номер искомого синхробита, а счетчик 9 отсчитывает расстояние межцу каждььми двумя соседними элементами синхронизации. Схема сравнения дает сигнал о равенстве показаний счетчика 9 и двоичного числа, считанного из блока памяти для данного синхробита. 1 ил. с «

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„Я0„„141 449 А1 (51)4 Н 04 L 7/08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4149423/24-08 (22) 20.11.86 (46) 07 .08.88. Бюл. У 29 (72) В.Н.Данилов, Д.В.Паниткин, В.Ц.Жапов и А.Н.Петрунин (53) 621. 394. 14 (088. 8) (56) Авторское свидетельство СССР

9 965006 кл. Н 04 1. 7/08, 1982. (54) УСТРОЙСТВО ЦИКЛОВОГО ФАЗИРОВАНИЯ АППАРАТУРЫ ПЕРЕДАЧИ ДВОИЧНЫХ СИГНАЛОВ (57) Изобретение относится к технике передачи дискретной информации. Цель изобретения — расширение функциональных возможностей путем обеспечения циклового фазирования при неравномерно распределенной синхрокомбинации устр-во содержит блок стробпрования 1, блок сравнения 2,решающий блок 5, блок памяти 6, В устр-во введены ключ 3, триггер 4, счетчики

7, 9 и дополнительный блок сравнения

8. Во время работы происходит сравнение поступающих с входа двоичных сигналов с элементами синхрокомбинации через расстояния, считываемые из блока памяти 6. При этом счетчик 7 определяет номер искомого синхробита, а счетчик 9 отсчитывает расстояние ме щу каждыми двумя соседними элементами синхронизации. Схема сравнения дает сигнал о равенстве показаний счетчика 9 и двоичного числа, считан- цр с ного из блока памяти для данного синхробита. 1 ил, 1415449

H.çñ брет;- ние о. =ится к технике передачи дискретной информации, а именно к устройствам синхронизации по циклам передающей и приемной частей аппаратуры передачи двоичных сигнапов при использовании распределенной синхрокомбинации.

Цель изобретения — расширение функциональных возможностей путем обеспечения циклового фазирования при неравномерно распределенной синхрокомбинации.

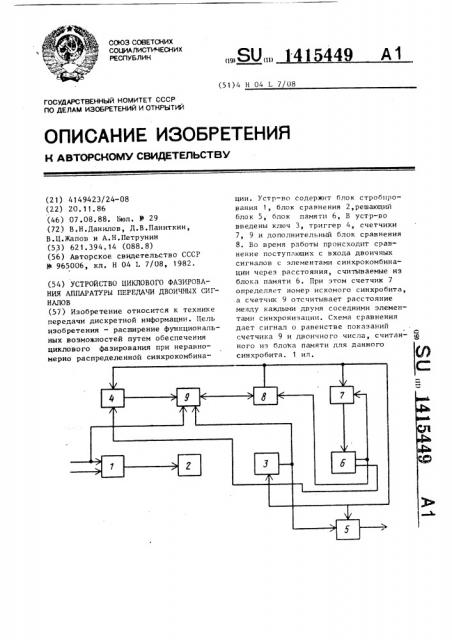

На чертеже приведена структурная электрическая схема устройства. 15

Устройство циклового фазирования содержит блок 1 стробирования, блок

2 сравнения, ключ 3, триггер 4, решающий блок 5, блок 6 памяти, первый счетчик 7, дополнительный блок 8 сравнения и второй счетчик 9.

Устройство работает следующим образом.

Перед началом работы в блок 6 памяти заносятся исходные данные, сос- 25

-,îÿùèe из двоичного кода расстояния между каждыми двумя соседними символами синхрокомбинации, признака конца цикла, после которого порядок распределения символов и сами символы синх- 30 рокомбинации повторяются, кроме того, первый и второй счетчики 7 и 9 и триггер 4 обнуляются (цепи начальной установки и занесения информации в память на схеме не показаны). Таким образом, счетный вход второго счетчика 9 закрыт, иэ блока 6 памяги на вход дополнительного блока 8 сравнения поступает первое управляющее слово, которое обозначает расстояние между первым и вторым синхробитами в двоичном коде, кроме того, закрыт ключ 3 и счетный вход первого счетчика 7.

Приходящие на вход символы строби- 45 руются в блоке 1 стробирования и поступают далее в блок 2 сравнения. На адресный вход блока 6 памяти заведен выход первого счетчика 7, показания которого обозначают номер символа

50 синхрокомбинации, подлежащего сравнению с пос гупившим символом на входе.

Считанный из оперативной памяти сиь вол эталонн< го синхрокода, через вто рой выхо,; »пока Ь памяти поступает

55 на второ » вход блока 2 сравнения. Как только синхробит совпадает с входным символом, триггер 4 по сигналу иэ блока 2 сравнения устанавлин ае тся в единичное состояние, и на счетном входе второ ro счетчика 9 появляется разрешение. Каждый последующий входной символ увеличивает показания второго счетчика 9 на единицу до тех пор, пока его показания не сравнятся с двоичным числом, поступающим иэ блока 6 памяти . Когда укаэанное сравнение произойдет, триггер 4 сбрасывается, счетный вход второго счетчика 9 закрывается, ключ 3 открывается, а показания первого счетчика 7 увеличиваются на единицу, Считанный иэ блока 6 памяти новый символ эталонного синхрокода поступает в блок 2 сравнения, в котором происходит сравнение входного символа с очередным синхробитом. Если указанные символы равны, то появившийся сигнал на выходе блока 2 сравнения, пройдя через ключ 3, обнуляет показания второго счетчика 9 и, кроме того, поступает в решающий блок 5, в котором происходит накопление совпадений входных символов с синхробитами и принятие решения о вхождении в синхрониэм с входным потоком информации.

В случае несравнения в блоке 2 сравнения входного символа с очередным синхробитом решающий блок 5 сбрасывает ранее накопленное количество совпадений и начинает подсчет с нуля, при этом ключ 3 остается открытым, а в блоке 2 сравнения происходит сравнение следующего входного символа с синхробитом, на котором произошло несравнение. После появления входного символа, равного проверяемому синхробиту, триггер 4 снова взводится, иэ блока 6 памяти считывается очередное управляющее слово, содержащее двоичное число, указывающее расстояние до очередного синхробита и сам синхробит, а описанный процесс повторяется.

Если в управляющем слове также присутствует признак конца цикла, первый счетчик 7 обнуляется, и блок 2 сравнения переходит к поиску первого символа синхрокомбинации.

Фор»чулаиэобретения

Устройство циклового фаэирования аппаратуры передачи двоичных сигналов, содержащее блок памяти, решающий блок, выход которого является выходом ус тройс тв а, и последов ательно соединенные блок стробирования, вход которого является входом устройСоставитель Н.Лебедянская

Редактор Н.Яцола Техред Л.Олийнык Корректор С.Черни

Заказ 3888/56 Тираж 660 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3 1(1 ства, и блок сравнения, о т л и ч а— ю ш е е с я тем, что, с целью расширения функциональных возможностей путем обеспечения циклового фазирования при неравномерно распределенной синхрокомбинации, введены триггер, первый счетчик, ключ и последовательно соединенные второй счетчик и дополнительный блок сравнения, второй вход которого объединен с входом сброса первого счетчика и первым выходом блока памяти, адресный вход которого соединен с выходом первого счетчика, а второй выход блока памяти соединен с вторым входом блока

5449

4 сравнения, выход которого соединен с установочными входом триггера и информационным входом ключа, выход которого соединен с входом решающего блока и входом сброса второго счетчика, тактовый вход которого соединен с тактовым входом блока стробирования и является тактовым входом устройства, счетный вход второго счетчика соединен с выходом триггера, вход сброса которого соединен с управляющим входом ключа, счетным входом первого счетчика, вторым вхоцом решакще1ч шо блока и выходом дополнительного блока сравнения.