Приемник частотно-манипулированных сигналов

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„Л0„„41545

А1 (51) 4 Н 04 1. 27/1ч

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ASTOPGHOIVIV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4047943/24-09 (22) 03.04,86 (46) 07.08.88. Бюл. У 29 (71) Ленинградский институт инженеров железнодорожного транспорта им. акад.В.Н,Образцова (72) А.Е.Красковский, А.А.Семенов и Е.И.Тетерина (53) 621.396.62(088.8) (56) Авторское свидетельство СССР

У 290473, кл. Н 04 Ь 27/10, 1969. (54) ПРИЕМНИК ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ (57) Изобретение относится к радиотехнике и позволяет повысить помехо" устойчивость. Приемник содержит смеситель 1, генератор 2, полосовой фильтр 3, АЦП 4, коммутатор 5, блоки задержки 6,7, элемент ИЛИ 8, перемно житель 9, интегратор 10, сумматор 11, пороговый блок 12 и блок 13 вьщелення опорной частоты. Входной частотноманипулированный сигнал преобразуется в преобразователе, состоящем иэ блоков 1-3, в сигнал с соотношением между частотами 1,5. Соотв. ему цифровой сигнал проходит на перемножитель 9 непосредственно, а также через один иэ блоков задержки 6,7. Напряжения, поступающие на перемножитель 9, при поступлении более высокой частоты манипуляции равны по амплитуде и про тивоположны по знаку, а при поступлении менее высокой частоты манипуля-. ции они совпадают, В результате на выходе перемножителя 9 формируется сигнал удвоенной амплитуды, но разно го знака. В интеграторе 10 сигнал перемножения интегрируется на интервале, равном периоду меньшей частоты манипуляции. Блок 13 определяет начало н конец дискретной посылки, Во время этого интервала сигнал с сумматора !i проходит на пороговый блок 12. В зависимости от знака поступающего сигнала пороговый блок l2 формирует токовую или бестоковую посылку. 1 ил .

)415454

Изобретение относится к радиотехнике.

Цель изобретения — повышение помехоустойчивости.

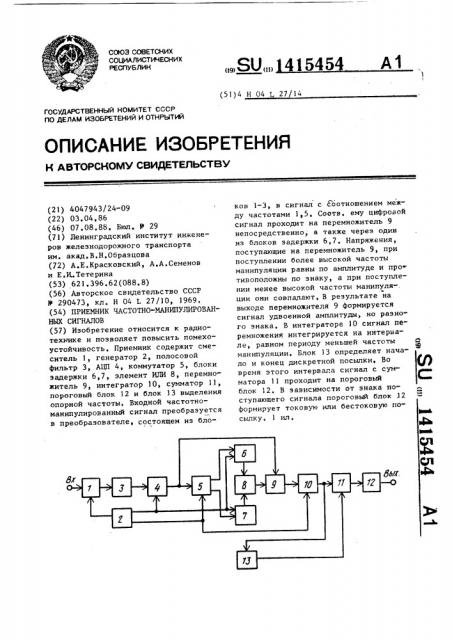

Па чертеже изображена структурная

5 электрическая схема предлагаемого приемника, Приемник содержит смеситель 1, генератор 2, полосовой фильтр 3, аналого-цифровой преобразователь (АЦП) 4, коммутатор 5, блоки 6 и 7 задержки, элемент ИЛИ 8, перемножитель 9, интегратор 10, сумматор 11, пороговый блок 12 и блок 13 выделения опорной 15 частоты, Приемник работает следующим образом.

Частотно-манипулированный сигнал поступает на вход преобразователя 20 частоты, состоящего иэ смесителя 1 генератора 2 и полосового фильтра 3, Б результате преобразования на входе

АГГГ1 4 имеется частотно-манипулированный сигнал с соотношением между час- 25 тотами 1,5. Для получения такого соотношения подбирается частота, формируемая в генераторе 2, которая подается на второй вход смесителя 1, С помощью АЦП 4 производится перевод 30 уровня входного сигнала в цифровую форму и в виде определенного двоичного кода подается во время существования импульса квантования на входы коммутатора 5 и перемножителя 9.

Во время включения устройства коммутатор 5 устанавливается в произвольное положение, допустим в такое, что сигнал с выхода АЦП 4 поступает на вход блока 6 задержки. Импульсами с 40 выхода генератора 2 дноичный код записывается в блок 6 задержки, причем производится последовательное заполнение ячеек..Одновременно этими же импульсами считывается информация с 45 блока 7 задержки, которая через элемент ИЛИ 8 подается на второй вход перемножителя 9. Через время, равное периоду наименьшей частоты манипуляции коммутатор 5 переводится в сос- .

В

50 тояние, при котором информация записывается в блок 7 задержки и считывается наоборот с блока 6, Импульсы, переводящие коммутатор 5 в другое состояние, создаются в генераторе 2, Таким образом, на входах перемножителя 9 н моменты квантования входного сигнала присутствуют два напряжепия, эти напряжения но время Ilo сту33ления более высокой частоты равны пс> амплитуде и противоположны по знаку, а но время поступления менее высокой частоты манипуляции они полностью должны совпадать. В результате на выходе перемножителя 9 ормируется сигнал удвоенной амплитуды, но знак которого положительный или отрицательный. Сигнал с выхода перемножителя 9 подается на вход интегратора 10, выполненного в виде реверсивного счетчика, в котором производится интегрирование результатов перемножения на интервале времени, равном периоду наименьшей частоты манипуляции. Г!ри этом результат интегрирования не зависит от начала интегрирования, т.е. схема полностью инвариантна к начальной фазе. Инвариантность достигается путем реализации автокорреляционного способа обработки сигнала. Поэтому эффективность использования схемы не зависит от того, имеется ли разрыв фазы в момент смены частоты манипуляции или он отсутствует.

После интегриронания сигнал поступает на вход сумматора ll и на вход блока 13 ньщеления опорной частоты.

С помощью блока 13 производится определение начала и конца дискретной посылки. Поэтому сигнал с выхода сумматора 11 12, поступает в моменты времени, кратные длительности элементарной посылки и совпадающие по фазе с началом и концом дискретного сигнала. На выходе порогового блока 12 формируется токовая или бестоковая посылка в зависимости от знака сигнала на выходе суммирующего блока.

Ф о р м у л а и з о б р е т е н и я

Приемник частотно-манипулированных сигналов, содержащий смеситель, блок выделения опорной частоты, перемножитель, первый блок задержки, генератор, первый выход которого соединен с первым входом смесителя, второй вход которого янляется входом приемника частотно-манипулированных сигналов, отличающийся тем, что, с с>еньн> повышения помехоустойчивости, внедепы последовательно соединенные 33с>лос оной фильтр, аналого-цифранс>й пресбр;33(ватель и ком1415454

Составитель Н.Лазарева

Техред A. Кравчук

Корректор М.Иаксимишинец

Редактор Н.Яцола

Тираж 660 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 3889/57

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, ектная 4 мутатор, второй блок задержки, элемент ИЛИ, последовательно соединенные интегратор, сумматор и пороговый блок, причем выход смесителя соединен с входом полосового фильтра, второй выход генератора соединен с вторым входом аналого-цифрового преобраэоват ля и первыми входами блоков задержки, вторые входы которых соединены с соответствующими выходами коммутатора, выходы блоков задержки соединены с входами элемента ИЛИ, выход которого соединен с первым входом перемножителя, второй вход которого соединен с выходом аналого-цифрового

5 преобразователя а выход — с первым

t входом интегратора, третий выход генератора соединен с вторыми входами коммутатора и интегратора, выход которого через блок выделения опорной частоты соединен с вторым входом сумматора, выход порогового блока является выходом приемника частотно-манипулированных сигналов.