Устройство измерения времени задержки включения компараторов напряжения

Иллюстрации

Показать всеРеферат

Изобретение относится к области электронной техники. Устройство измерения времени задержки включения комиараторов напряжения содержит опорные резисторы 26, 27, переключатель 11, источник 13 опорного напряжения, блок 1 управления, задающий генератор 2, формирователи 3, 4 тестовых сигналов, блок 9 балансировки, RS-триггер 14, пороговый блок 12, блок 10 привязки уровня и измеритель 15 временных интервалов , содержаш.ий логические вентили 29, 30, тактовый генератор 31, реверсивный счетчик 32 и индикатор 33. Устройство имеет повышенную точность измерения времени задержки включения (выключения) за счет устранения влияния задержек. 1 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU, 141 923 А 1 Ю 4 G 01 3128

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

gfp($ F g»

ОПИСАНИЕ ИЗОБРЕТЕНИЯ . 1:, К А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 41 15725/24-21 (22) 08.09.86 (46) 15.08.88. Бюл. ¹ 30 (72) Ю. В. Троицкий, К. Н. Строев, Е. Т. Петренко, Ю. В. Додока и А. К. Линга (53) 621.317.799 (088.8) (56) Электронная техника. Сер. 8, вып. 1 (79), 1980, с. 63 — 68.

Авторское свидетельство СССР № 555374, кл. G 04 F 10)00, 1976. (54) УСТРОИСТВО ИЗМЕРЕНИЯ ВРЕМЕНИ ЗАДЕРЖКИ ВКЛЮЧЕНИЯ КОМПАРАТОРОВ НАПРЯЖЕНИЯ (57) Изобретение относится к области электронной техники. Устройство измерения времени задержки включения компараторов напряжения содержит опорные резисторы 26, 27, переключатель 11, источник 13 опорного напряжения, блок 1 управления, задающий генератор 2, формирователи 3, 4 тестовых сигналов, блок 9 балансировки, RS-триггер

14, пороговый блок 12, блок 10 привязки уровня и измеритель 15 временных интервалов, содержащий логические вентили 29, 30, тактовый генератор 31, реверсивный счетчик 32 и индикатор 33. Устройство имеет повышенную точность измерения времени задержки включения (выключеHèÿ) за счет устранения влияния задержек. 1 з.п. ф-лы, 3 ил.

1416923

Устройство относится к электронной технике и может использоваться для измерения и контроля динамических параметров компараторов (времени задержки включения и выключения) .

Целью изобретения является повышение точности измерения времени задержки включения (выключения) за счет устранения влияния задержек, вносимых формирователями и пороговым устройством, и привязки начала отсчета временного интервала к началу формирования восстанавливающего сигнала.

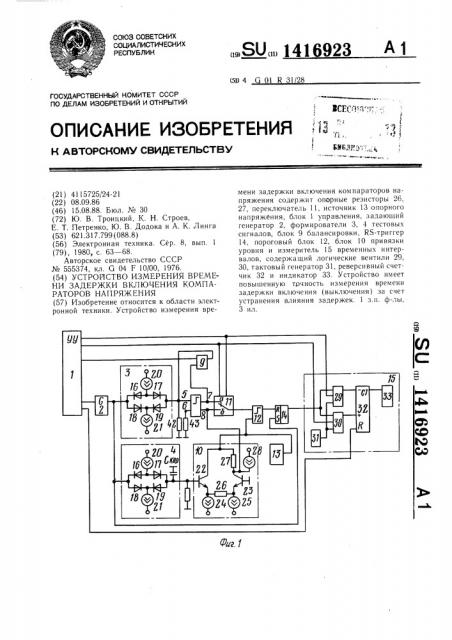

На фиг. 1 показана структурная схема устройства измерения времени задержки включения компараторов напряжения; на фиг. 2 — временные диаграммы, поясняющие работу устройства; на фиг. 3 — структурная схема устройства управления.

Устройство измерения времени задержки включения компараторов напряжения состоит из блока 1 управления, задающего генератора 2, формирователей 3, 4 тестовых сигналов, входных клемм 5, 6 и выходных клемм 7, 8 для подключения исследуемого компаратора, блока 9 балансировки, блока !

О привязки уровня, переключателя 11, порогового блока 12, источника 13 опорного напряжения, RS-триггера 14, измерителя

15 временных интервалов.

Первый выход блока 1 управления соединен с входом задающего генератора 2, выход которого соединен с входами формирователей 3, 4 тестовых сигналов и S входом

RS-триггера !4, выход которого соединен с первым входом измерителя 15 временных интервалов, а R-вход соединен с выходом порогового блока 12, первый вход которого соединен с выходом источника 13 опорного напряжения и выходом блока 10 привязки уров ня, а второй вход с выходом переключателя ! 1, первый вход которого соединен с выходной клеммой 7 для подключения исследуемого компаратора и первым входом блока 9 балансировки, а второй вход переключателя !1 соединен с второй выходной клеммой

8 и первым входом блока 10 привязки уровня, первый вход которого соединен с выходом формирователя 4 тестовых сигналов. выход формирователя 3 тестовых сигналов соединен с входной клеммой 5 для подключения исследуемого компаратора, с выходом блока 9 балансировки, третий выход блока

1 управления соединен с вторым входом блока 9 балансировки, четвертый выход соединен с третьим входом измерителя 15 временных интервалов и третьим входом блока балансировки, а четвертый выход блока 1 управления — с четвертым входом измерителя 15 временных интервалов и четвертым входом переключателя 11.

Формирователи 3, 4 тестовых сигналов состоят из диодов 16 — 19, включенных по мостовой схеме, и двух 20, 21 источников то5

10 !

55 ка, подключенных к общим точкам диодов.

Блок !О привязки уровня состоит из транзисторов 22, 23, в эмиттерные цепи которых включены два источника 24, 25 тока, а между эмиттерами — первый резистор 26, в коллекторную цепь первого транзистора включен второй резистор 27 и подключен третий источник 28 тока.

Вычитающий измеритель 15 временных интервалов состоит из двух логических вентилей 29, 30, к одному из входов каждого вентиля подключен выход тактового генератора 31, к вторым — выход RS-триггера

14, а к третьим — выходы блока 1 управления; выход вентиля 30 подключен к суммирующему входу реверсивного счетчика 32, к вычитающему входу которого подключен выход вентиля 29, а выход счетчика подключен к индикатору 33.

Блок 1 управления (фиг. 3) состоит из тактового генератора 34, соединенного через вентиль 35 с синхровходом последовательно-параллельного регистра 36, на входы параллельной записи которого подан код начальной уставки, а вход управления режимом работы соединен с выходом старшего разряда, нулевой, первый и второй разряды соединены с выходами блока 1 управления и с входами формирователей 37, 38, выходы которых объединены через схему

ИЛИ 39, выход которой через схему задержки 40 соединен с выходом блока, выход RSтриггера 41 соединен с вторым входом вентиля 35, на его 5-вход подан сигнал «Г1уск», а R-вход соединен с третьим разрядом регистра 36. Устройство содержит также опорные резисторы 42, 43.

Устройство работает следующим образом.

Вначале с помощью блока 9 автоматической балансировки, запускаемого сигналом с выхода блока управления, балансируется исследуемый компаратор. При этом на его выходе устанавливается напряжение, равное

Uoa Затем в момент (, сигналом Uq блока ! управления переключатель 11 переводится в положение би открывается вентиль 29 из. мерителя 15 временных интервалов. С задержкой C относительно фронта сигнала U„ формируется на выходе блока 1 управления импульс запуска задающего генератора Ug.

Импульс задающего генератора 2 запускает формирователь тестовых сигналов 3 и одновременно аналогичный дополнительный формирователь 4, с выхода которого снимается восстанавливающий сигнал U,< . Формирователи имеют одинаковые задержки срабатывания t> = tz,,. Фронтом сигнала

U генератора 2 триггер 14 переводится в единичное состояние. Блок 10 привязки уровня сдвигает уровень сигнала формирователя 4 Ь на вели«U что обеспечивает срабатывание порогового блока 12 при тех же условиях, которые даны в качестве от14!б923

Формула изобретения счетных для исследуемого компаратора. Пороговый блок 12 переходит в единичное состояние с некоторой задержкой t . относительно момента равенства Uz = U„. Сигналом U сбрасывается в исходное состояние триггер 14. Таким образом, длительность импульса U

Длительность импульса 1 преобразуется с помощью счетчика 32 измерителя 15 временных интервалов в дополнительный код за счет заполнения его через вентиль 29 импульсами тактового генератора 31 по вычитаюшему входу. После этого в момент сигналом U с выхода блока управления переключатель l l переводится в положение а и открывается вентиль 30 измерителя 15.

Вновь запускается задаюший генератор 2, на выходе формирователя 3 формируется тестовый сигнал U (U,, — заданное значение перегрузки; 1т ; — значение восстанавливающего сигнала). По фронту сигнала 1)„перебрасывается в единичное состояние триггер 14. Через переключатель 11 на вход порогового блока 12 подается выходное напряжение исследуемого компаратора UII.

При достижении равенства U = U,„с задержкой 1, срабатывает пороговый блок

12 и сбрасывается в исходное состояние триггер 14. При этом длительность импульса

U„, сформированного триггером 14, равна сумме задержки времени включения исследуемого компаратора и задержек срабатывания формирователя и порогового блока t

= t „„+t . Полученная длительность ймпульса преобразуется измерителем в код за счет подсчета числа импульсов тактового генератора 31, поступающих через вентиль

30 на суммирующий вход счетчика 32. В результате в счетчик будет записан код, пропорциональный значению — t> + t +(и,=

= t „„. Таким образом устраняется влияние погрешности t>,, определяемой задержками формирователя напряжения и порогового блока.

Схема привязки уровня выполнена по схеме параллельно-балансного каскада на транзисторах 22, 23. В начальный момент сигналом U = UI, заперт транзистор 22.

Транзистор 23 открыт, и с его коллектора снимается низкий уровень напряжения. При формировании сигнала перегрузки в момент перехода сигнала через нулевой уровень начинает открываться транзистор 23 и запираться транзистор 22. 3а счет тока источника

28 растет напряжение на коллекторе. При равенства 11 = Upp срабатывает пороговый блок 12. Использование в качестве транзисторов 22, 23 СВЧ транзисторов с граничной частотой 3 ГГц обеспечивает значение задержки, вносимой блоком 10 привязки уровня, »е более 0,3 — 0,4 нс.

Блок 1 управления формирует последовательность управляюши| импульсов; сигнал управления блоком балансировки; сигнал управления переключателем и вентилем измерителя 15 временных интервалов LI,, сш.— нал управления переключателем и вентилем устройства измерения Ug, сигнал запуска задающего генератора U,; сигнал сброса из мерителя временных интервалов U,q

1. Устройство изMåpåнпя времени задержки включения компараторов напряжения, содержащее первый и второй опорные резисторы, первую и вторую в|одные и первую выходную клеммы для подключения исследуемого компаратора, переключатель, IIcточник опорного напряжения, блок управления, первый выход которого соединен с входом задающего генератора, выход которого соединен с в.|одом первого формирователя тестовых сигналов, вы|од которого через первый опорный резистор соединен с обшей шиной, блок балансировки, первый в|од которого соединен с первой выходной клеммой для подключения исследуемого компаратора, второй вход — с вторым выходом блока управления, а выход — с первой входной клеммой для подключения исследуемого компаратора, RS-триггер, S-вход которого соединен с выходом задаюшего генератора, Rвход — с выходом порогового блока, а выход — с I .åðâüì входом измерителя временны| интервалов, отличаюи1ееся тем, что, с целью повышения точности измерения, в него введены второй формирователь тестовы| сигналов, блок привязки уровня, вторая вы ходна я клемма для подключения исследуемого компаратора, выход задавшего генератора соединен с входом второго формирователя тестовых сигналов, выход которого соединен с первым входом блока привязки уровня, второй вход которого соединен с второй выходной клеммой для подключения исследуемого компаратора и первым входом переключателя, а вы|од — с вторым в|одом порогового блока и выходом источника опорного напряжения, второй вход переключателя соединен с первой выходной клеммой для подключения исследуемого компаратора, третий выход блока управления соединен с третьим входом переключателя и вторым входом измерителя временны| интервалов, четвертый выход блока управления соединен с четвертым в|одом переключателя и третьим входом измерителя временны| интервалов, а пятый выход — с четвертым в|одом измерителя временных интервалов.

2. Устройство по и. 1, отличаюыееся тем, что измеритель временных интервалов содержит первый и второй логические вентили, реверсивный счетчик, генератор и индикатор..72

Фиг 2

Составитель A. Коробков

Редактор М. Циткина Техред И. Верее Корректор О. Кравцова

Заказ 4061 43 Тираж 772 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

141692 выход генератора соединен с первыми входами первого и второго вентилей, вторые входы которых соответственно соединены с вторым и третьим входами измерителя временных интервалов, а выходы — соответст3 ь венно с первым и вторым входами реверсивного счетчика, установочный вход которого соединен с четвертым входом измерителя временных интервалов, а выход соединен с входом индикатора.