Устройство для инициативного ввода адреса

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и автоматики и может быть использовано в автоматизированных системах управления технологическими процессамио Целью изобретения является повышение быстродействия устройства за счет исключения механическ 1Х элементов из схемы. Устройство содержит генератор импульсов 1, счетчик 2, дешифратор 3, блок регистров 4, содержащие элементы И 5 и триггеры 6, мультиплексор 7, коммутатор 8, триггер 9, первый и второй элементы И 10, 14, элемент И-НЕ 12, первый и второй формирователи 11,13. В устройстве предусмотрена возможность соединения нескольких устройств для увеличения числа инициативных входов. 3 кл. (Л С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (5)) 4 G 06 F 3/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

rnP

P Юьи

PJP А

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К A ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 408484)/24-24 (22} 04.07.86 (46) 15.08.88. Бюл. )и 30 (71) Научно-производственное объединение Союзцветметавтоматика" (72) В.И.Якубович, В.Я.Балиашвили и Г.В.Федин (53} 68).327 (088.8) (56) Соботка 3,, Стары Я. Микропроцессорные системы. - М.: Энергоиэдат, 1981, с. 154.

Березенко А.И. и др. Микропроцессорные комплекты повьппенного быстродействия. - М.: Радио и связь, 1981, с. 43.

Авторское свидетельство СССР

У 1)82504, кл. 6 06 F 3/02, 1984. (54) УСТРОЙСТВО ДЛЯ ИНИЦИАТИВНОГО

ВВОДА АДРЕСА

„„SU„„1416964 А 1 (57) Изобретение относится к облас ти вычислительной техники и автоматики и может быть использовано в автоматизированных системах управления технологическими процессами.

Целью изобретения является повышение быстродействня устройства за счет исключения механических элементов из схемы, Устройство содержит гене» ратор импульсов 1, счетчик 2, дешиф» ратор 3, блок регистров 4, содержащие элементы И 5 и триггеры 6, мульти плексор 7, коммутатор 8, триггер 9, первый и второй элементы И 10 14, элемент И-НЕ 12, первый и второй формирователи 11,13. В устройстве предусмотрена возможность соединения нескольких устройств для увеличения числа инициативных входов. 3 ил.

1416964

25

Изобретение относится к вычислительной технике и автоматике и может быть использовано, например, в автоматизированных системах управления технологическими процессами.

Пель изобретения - увеличение

f быстродействия устройства.

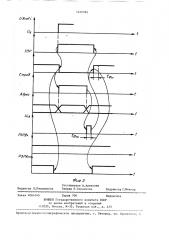

На фиг.1 изображена функциональная схема устройства; на фиг.2 пример включения нескольких устройств для увеличения числа входов; на фиг.З - диаграммы сигналов на входах и выходах устройства.

Устройство состоит иэ генератора

1 импульсов, счетчика 2, дешифратора Э, блоков 4 регистраторов, каждый из которых содержит третий элемент И 5 и второй триггер 6, мультиплексора 7, коммутатора 8, первого триггера 9, первого элемента И 10, второго формирователя 11, элемента И-НЕ 12, первого формирователя 13 и второго элемента И 14.

Устройство работает следующим образом.

После включения устройства на вход

"Начальная установка" (НУ) подается импульс высокого уровня "1", который сбрасывает первый и вторые триггеры.

Генератор импульсов подает на вход счетчика прямоугольные импульсы.

Счетчик при этом находится в режиме последовательного счета, дешифратор в режиме кольцевого счета, а мультиплексор в режиме кольцевого опроса входов. При поступлении на вход синхронизации одного из вторых триггеров перепада сигнала из "0" в "1" выход соответствующего триггера ус- @> танавливается в "1". Когда входной код на адресных входах мультиплексора соответствует номеру установившегося триггера, на инверсном выходе мультиплексора появляется сигнал ну левого уровня, который останавливает генератор, а с прямого выхода сигна» лом высокого уровня устанавливается первый триггер. При этом код на выходах счетчика соответствует адресу канала, по которому пришел инициатив ный сигнал. При наличии на входе РЗР сигнала высокого уровня на выходе

ТПР появляется сигнал низкого уровня, информирующий о наличии инициативного воздействия. Приняв этот сигнал, например, ЭВМ, формирует сигнал

"Строб" (фиг.З). Сигнал "Строб" через первую схему И открывает для считывания кода полного адреса ини 1иативного сигнала коммутатор, у которого входы второй группы - старшие разряды адреса задаются перемычками.

По заданному фронту сигнала "Строб" на выходе первого формирователя появляется импульс ф, которым сбрасывается первый триггер и через соответствующую четвертую схему И, на первый вход которого подается сигнал вы сокого уровня от дешифратора, сбрасывается тот второй триггер, номер которого соответствует адресу на выходе счетчика. После этого схема переходит в исходное состояние. Если одновременно приходит несколько инициативных сигналов, то они обслуживаются в порядке следования их адресов.

При увеличении числа каналов инициативного ввода устройства объединяются по соответствующим входам и выходам, за исключением сигнала

РЗРвх и РЗРвых, который представляет собой последовательную цепь, т.е. сигнал РЗРвых предыдущего устройства подключен на вход РЗРвх последующе го (фиг.2).

Прохождение сигнала РЗР по цепи блокируется при установке первого триггера сигналом с его инверсного выхода через вторую схему И 14.

Устройство, стоящее в цепи первым, имеет наивысший приоритет и его вход

РЗРвх подключен к шине питания устройства. Если сигнал ТПР приходит одновременно от нескольких устройств, то адреса инициативных сигналов выводятся на шину адреса в порядке следования их приоритетов.

Второй формирователь 11 предназначен для задержки заднего фронта входного сигнала разрешения (РЗВвх ) на

,„при одновременной работе нескольких устройств, когда предыдущее устройство формирует сигнал разрешения и уже установлен первый триггер

9 данного устройства.

Увеличение быстродействия и повышение надежности устройства достигается за счет исключения механических элементов из схемы.

Формула и э о б р е т е н и я

Устройство для инициативного ввода адреса, содержащее блок ключей, первый элемент И, первый триггер, дешиф14 i 6964 ратор, счетчик, генератор импульсов, выход которого соединен с тактовым входом счетчика, выходы которого соединены с информационными входами де шифратора и информационными входами коммутатора, выход коммутатора является адресным выходом устройства, управляющий вход коммутатора соединен с выходом первого элемента И, третий вход которого соединен с прямым выходом первого. триггера, первый вход сброса которого является входом начальной установки устройства, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены первый и второй формирователи, второй элемент

И, элемент И-НЕ, мультиплексор, блок регистраторов, содержаший группу элементов И и группу триггеров, информационные входы которых соединены с шиной питания устройства, а тактовые входы являются группой входов пуска устройства, первые входы сброса триггеров группы соединены с входом начальной установки устройства, а вторые входы сброса триггеров группы соединены с выходами соответствующих элементов И группы, первые входы которых соединены с соответствующими выходами дешифратора, вторые входы элементов И группы соединены с вторым входом сброса первого триггера и выходом первого формирователя, вход которого соединен с выходом

5 первого элемента И, первый вход которого является входом стробирования устройства, а второй вход соединен с вторым входом второго элемента И, входом второго формирователя и является входом разрешения устройства, первый вход второго элемента И сое,цинен с инверсным выходом первого триггера, информационный вход которого соединен с шиной питания устройства, тактовый вход первого триггера соединен с прямым выходом мультиплексора, инверсный выход которого соединен с управляка им входом генератора импульсов, выходы триггеров группы соединены с соответствующими информа ционными входами мультиплексора, адресные входы которого соединены с соотве1ствуицими выходами счетчика, 25 первый вход элемента И-HE соединен с прямым выходом первого триггера, второй вход элемента И-НЕ соединен с выходом второго формирователя, а вы" ход элемента И-HE является выходом

gp требования прерывания устройства, выход второго элемента И является выходом разрешения устройства.

1416964

Слтро8

РУРА, 4 ЗР/аи

Составитель А.Алексеев

Техред Л.Сердюкова

Корректор С.йекмар

Редактор Л.Пчолинская

Заказ 4064/45 Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4