Цифровой коррелятор

Иллюстрации

Показать всеРеферат

(Изобретение относится к вычислитёльАой технике и может быть использовано в системах автоматического управления и контроля. 1(ифровой коррелятор содержит два аналого-цифровых преобразователя, четьфе регистра, два блока памяти, элемент ИСКЛЮЧАЮЩЕЕ ШШ, компаратор, элемент И, коммутатор , генератор тактовьк импульсов, сумматор,. блок синхронизации. Цель изобретения - повышение точности оценок значений корреляционных функций. Поставленная цель достигается за счет введения в коррелятор RS-триггера и элемента И-2КЛИ, с помощью которых производится анализ состояния второго старшего разряда большего числа. 1 ил.

СОЮЗ СОВЕТСКИХ

С(К1ИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 G 06 F 15/336

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСХОМУ СВИДЕТЕЛЬСТВУ

Ф

° °

° °

Ъ °

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1251107 (21) 4053501/24-24 (22) 14.04.86 (46) 15.08.88. Бюл. Р 30 (72) В.С.Джус, М.В.Солдатенко и Л.Л.Чайковский (53) 681.3(088.8) (56) Авторское свидетельство СССР

В.1251107, кл. G 06 F 15/336, 1985. (54) ЦИФРОВОЙ КОРРЕЛЯТОР (57),Изобретение относится к вычисли» тельной технике и может быть использовано в системах автоматического управления и контроля. Цифровой кор,.80„„1416980 А 2 релятор содержит два анапого-цифровых преобразователя, четыре регистра, два блока памяти, элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ, компаратор, элемент И, коммутатор, генератор тактовых импульсов, сумматор, блок синхронизации. Цель изобретения — повышение точности оценок значений корреляционных функций.

Поставленная цель достигается за счет введения в коррелятор RS-триггера и элемента И-2KIH с помощью которых производится анализ состояния второго старшего разряда большего числа.

1 ил.

1416980

Изобретение относится к вычислительной технике и может быть исполь-! зовано. в системах автоматического уп::равления и контроля.

Цель изобретения — повышение -.î÷ности цифрового коррелятора.

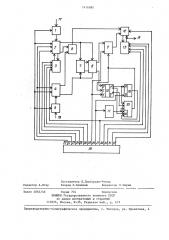

На чертеже представлена схема цифрового коррелятора.

Цифровой коррелятор содержит первый аналого †цифров преобразователь

1, первый регистр 2, первый блок 3 . памяти, второй регистр 4, второй аналого-цифровой преобразователь 5, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6, компаратор 7, 15 коммутатор 8, третий 9 и четвертый 10 регистры, генератор 11 тактовых импульсов, сумматор 12, второй блок 13 памяти, логический элемент И 14, блок

15 синхронизации, RS-триггер 16, пер- 2О вый 17 и второй 18 входы коррелятора, выход 19 коррелятора, с первого по тринадцатый выходы 20-32 блока 15 синхронизации и элемент И-2ИЛИ 33.

Цифровой коррелятор работает следующим образом. . На входы 17 и 18 устройства поступают сигналы Х(Г) и Y(t). Пройдя через аналого-цифровые преобразователи

1 и 5, их оцифрованные модульные зна- 30 чения, представленные в естественной форме, после хранения в соответствующих регистрах 2 и 4 и задержки в первом блоке 3 памяти поступают на входы компаратора 7 и коммутатора 8.

Последние обеспечивают передачу меньшего .по модулю цифрового кода в тре— тий регистр 9, а большего — в четвертый регистр 10..Такое распределение цифровых кодов по регистрам 9 и 10 фактически обеспечивает релейный метод вычисления оценки прямолиней тод вычисления оценки корреляционной функции, так как в дальнейшем все вычислительные операции проводятся только над одним, меньшим по модулю, цифровым кодом, находящимся в третьем регистре 9. Дополнительно к этому в корреляторе производится анализ двух старших разрядов модульного значения большего цифрового кода с целью полу- чения более высокой точности вычисления промежуточных произведений. Полученные таким образом модульные значения произведений поступают на вход сумматора 12, на знаковый вход которого с выхода элемента ИСКЛЮЧА10ЩЕЕ

ИЛИ 6 поступает знак произведения.

В сумматоре 12 совместно с вторым блоком 13 памяти формируется окончательная оценка корреляционной фуйкции й+т-1 л

R<„(Knt) sign Х 1 Ksign У с =Ю Хн-1,l 2 в+И при (Хч-KI 4 I 1 1

-(Kyat j (1) У,)1 ° 2 при Х к 1Yql, где К (К ) — коэффициент, равный числу нулей (числу сдвигов,) между запятой и первой значащей цифрой входного кода Х (Y );

of(p) — коэффициент, учитывающий дополнительный сдвиг, который определяется из условия при а,(Ъ ) = О, ы (p) =

О при а (Ъ ) = 1, где а (Ъ ) — значение второго старшего разряда нормализованного входного кода

Х к(У )

Для организации синхронной -работы отдельньгх блоков в цифровом корреляторе и вычисления оценки корреляционной функции параллельно-последовательным способом в соответствии с выражением (1) используется блок 15 синхронизации. Работа цифрового коррелятора синхронизируется четырьмя последовательностями импульсов, вырабатываемых блоком 15.

Формул а изобретения

Цифровой коррелятор по авт. св.

61251107,отличающийся тем, что, с целью повышения точности, в него введены RS-триггер и элемент

И-2ИЛИ, при этом К-вход RS-триггера подключен к прямому выходу и-го раз ряда четвертого регистра, инверсный выход (n-1) — го разряда которого соединен с вторым входом элемента И2ИЛИ, третий и четвертый входы которого подключены к выходу генератора тактовых импульсов, инверсный выход п-ro разряда четвертого регистра соединен с пятым входом элемента И-2ИЛИ, шестой вход которого подключен к пряI мому выходу RS-триггера, S — вход которого соединен с десятым выходом блока синхронизации.

1416980

Составитель Л.Григорьян-Чтенц

Техред Л.Олийнык Корректор С.Черни

Редактор А.Огар

Заказ 4065/46

Тираж 704 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

ll3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4