Устройство для контроля цифровых блоков

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для контроля периферийных БИС5 например, серии КР580. Целью изобретения является повьязение надежности устройства. Устройство содержит блок 1 сш хронизации, блок 2 адресования, сигнатурный анализатор 5, блок 6 формирования управляющих и адресных сигналов, блок 7 памяти данных и блок 8 управляющей памяти. Повышение надежности обеспечивается за счет меньших по сравнению с прототипом затрат памяти программ Это достигается тем, что наиболее высокочастотные к малые по длительности входные сигналы контролируемой,БИС (синхронизации, чтения, записи) формируются аппаратно, а в памяти хранятся только команды и данные, число которых невелико. 3 ил. с ф (Л е о со со d

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК д11 4 G 06 F 11/26

ВС1", ., 3 3

4 "Э

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTGPCHGMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21 ) 4084874/24-24 (22) 04.07.86 (46) 15,08.88. Бюл, У 30 (?1) Всесоюзный научно-исследовательский, проектно-конструкторский и технологический институт релестроения (72) В.А. Герасимов (53) 681.3 (088,8) (56) Механизация и автоматизация управления, 1983, В 3 (117), с. 41-43.

Средства диагностирования и отладки микропроцессорных систем: Материалы семинара, 14-15 июня 1984 г, Л. общество "Знание", Лениградский

Дом научно-технической пропаганды, с ° 32-36, фиг. 1. (54) УСТРОЙСТВО- ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ (57) Изобретение относится к вычис„„SU„„1416995 А1 лительной технике и может быть использовано для контроля периферийных

БИС, например, серии КР580. Целью изобретения является повьлиение надежности устройства. Устройство содержит блок 1 синхронизации, блок 2 адресоэания, сигнатурный анализатор

5, блок 6 формирования управляющих и адресных сигналов, блок 7 памяти данных и блок 8 управляющей памяти.

Повышение надежности обеспечивается

1 за счет меньших по сравнению с прототипом затрат памяти программ. Это достигается тем, что наиболее высокочастотные и малые по длительности входные сигналы контролируемой„БИС

1 синхронизации, чтения, записи) формируются аппаратно, а в памяти хранятся только команды и данные, число которых невелико. 3 ил.

1416995

Для проверки программируемых БИС, например. периферийных БИС микропроцессорного набора КР580, необходимо последовательно программировать различные режимы работы БИС и проверять правильность их выполнения. При этом необходимо формировать последовательности команд и данных, записывать их в регистр команд или в регистр данных проверяемых БИС соответственно и считывать слово состояния и регистр данных. Выбор внутреннего регистра осуществляется посредством адресных входов проверяемой

БИС. Запись ичтение. информации инициируются сигналами записи и чтения.

В связи с тем, что время выполнения различных команд в разных регистрах различно, распределение сигналов записи и чтения во времени неравномерно и для их формирования обычно используют мткропроцессор илимикропрограммный автомат. В предлагаемом устройстве сигналы записи и чтения во времени распределены равномерно, с ними синхронизирован поток данных.

Такое решение при простой схеме позволяет значительно сократить объем памяти программ.

В процессе работы устройства блок

6 формирования сигналов из последовательности импульсов синхронизации

Изобретение относится к вычислительной технике и может быть использовано для контроля БИС, например, серии КР580 и сервисного оборудова5 ния электронной аппаратуры на базе

БИС, Цель изобретения — повышение надежности устройства за счет сокращения объема оборудования(ПЗУ для хранения тестовых программ ).

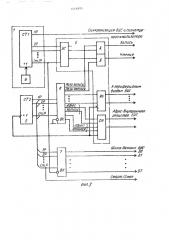

На фиг. 1 приведена структурная схема устройства; на фиг. 2 — пример конкретной реализации устройства; на фиг. 3 — временные диаграммы его работы.

Устройство (фиг. 1) содержит блок

1 синхронизации, блок 2 адресования и блок 3 памяти. Позицией 4 обозначена контролируемая БИС. Устройство содержит также сигнатурный анализатор

5 и блок 6 формирования управляющих .и адресных сигналов. В состав блока

3 памяти входят блок 7 памяти данных и блок 8 управляющей памяти. 25

Устройство работает следующим об-.. разом. вырабатывает в заранее определенные моменты времени сигналы записи и чтения информации из проверяемой БИС

4 (фиг,3). Блок 8 управляющей памяти через блок 6 формирования сигналов себспечивает выбор внутреннего регистра или порта БИС, B KQTopbIA или из которого производится запись-чтение информации., и разрешает или запрещает запись-чтение информации. Кроме того, с выходов блока 8 осуществляется воздействие на периферийные входы БИС. С выхода блока 7 на шине данных контролируеиой БИС 4 устанавливается управляющее слово или данные на время действия сигнала записи.

Во время действия сигнала чтения выход блока 7 блокируется сигналом ВК с блока 1 синхронизации (разряд m

СТ 1, фиг.2) чтобы не искажать считываемую информацию. Блоки 7 и 8 выдают и изменяют информацию под воздействием блока 2 адресования, который последовательно циклически изменяет свое состояние под действием импульсов синхронизации. Сигналы, поступающие на БИС по периферийным входам, обеспечивают выполнение этой

БИС заданного режима работы.

Сигналы с выходов проверяемой БИС поступают на входы данных сигнатурного анализатора 5. Для их правильной обработки анализатор имеет два управляющих входа. Вход синхронизации служит для стробирования входных данных. С помощью этого сигнала анализатор принимает данные с входов во внутренний регистр и производит их логическую обработку. Сигнал окна изиерения (разрешения приема данных) указывает на начало и окончание тестовой процедуры. В качестве сигнала синхронизации используется сигнал синхронизации БИС, чем обеспечивается регистрация откликов проверяемой БИС в каждом такте. В качестве сигнала окна измерения используется старший разряд блока 2 адресования (фиг.2), который изменяет свое состояние с

l1 l t 11 !!

1 в 0 при окончании теста и воз-. врате к началу тестовой программы.

В примере конкретного исполнения устройства (фиг,2 ) в качестве блока синзронизации используется двоичный счетчик СТ1 совместно с генератором импульсов G. Разряды счетчика используются для синхронизации контролируемой БИС и формирования с помощью

1416995

Устройство для контроля цифровых блоков, содержащее блок синхронизации, блок адресования и блок памяти данных, причем первый выход блоха синхронизации является выходом устройства для подключения синхровхода контролируемого блока, второй выход блока синхронизации соединен с синхровходом блока адресования, первая группа выходов которого соединена с группой адресных входов блока памяти данных, группа выходов которого является группой выходов устройства для подключения входов данных контролируемого блока, о т л и ч а ю щ е е с ятем, что, с целью повьппения надежности устройства за счет сокращения оборудования, оно содержит блок формирования управляющих и адресных сигналов, сигнатурный анализатор и блок управляющей памяти, группа адресных входов которого объединена с группой адресных входов блока памяти данных, синхровход блока формирования управляющих и адресных сигналов подключен к третьему выходу блока синхронизации, группа информационных входов блока формирования управляющих и адресных сигналов подключена к группе выходов блока управляющей памяти, а первая группа выходов блока формирования управляющих и адресных сигналов является группой выходов устройства для подключения управляющих и адресных входов контролируемого блока, второй выход блока формирования управляющих и адресных сигналов соединен с входом разрешения блока памяти данных, синхровход сигнатурного анализатора соединен с первым выходом блока синхронизации, группа информационных входов сигнатурного анализатора является группой информационных входов устройства для подключения выходов контролируемого блока, управляющий вход окна измерения сигнатурного анализатора соединен. с вторым выходом блока адресования,.

Предлагаемое устройство по сравнению с известным характеризуется вы- 55 сокой надежностью и малой стоимостью за счет значительно меньших затрат памяти программ. Это обеспечивается дешифратора DC сигналов чтения и за— писи. На входы БИС сигналы чтения и записи поступают со схемы совпадения, управляемой сигналами Разрешение записи и "Разрешение чтения что позволяет гибко формировать тестовую процедуру. Сигналы "Адрес запи— си" и "Адрес чтения" поступают.на входы контролируемой БИС через комму- 1О татор сигналов CN синхронно с сигналами записи и чтения соответственно и определяют в какой или из какого внутреннего регистра или порта БИС будет произведена запись-чтение ин- 15 формации. Управление коммутатором осуществляется разрядом ш счетчика

СТ1. При равенстве его "О" формируется сигнал записи, при равенстве "1" чтения (фиг.З). Этим же разрядом 20 разрешается выдача информации из блока 7 памяти данных на шину данных контролируемой БИС при наличии сигнала записи и запрещается работа памяти данных при чтении информации из БИС.

Блок 2. адресования в данном устройстве.представлен двоичным счетчиком СТ2, управляемым от блока синхронизации. Изменение состояния СТ2 30 (прибавление единицы к состоянию счетчика ) осуществляется в конце цикла записи-чтения. При этом изменяется информация на выходах блока памяти и производится очередная проверка БИС.

Управление периферийными входами гроверяемой БИС осуществляется сигналами блока 8 управляющей, памяти через буферный регистр КС, расположенный в блоке 6. Регистр необходим для 40 исключения ложных импульсов, которые могут иметь место на выходах, микросхем ПЗУ блока 8 управляющей памяти в моМент изменения адреса блоком 2 адресовачия (счетчик CT2). При этом из- 5 менение состояния счетчика СТ2 происходит по переднему фронту сигнала инкрементирования блока адресования (разряд ш счетчика СТ1), а прием в регистр — по заднему, когда информа- 50 ция на выходах ПЗУ уже стабильна и достоверна. тем, что наиболееE высокочастотные и малые пс длительности входные сигналы контролируемой БИС (синхронизации, чтения, записи)формируются аппаратно, а в памяти хранятся только команды и данные, число которых невелико.

Формула изобретения

1416995

77gp1416995

Составитель С. Старчихин

Техред Л.Сердюкова Корректор В.Гирняк

Редактор А.Огар

Тираж 704

Заказ 4066/47

Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4