Запоминающее устройство с резервированием

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и -может быть использовано при построении полупроводниковых запоминающих устройств. Целью изобретения является повьшение быстЮ родействия за счет ускоренного сброса сигналов на выходе дешифратора адреса. Поставленная цель достигается введением группы элементов И 11, которые на время смены сигналов на адресном входе 10 устройства блокируют адресный вход резервного накопителя 2 и выход дешифратора 4 адреса, наличие у которого входа блокировки позволяет ускоренно сбрасывать сигналы на его выходе. Указанные меры позволяют уменьшить взаимное перекрытие сигналов на выходах основного 1 и резервного 2 накопителей, что повышает быстродействие запоминающего устройства и снижает потребляемую мощность. 2 ил. (Л с 12 о

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (И) СЮ4 С С29 00

ОПИСАНИЕ .ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4176895/24-24 (22) 24.10.86 (46) 15.08.88. Бюп. В 30 (72) П.М.Гафаров, Д.Е.Ковалдин, С.А.Насонов и О.А.Титов (53) 681.327.6 (088 ° 8) (56) Электроника, 1981, Ф 15, с.44, Патент CHIA У 4346459, кл. С 11 С 8/00, опублик. 1982 . (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕ3ЕРВИРОВАНИЕМ (57) Изобретение относится к вычислительной технике и -может быть использовано при построении полупроводниковых запоминающих устройств. Цепью изобретения является повышение быстродействия за счет ускоренного сброса сигналов на выходе дешифратора адреса. Поставленная цель достигается введением группы элементов И 11, которые на время смены сигналов на адресном входе 10 устройства блокируют адресный вход резервного накопителя

2 и выход дешифратора 4 адреса, наличие у которого входа блокировки позволяет ускоренно сбрасывать сигналы на его выходе. Указанные меры позво" ляют уменьшить взаимное перекрытие сигналов на выходах основного 1 и резервного 2 накопителей, что повышает быстродействие запоминающего устройства и снижает потребляемую мощность. .2нл.

1417042

Изобретение относится к вычислительной технике и может быть использовано при построении полупроводниковых запоминающих устройств (ЗУ), Целью изобретения является повышение быстродействия ЗУ sa счет ускоренного сброса сигналов на выходе дешифратора адреса.

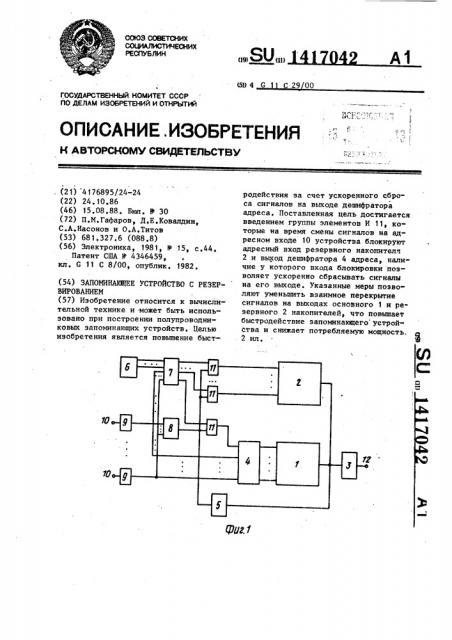

На фиг„1 представлена функциональ- 1 ная схема ЗУ с резервированием; на фиг.2 — временные диаграммы его работы.

ЗУ с резервированием (фиг.1) содержит основной 1 и резервный 2 накопители, усилитель 3 записи-считывания, Дешифратор 4 адреса, блок 5 предзаряда, блок 6 хранения резервных адресов, блок 7 формировайия резервных адресов, детектор 8 смены ðeñà, 20 группу адресных формирователей 9, входы 10 адреса устройства, группу элементов И 11 и информационный вход/ выход 12 устройства.

Устройство работает следующим об" разом.

В режиме обращения при неизменных адресных сигналах на входах 10 ЗУ на выходе адресных формирователей 9 устанавливается адрес, на выходе детектора 8 смены адреса сформированы разрешающий уровень (в данном случае — высокий логический уровень).

Ксли адрес на входах 10 совпадает с адресами, хранимыми в блоке 6 хранения резервных адресов, т.е. при обра- 35 щении к резервному накопителю 2, то на соответствующем выходе блока 7 и на выкоде соответствующего элемента

И 1 1 сформированы сигналы, разрешающие выборку элементов памяти из резервного накопителя 2 (высокий логический уровень).

На выходе равенства блока 7 и на выходе первого элемента И 11 сформированы сигналы, запрещающие работу 45 дешифратора 4 (низкий логический уровень) и выборку из основного накопителя 1. Происходит выбор элементов памяти из резервного накопителя 2.

При обращении к основному накопи- 50 телю 1 на выходах блока 7 установле» ны уровни логических сигналов, запрещающие выборку из резервного накопителя 2 (низкий логический уровень), на выходе равенства блока 7, выходе первого элемента И 11 и на входе блокирования дешифратора 4 сформированы разрешающие сигналы (вь.сокий логический уровень)„

Таким образом происходит выбор элементов памяти из основного накопителя 1, данные из которых поступают на вход усилителей записи — считывания 3 и на информационный вход/выход ЗУ в режиме считывания.

Процесс выборки элементов памяти нри записи происходит аналогично, данные с входа/выхода данных ЗУ Ilo ступают на входы/выходы основного и резервного накопителей и записываются в выбранные элементы памяти.

При изменении любого адресного сигнала на входах 10. ЗУ на выходе детектора 8 смены адреса появляется кратковременный импульс смены адреса, имеющий логический уровень, на выходах элементов И 11 формируется уровень сигнала, запрещающий работу дешифратора 4 и выбор элементов памяти из основного и резервного накопителей., независимо от логических уровней сигналов на вторых входах элементов

И 11 (фиг.2д,е) . Таким образом, при смене адресных сигналов на входах

ЗУ происходит кратковременный запрет обращения к накопителям, осуществляется быстрый сброс сигналов выборки и сигнала на втором входе дешифратора 4, происходит установка сигналов на адресных входах накопителей. Через определенное время, задаваемое детектором 8 смены адреса (например, через время, равное времени установления сигналов на выходах адресных формирователей 9), на выходе детектора 8 смены адреса устанавливается уровень сигнала, разрешающий выборку элементов памяти, на выходе элементов

И 11 формируются сигналы, соответствующие статическому состоянию.

Введение дополнительных элементов

И 11, управляемых сигналами с выхода детектора 8 смены адреса, позволяет обеспечить быстрый сброс сигналов на втором входе дешифратора 4, на адресных входах накопителей, При этом ускоряется сброс сигналов выборки на адресных входах резервного накопителя и сигнала запрета работы дешифратора, которые определяют быстродействие ЗУ, исключается возможность одновременного подключения к усилителю записи-считывания элементов памяти с различной хранимой информацией, что приводит к повышению быстродействия

ЗУ, с а

4дресиые

Aooor w

8аиод

Вотентора сиеиы сиенмод одресо

Адресиые осиооиоео риероиого

rrorronu ress г

Адресиые

Nroibr ocuo

cr резердио иокопите г идресиые . Входа оси

cr рл@оди иол опыта д е рдрусные дхоои осиодиоео и

rroto uouou

Фиг 2

3 (41

Формула изобретения

Запоминакпцее устройство с резервированием, содеркащее основной и резервный накопители, усилител записи-считывания, дешифратор адреса, блок предзаряда, детектор смены адреса, блок формирования резервных адресов, блок хранения резервных адресов, группу адресных формирователей, входы которых являются адресными входами устройства, выходы адресных формирователей группы соединены с соответствующими разрядами входа детектора смены адреса и с соответствуницими разрядами первого входа блока формирования резервных адресов, разряды второго входа которого соединены с выходами блока хранения резервных адресов, выход детектора смены адреса соединен с входом блока предзаряда, выход которого соединен с информационными входами/выходами основного и резервного накопителей и с входом усилителя записи-считывания, выход которого является информационным входом/выходом устройства, вход адреса основного накопителя соединен с

7042

4 выходом дешифратора адреса, разряды информационного входа которого соединены с соответствующими выходами

5 адресных формирователей группы о тУ л и ч а ю щ е е с я тем, что, с целью повышения быстродействия за счет ускоренного сброса сигналов на выходе дешифратора адреса, в него введе10 на группа элементов И, причем выход первого элемента И группы соединен с входом блокировки дешифратора адреса, первый и второй входы первого элемента И группы соединены соответ1 ственно с выходом детектора смены адреса и с выходом равенства блока формирования резервных адресов, выходы элементов И группы с второго по (М+1)-й (М - разрядность адреса резервного накопителя) соединены с сО

20 ответствующими разрядами входа адреса резервного накопителя, первые входы элементов И группы с второго по (М+1)-й соединены с выходом детекто2 ра смены адреса, вторые входы элементов И группы с второго по (М+1)-й со единены с соответствующими разрядами информационного выхода блока формирования резервных адресов.