Устройство для моделирования процесса программирования задач на эвм

Иллюстрации

Показать всеРеферат

СОЮЗ СО8ЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) (51) 4 С 06 F 15/20

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И.ОТНРЫТИЙ (21) 4195351/24-24 (22) 16.02.87 (46) 23.08.88. Бюл. № 31 (75) В.П.Морозов, В.Н.Барулин, Я.С.Дымарский и О.Е.Климова (53) 681.3 (088.8) (56) Авторское свидетельство СССР № 1059577, кл. С 06 F 15/20, 1982.

Авторское свидетельство СССР №- 1310836, кл. G 06 F 15/20, 1985, (54) VCTPOACTBO ДЛЯ МОДЕЛИРОВАНИЯ

ПРОЦЕССА ПРОГРАММИРОВАНИЯ ЗАДАЧ НА

ЗМВ (57) Изобретение относится к цифровой вычислительной технике и может быть использовано для моделирования процесса программирования задач для решения на ЭВМ. Цель изобретения— расширение функциональных возможностей за счет моделирования уменьшения числа ошибок при отладке программного обеспечения. Цель достигается введением в устройство элемента НЕ и группы генераторов случайных импульсов ошибок. Устройство обеспечивает возможность моделирования процесса сокращения ошибок в проектируемом программном обеспечении за счет адаптации и настройки технологического конвейера в процессе его функционирования. 1 ил.

1418741

Изобретение относится к цифровой вычислительной технике и может быть

40 использовано для моделирования процесса программирования задач для решения на ЗВМ.

Цель изобретения — расширение функциональных возможностей за счет моделирования уменьшения числа ошибок при отладке программного обеспечения. 10

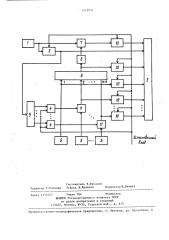

На чертеже приведена схема предлагаемого устройства.

Устройство содержит генератор 1 ! импульсов, счетчик импульсов, блок 7

3 индикации, группу триггеров 4,груп-15 ,пу генераторов 5 случайных импульсов ошибок, элемент HE 6, элемент И 7, элемент ИЛИ 8, дншифратор 9, счетчики

10 и группу элементов И 11.

Устройство работает следующим об- 20 разом.

Перед началом работы устройства . через его установочный вход на установочные входы всех счетчиков импульсов и на входы всех триггеров 4 по- 25 ступает управляющий сигнал, обнуляющий счетчики импульсов и устанавливающий триггеры 4 в состояние "1, чем разрешается прохождение сигналов через элементы И 11.

Генератор 1 импульсов вырабатывает последовательность импульсов, моI делируя последовательность кодов операторов (машинных команд) программы.

Количество импульсов с выхода генератора 1 импульсов подсчитывается счет-35 чиком 2 импульсов.

Импульсы с выхода генератора 1 импульсов поступают также на вход элемента И 7.

Генераторы 5 случайных импульсов ошибок генерируют в случайные моменты временй импульсы со случайной длительностью, которые через элемент

ИЛИ 8 и элемент HF. 6 поступают на вход элемента И 7. Если на выходе генераторов 5 появится случайный сигнал, то запрещается прохождение сигналов через элемент И 7, Если на выходах генераторов 5 случайные сигналы отсутствуют, что разрешается прохождение сигналов через элемент

И 7.

Выход счетчика 2 импульсов соединен с входом дешифратора 9, При определенной временной наработке (код в счетчике 2 импульсов достиг значения

Л ) на первом выходе дешифратора 9

1 появляется управляющий сигнал, который устанавливает первый триггер 4 в состояние "0", чем будет запрещено прохождение сигналов через первый элемент И 11, Так будет происходить до тех пор, пока код в первом счетчике 2 импульсов не достигнет значения

А„. При этом íà N-м выходе дешифратора 9 появляется управляющий сигнал, который устанавливает N-й триггер 4 в состояние "0", чем будет запрещено прохождение сигналов через N - -й элемент И 11. Таким образбм, суммарный поток ошибок ступенчато уменьшается во времени до минимального потока ошибок, определяемого первым генератором 5 случайного потока импульсов.

Формула изобретения

Устройство для моделирования про-. цесса программирования задач на ЭВМ, содержащее генератор импульсов, счетчик импульсов, элемент И, элемент

ИЛИ, группу элементов И, группу триггеров и дешифратор, входы которого соединены соответственно с разрядными выходами счетчика импульсов, счетный вход которого подключен к выходу генератора импульсов и первому входу элемента И, выходы элементов И группы соединены соответственно с входами элемента ИЛИ, а первые входы элементов И подключены соответственно к прямым выходам триггеров группы, единичные входы которых и установочный вход счетчиков объединены и являются установочным входом устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет моделирования уменьшения числа ошибок при отладке программного обеспечения, оно дополнительно содержит элемент НЕ и группу генераторов случайных импульсов ошибок, причем выход элемента ИЛИ через элемент НЕ соединен с вторым входом элемента И, выход которого является выходом устройства, выходы дешифратора подключены соответственно к нулевым входам триггеров группы, выход первого генератора случайных импульсов ошибок группы подключен к входу элемента ИЛИ, а выхолы остальных генераторов случайных импульсов ошибок группы подключены соответственно к вторым входам элементог группы.

1418741

Составитель В.фукалов

Редактор Г.Волкова Техред А. Кравчук

Корректор В.Бутяга

Заказ 4155/47 Тираж 704 Подписное

ВПИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4