Блок буферной памяти для терминального устройства

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих запоминающих устройств для обработки отображения и ввода в ЭВМ графических изображений. Цель изобретения - упрощение блока. Устройство содержит генератор 1 тактовых импульсов, счетчики 2 и 3 адресов, матричные блоки 5 оперативной памяти , адресный коммутатор 8, блок 9 постоянной памяти, счетный триггер 10, сумматор 11 по модулю два. Упрощение блока достигается путем более полного использования имеющегося объема оперативной памяти, работы в режиме ввода-вывода в обоих полукадрах прогрессивной развертки и исключения выходных коммутаторов. Управляющие сигналы блока вырабатьгааются с временным сдвигом относитетельно соответствующих сигналов в пр адыдущем полукадре. 2 ил. (Л СХ) 00 tc Ф

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК II q С 11 С 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ОО

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4200832/24-24 (22) 26.02.87 (46) 23.08.88. Бюл. И 31 (71) Львовский политехнический институт им. Ленинского комсомола (72) И.Б.Боженко и П.А. Кондратов (53) 681.327(088.8) (56) Патент США 11 4281401, кл . 365/87, опублик. 1981.

Авторское свидетельство СССР

У 1231535, кл. G !1 С 11/00, 1984. (54) БЛОК БУФЕРНОЙ ПАМЯТИ ДЛЯ ТЕРМИНАЛЬНОГО УСТРОЙСТВА (57) Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих запоминающих устройств для обработки отображения и ввода в ЭВМ

„„SU, 1418812 А1 графических изображений. Цель изобретения — упрощение блока. Устройство содержит генератор I тактовых импульсов, счетчики 2 и 3 адресов, матричные блоки 5 оперативной памяти, адресный коммутатор 8, блок 9 постоянной памяти, счетный триггер

10, сумматор 11 по модулю два. Упрощение блока достигается путем более полного использования имеющегося объема оперативной памяти, работы в режиме ввода-вывода в обоих полукадрах прогрессивной развертки и исключения выходных коммутаторов. Управляющие сигналы блока вырабатываются с временным сдвигом относитетельно соответствующих сигналов в пр дыдущем полукадре. 2 ил.

14 l 8812 !

Из< сретение относится к вычи лительной технике и может быть использовано при построении быстродействуюэл«оминI>oil!Hx QcTp(>IIcI н большого объема для обработки, вводя н 3IIM и отображения графических иэображений.

Цель изобретения — упрощение блока

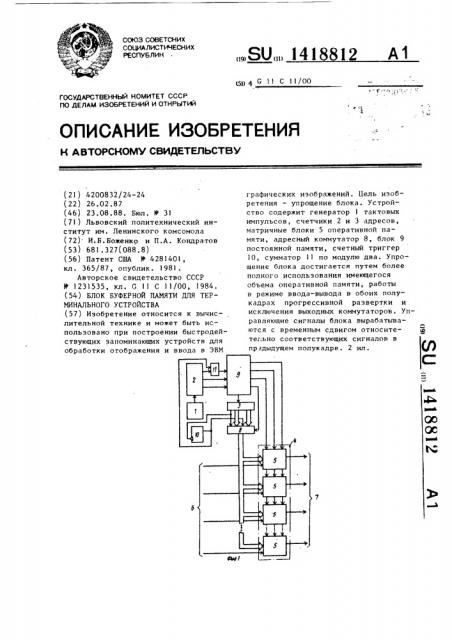

На фиг. l представлена функцио- f0 нальнля схемл блока буферной памяти для терминального устройства, на фиг. 2 — временные диаграммы его работы.

Блок содержит (фиг. 1) генератор 15

1 тактовых импульсов, первый 2 и второй 3 счетчики адресов, блок 4 памяти, состоящий из отдельных, по числу разрядов, матричных блоков 5 оперативной памяти, информационные входы 6 и вы- /О ходы 7, адресньн1 коммутатор 8, блок управления записью (считыванием, вы полненным, например, в виде блока 9 постоянной памяти), счетный триггер

10 и сумматор 11 по модулю два. 25

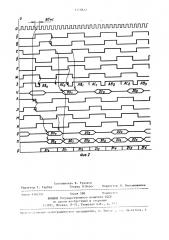

Нл фиг. 2 обозначены: а — сигнал тактовой частоты 20 МГц, б — сигналы блока в первом полукадре развертки; 6 — сигнал на выходе сумматора ll по модулю два, в,г, 30 соответственно сигналы выборки строк

RAS и столбцов СА$ блока 4, д сигналы управления записью; е — сигналы модификации счетчика 3 адресов, ж — сигналы управления коммутато« ром 8 з — последовательность поступления сигналов с выхода коммутатора 8, и — сигналы на выходах блока, к-o — сигналы блока во втором полукадре Развертки; к — сигнал íà 40 выходе сумматора 11; л-н — соответственно сигналы RAS, GAS, WE о сигнал на выходе блока; п — последовательность отображения выходной информации, р — последовательность по- 45 ступления входной информации.

Устройстве работает следующим об— разом.

Выходным сигналом генератора 1 тактовых импульсон (фиг. 2,а) запускается счетчик 2. Выходные напряжения счетчика 2 подаются нл адресные входы блокл 9. Сумматор 11 по состоянию счетного триггера 10 управляет полярностью поступающего

55 на нх1ц бл >кл 9 сигнала старшего р л э р >1д л с l!. . 1 1 ик 1

1> >>

При .л1с гочн>1и 1 три1 гера 10 сигпл 1 с тар11>ег, рлэрядл счетчика 2 передается нл вход блока 9 не инвертируясь (фиг. 2,6), при состоянии

"0" он иннертируется (фиг. 2,к).

К фронтам сигналон счетчика 2 привязаны управляющие сигналы, генерируемые блоком 9 с периодом 400 нс:

RA$, СА$, WE, модификации счетчика

3 и управления коммутатором 8.

Счетчик 3 модифицируется по переднему фронту сигнала с четвертого выхода блока 9 (фиг.2,е). По состоянию

"0" сигнала на пятом выходе блока 9 (фиг. 2,ж) коммутатор 8 подключает к адресным входам блоков 5 семь младших разрядов счетчика 3 (сигналы

АЛ -АЗ ) и сигнал состояния тригге1 ра 10 — АБ (фиг. 2,з). По отрицательному фронту сигнала RAS с перного входа блока 9 (фиг. 2,в) .сигнал

АВ заносится в лдресные регистры блоков 5. По состоянию "1" сигнала управления коммутатором 8 (фиг.2,ж) к адресным входам блоков 5 подключаются старшие разряды счетчика 3 сигналы АС,-ACI,(фиг. 2,з)..По отрица гельному фронту сигнала CAS с второго входа блока 9 (фиг.2,г) сигнал

АС заносится в адресные регистры блоков 5, производится ныборка микросхем памяти блоков 5 и на выход 7 блока поступает считанная информация (фиг.2,и). По положительному фронту сигнала СЛ$ выходы блоков 5 переходят в третье состояние.

По отрицательному фронту сигнала

УЕ с третьего выхода блока 9 (фиг.2,д) информация, поступающая на входы 6 блока (фиг. 2,р), заносится в выбранные ячейки памяти.

В первом полуклдре (при состоянии

"1" триггера 10) выборка ячеек блоков 5 производится перебором адресов

AR,-AR 1,AC-,-AC при АЛ,= 1. Тлк обрабатывается первый полуклдр изображения.

По переполнению счетчика 3 отрицательным фронтом стлрп>его разряда счетчика 8 триггера 10 устлнлнливлется н состояние "О" и начинается обр;1боткл второго полуклцрл. Сигнлл, поступлкщий нл нхоп блока 9 с суммлторл 11, инвертируется. Тем самым обеспеч11нлется сдн11г 11л 00 нс сигнллон, генерируе.l!,>х 6: ..окг м 9 но нтором полуклдре (фиг. ?,л-и). Выборка ячеек памяти 11Го11 »> TI! Tc ÿ перебором адресов при Al>>- (. «, >рмлпия поступает на выход 7 «, чл11гом l»; 400 нс з )4) относительно информации, считанной в первом полукадре. Затем по переполнению, счетчика 3 триггер )О вновь устанавливается в состояние ")" и начитается обработка первого полукадра.

Последовательность отображения иэображения, образованного положением первого и второго полукадров прогрессивной развертки (фиг. 2,п)

Требование регенерации информции в. блоке 4 памяти обеспечивается путем перебора адресов АН -AR в течение строки полукадра развертки эа 64 мс.

Формула изобретения

Блок буферной памяти для терминального устройства, содержащий генератор тактовых импульсов, первый и второй счетчики адресов, блок управления записью-считыванием, адресный коммутатор и матричные блоки оперативной памяти, информационные входы которых являются информационными входами устройства, информацион. ные выходы устройства, информационные выходы матричных блоков оперативной памяти являются информационными выходами устройства, адресные входы матричных блоков оперативной памяти поразрядно объединены и подключены к выходам адресного коммутатора, выход генератора тактовых

88) 2

З импульсов подключен к счетному входу первого счетчика адресов, выходы младших разрядов которого подключены к младшим адресным входам блока управления записью-считыванием, первый, второй и третий выхоцы которого соединены соответственно с входами выборки строк, выборки столбцов и входами записи матричных блоков оперативной памяти, четвертый и пятый выходы блока управления записью-считыванием соединены соответственно со счетным входом второго счетчика адресов и управляющим входом адресного коммутатора, выходы младших и старших разрядов второго счетчика адресов подключены соответственно к информационным входам первой и второй групп адресного коммутатора, о т л и ч а ю щ и йс я тем, что, с целью упрощения блока, в него введены счетный триггер и сумматор по модулю два, выход которого подключен к старшему адресному входу блока управления записью-считыванием, первый вход сумматора по модулю два и информационный вход адресного коммутатора соединены с выходом счетного .триггера, счетный вход которого подключен к выходу старшего разряда второго счетчика адресов, второй вход сумматора по модулю два соединен с выходом старшего разряда первого счетчика адресов.

14 1881 2

Фиа 2

Составитель В. Рудаков

Редактор Г. Гербер Техред И.Верес

Корректор М. Максимишинец Закав 4162/51

Прои » лственно-полит.рафическое предприятие, r. Ужг< р:., ул. 11р< ектная, 4 а

О

8 у

Тираж 590 Подпис ню с

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

11 3035, Москва, Ж-35, Раушская наб ., д. 4 5