Преобразователь форматов данных

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

150 4 H 03 М 7/12

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMY СВИД .:ТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3977743/24-24 (22) 19.11.85 (46) 23.08.88. Бюл. 11 31 (71) Институт кибернетики им. В.М.Глушкова (72) В.П.Боюн, Б.H.Малиновский, В.E.Ðåóöêèé и М.Е.урсу (53) 681.325(088.8) (56) Авторское свидетельство СССР

У 717755, кл. Н 03 М 7/12, 1977.

Авторское свидетельство СССР

Ф 1092490, кл. Н 03 М 7/12, 1982. (54) ПРЕОБРАЗОВАТЕЛЬ ФОРМАТОВ 1АННЫХ (57) Изобретение относится к цифровой вычислительной технике и может

„vcr Характерискнка

ÄÄSUÄÄ 1418909 А1 быть использовано при построении уст1 ройств согласования ЭВМ с различными форматами данных. Целью изобрете" ния является расширение класса решаемых задач эа счет обеспечения воэможности преобразования в формат данных с шестнадцатиричным основанием.

Для этого в преобразователь форматов данных, содержащий счетчик порядка 1, блок сдвига 2, триггер знака 3, коммутатор мантиссы 8 и блок управления 9, дополнительно введены дешифратор нулевой характеристики 4, элемент ИЛИ-НЕ 5; элементы ИЛИ 6, 7.

2 ил, 2 табл, Фаю исса

1418909

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении устройств согласования ЭВМ с различными форматами представления данных.

Цель изобретения — расширение класса решаемых задач за счет обеспечения возможности преобразования в формат данных с шестнадцатиричным основанием.

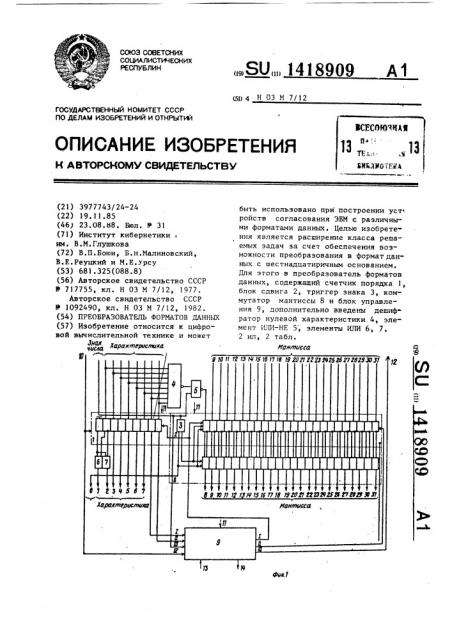

На фиг ° 1 приведена блок-схема предлагаемого преобразователя; на фиг.2 — схема блока управления.

Предлагаемый преобразователь 15 (фиг. 1) содержит счетчик 1 порядка, блок 2 сдвига, триггер 3 знака мантиссы, дешифратор 4 нулевой характеристики, элемент ИЛИ-НЕ 5, элементы

HJIH 6-7, коммутатор 8 мантиссы, блок 20

9 управления, вход 10 разрешения приема, тактовый вход ll выход 12 занятости, вход 13 окончания приема и выход 14 разрешения выдачи.

Блок управления (фиг.2) содержит 25 элемент HE 15, элементы ИЛИ 16-17, элемент НЕ 18, триггеры 19-20, элементы И 21-23.

Принцип построения и работу предлагаемого преобразователя рассмотрим 30 на примере преобразования форматов данных ЭВМ СМ-4 в формат EC ЭВМ.

Двоичные числа с плавающей запятой в формате ЭВМ СМ-4 представляются следующим образом: 1 разряд — знак 35 числа; 8 разрядов — характеристика;

23 разряда — мантисса.

Основание системы счисления в формате ЭВМ СМ-4 принято равным двум, поэтому нормализация чисел осуществ- 40 ляется с точностью до одного разряда.

Порядок чисел представляется уве7 личенным на 2 128, т. е. смещенным на числовой оси в положительном направлении на 7 разрядов ° s результате 45 чего все порядки положительны и являются характеристиками, Положительная мантисса представляется в прямом коде со знаковым разрядом, равным кулю. Отрицательная мантисса представляется в дополнитель50 ном коде со знаковым разрядом, равным единице.

Диапазон представления нормализованных двоичных чисел (по абсолютной

55 величине) находится в пределах от

8 о 2+ 11

Шестнадцатиричные числа с ялаваюme@ запятой в формате ЕС 38M представляются следующим образом: 1 разряд — знак числа; 7 разрядов - характеристика; 24 разряда — мантисса.

Основание системы счисления в этом формате принято равным 2 = 16, поэтому нормализация чисел осуществляется с точностью до тетрады.

Порядок чисел представляется увеличенным на 2 = 64, т.е. смещенным

° 6

1 на числовой оси в положительном направлении на 6 разрядов, в результате чего все порядки положительны и являются характеристиками.

Положительные числа с плавающей t запятой во всех моделях ЕС

ЭВМ в оперативной памяти хранятся в прямом коде. Знак числа определяется по значению двоичной цифры в знаковом разряде.

Диапазон представления нормализованных шестнадцатиричных чисел (по абсолютной величине) определяется пределами от 16 до 16, т.е. значительно шире, чем диапазон представления чисел в формате ЭВМ CM-4.

Входной код в формате с плавающей запятой и двоичным основанием можно записать в следующем виде (1)

Выходной код записывается следующим образом:

16 М1 = 2 ° М 1 где Е и М вЂ” характеристика и мантисса соответственно, а Y — число, дополняющее F. до кратного четырем. Приравняв уравнения (1) и (2), получим:

Е1+Y М1

Е

М, (4) - 4 — >1I, (1 О)

Е у = 4-res доп. где: 111 — значение двух младших pasрядов F „.

Иэ приведенных соотношений ясно, что для выполнения преобразования достаточно к входной характеристике прибавить у и результат разделить на четыре и на соответствующее число раз-1 рядов сдвинуть мантиссу. Число у является дополнительным кодом двух младших разрядов входной характеристики.

Преобразователь работает следующим образом.

1418909

При подключении входного кода на вхопы ствойства и подаче сигнала

"Разрешение приема" по входу 10 (фиг.l) осуществляется запись разрядов 1-8 характеристики в разряды 2-9 счетчика порядка, в разряд 1 счетчика 1 порядка при этом записывается ноль.

Нулевой разряд (знак числа) и разряды

9-31 мантиссы записываются соответственно в триггер 3 знака и в 24-разрядный блок 2 сдвига.

Одновременно сигнал с выхода элемента ИЛИ-HE 5 устанавливает в соответствующее состояние триггер неявно". го старшего (восьмого) разряда блока 2 сдвига. Если мантисса положительна и характеристика ненулевая, то триггер неявного старшего (восьмого) разряда устанавливается в единичное состояние ° Если же характеристика равна нулю, а также если мантисса отрицательна, то триггер неявного старшего (восьмого) разряда устанавливается в нулевое состояние.

Сигнал "Разрешение приема", поступающий также в блок 9 управления по четвертому входу устанавливает триггер 20 в единичное состояние, который,подготавливает блок 9 управления к работе и выдает по третьему выходу сигнал Занято" на выход 12 преобразователя, предупреждая источник входной информации о занятости устройства.

Знак мантиссы по выходу совпадает со знаком входного числа, поэтому однозначно передается с прямого выхода триггера 3 знака мантиссы на выход.

В счетчик 1 порядка добавляются от одной до трех единиц с одновременным сдвигом вправо (уменьшением) мантиссы, которая становится денормалиSOBBHHOA.

Значения восьмого и девятого разрядов с выхода счетчика l порядка по даются соответственно на первыч и второй входы блока 9 управления (фиг.2).,Ненулевое состояние этих разрядов через элемент ИЛИ 17 и через элемент И 21 дает разрешение на первый выход блока 9 управления для добавления единиц в счетчике 1 порядка и сдвигов (без знака) блока 2 сдвига, которые осуществляются под воздействием тактовых импульсов по входу 11 до тех пор, пока восьмой и девятый разряды счетчика 1 порядка не станут равными нулю. количествоноэ5

3S

40 можных добавлений единиц с одновременными сдвигами равно 0-3. При сдвигах мантиссы вправо в случае нуленого состояния триггера 3 знака мантиссы (фиг.l) на вход старшего (нось. мого) разряда мантиссы поступают нули, а в случае единичного состояния триггера 3 знака мантиссы — единицы.

После того как восьмой и девятый разряды счетчика 1 порядка станут равными нулю, снимается разрешающий сигнал с выхода элемента ИЛИ 17 и соответственно с первого ныхода блока 9 управления, и появляется сигнал на выходе элемента НЕ 18, который поступает на входы элементов И 22 и

23, подготавливая блок 9 управления для дальнейшей работы.

Если восьмой и девятый разряды счетчика 1 порядка сразу оказались равными нулю, то добанление единиц в счетчик 1 порядка и сдвиги вправо регистра мантиссы не производятся.

Диапазон изменения характеристики входного числа соотнетствует изменению характеристики выходного числа и пределах; 0100000 — Ullllll для отрицательных и 1000000 — 1011111 для по" ложительных порядков.

Пределы 0000000 — 0011111 для отрицательных и !l00000 — lllllll для положительных порядков при этом не используются. Поэтому второй разряд характеристики выходного числа всегда является инверсией первого разряда характеристики выходного числа„ кроме случая переполнения счетчика

1 порядка, когда характеристика нходного числа имеет одно из следующих значений: 1111101, 1111110 1111111.

3 этом случае на выходе преобразователя характеристика имеет значение

1100000.

Таким образом, разряди 3-7 счетчи. ка 1 порядка поступают прямо на выходы 3-7 преобразователя. Сигнал с прямого выхода второго разряда счетчика 1 порядка через элемент ИЛИ 6 поступает на первый выход преобраэо вателя, а сигнал с его инверсного выхода поступает через элемент ИЛИ 7 на второй выход характеристики преобразователя, Выход переполнения счетчика I порядка через элементы ИЛИ 6 и 7 выдачи соответственно первого и второго разрядов характеристики подается соответственно на первый и нто1418909

10

55 рой выходы характеристики преобразо. вателя.

Отрицательная мантисса в дополнительном коде во входном формате должна быть представлена в выходном формате в прямом коде со знаковым разрядом, равным единице, поэтому после денормализации числа блоком 9 управ-< ления осуществляется проверка знака нходного числа, записанного в его триггере 19. Если мантисса отрицательна, то единичный выход триггера

19 открывает элемент И 22, выдавая на второй выход разрешающий сигнал для вычитания единицы из содержимого блока 2 сдвига. Следующим же тактовым импульсом триггер 19 сбрасывается в нулевое состояние, разрешая через элемент И 23 подачу сигнала "Разрешение выдачи" по четвертому выходу блока 9 управления на выход 14 преобразова.теля °

Триггер 3 знака мантиссы управляет коммутатором 8 мантиссы, коммутируя на выход прямой код положительного числа или прямой код отрицательного числа блока 2 сднига. При положительном знаке на выход поступает прямой код положительного числа, при отрицательном - прямой код отрицательного числа.

После того как выходной код будет принят приемником информации,иэ него должен поступить сигнал "Принято" по входу 13, который сбрасывает триггер

20 н нулевое состояние, снимает сигнал "Занято" по выходу 12, после чего устройство готово к приему нового числа.

Пример l. Результаты преобразования форматов данных приведены в табл. 1.

Пример 2. Результаты преобразования форматов данных приведены в табл. 2.

Преобразование 16 и 64-раэрядйых форматов данных осуществляется аналогично, при этом разрядность блока

2 сдвига и коммутатора 8 мантиссы должна быть уменьшена или увеличена на соответствующее число разрядов.

Формула изобретения

Преобразователь форматов данных, содержащий счетчик порядка, блок сдвига, триггер знака мантиссы, коммутатор мантиссы и блок управления, тактовый вход которого соединен с тактовыми входами счетчика порядка и блока сдвига и с тактовым входом преобразователя, входы мантиссы которого соединены с информационными входами

Ь блока сдвига; выходы всех, кроме младшего, разрядов которого соединены с разрядными входами коммутатора мантиссы, выходы которого являются выходами мантиссы преобразователя, нход разрешения приема счетчика порядка соединен с входом разрешения приема блока управления и является входом разрешения приема преобразователя, выход знака которого соединен с перным управляющим .входом коммутатора мантиссы и с прямым выходом триггера знака мантиссы, инверсный выход которого соединен с вторым урравляющим входом коммутатора мантиссы, вход триггера знака мантиссы соединен с входом

25) знака преобразователя и с входом знака блока управления, выходы сдвига и инкремента которого соединены соответственно с входами сдвига. и инкремента блока сдвига, выходы заня тости и разрешения выдачи блока управления являются соответственно выходами занятости и разрешения выдачи преобразователя, нход окончания приема которого соединен с входом окончания приема блока управления, о т— л и ч а ю ш и и с я тем, что, с целью расширения класса решаемых задач за счет преобразования данных в формат с шестнадцатиричным основанием, в него введены элемент ИЛИ-НЕ, перный и второй элементы HJIH и дешифратор нулевой характеристики, входы которого соединены с входами характеристики преобразователя и соответственно с входами счетчика порядка, выходы двух младших разрядов которого соответственно соединены с первым и вторым входами денормализации блока управления, выход сдвига которого соединен с входом инкремента счетчика порядка, прямые выходы двух старших разрядов которого соединены с входами первого элемента ИЛИ, нхРды второго элемента ИЛИ соединены с прямым выходом старшего и инверсным выходом предстаршего разряда счетчика порядка, выходы первого и второго элементов ИЛИ совместно с выходами счетчика порядка, кроме выходов двух

14189

Таблица I исло

Показа- Знак Характетели чис" ристика ла

Мантисса

Исходный код

0 1 001 1 101 1 01 0000 0000 0000 0000 0000 1 3

Прием на регистр мантиссы и счетчик порядка 0

010011101 1101 0000 0000 0000 0000 OUOO

После денормализации 0

010100000 0001 1010 0000 0000 0000 0000

Выходной код 0

1001000 000! 1010 0000 0000 0000 0000 13 g

128

Таблица 2

Число

Характеристика

Знак

Показатели

Мантисса числа

Исходный код

1 01100011 011 0000 0000 0000 0000 0000 -13

Прием на регистр мантиссы и счетчик порядка 1

001100011 0011 0000 0000 0000 0000 0000

После денормализации 1

001100000 1001 1000 0000 0000 0000 0000

После вычитания единицы 1

1 111 1111 1111

001100!00 1001 0111 llll

Выходной код

1 0111001 0110 1000 0000 0000 0000 0000 13 -7

32 старших и двух младших разрядов, являются выходами характеристики преобраэователя, вход знака которого соединен с первым входом элемента ИЛИ-НЕ, 5 второй вход которого соединен с выходом дешифратора нулевой характеристики, а выход элемента ИЛИ-НЕ соединен с информационным входом старшего раэ09 8 ряда блока сдвига, входы последовательного прямого и обратного кодов которого соединены соответственно с прямым и инверсным выходами триггера знака, выход младшего разряда блока сдвига соединен с входом младшего разряда коммутатора мантиссы, 1418909

Фиа 2

Составитель M.Aðøàâñêèé

Редактор С.Патрушева Техред M.Ìoðãåíòàë Корректор А.Тяско

Закаа 4167/56

Тирам 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035, Москва Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул, Проектная, 4