Устройство для кодирования и декодирования информации

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСГ1УБЛИН (51)4 Н 03 М 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР пО делАм изОБРетений и ОтнРытий (21) 4180665/24-24 (22) 12.0!.87 (46) 23.08.88. Бюл. У 31 (72) А.Л. Вяткин и Г.Б. Галикеев (53) 621.398(088.8) (56) Авторское свидетельство СССР

Ф 758514, кл. Н 03 М 13/00, 1978.

Патент ФРГ Ф 2759106, кл. Н 03 К !3/24, 1977. (54) УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ И

ДЕ КОДИРОВАНИЯ ИНФОРМАЦИИ (57) Изобретение относится к радиотехнике, электросвязи и может использоваться в системах передачи цифровой

„SU, 418913 А1 информации для кодирования и декодирования информации цилиндрическими

БЧХ-кодами. Изобретение позволяет повысить быстродействие устройства. Декодируемое сообщение поступает в блок

1 ввода-вывода на вход последовательно-параллельного интерфейса 2, декодируется по алгоритму, заложенному в микроЭВМ 3, с помощью блоков 5,7 постоянной памяти, сумматоров 6, 8 по модулю два и поступает на выход параллельного интерфейса 4. Кодирова ние сообщения осуществляется в обратном порядке. 5 ил.

141891 3

Изобретение относится к радиотехнике, электросвязи и может использовать ся в системах передачи цифровой информации с кодированием цикличес5 кими кодами БЧХ.

Цель изобретения — повышение быстродействия устройства.

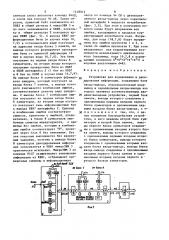

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 функциональная схема последовательнопараллельного интерфейса, микроЭВМ и параллельного интерфейса; на фиг.3— блок-схема алгоритма работы микроЭВМ в режиме кодирования; на фиг. 4 — f5 временная диаграмма работы устройства в режиме кодирования; на фиг. 5 блок-схема алгоритма работы микроЭВМ в режиме декодирования.

Устройство для кодирования и деко-2О дирования информации содержит (фиг.1) блок 1 ввода-вывода, выполненный на последовательно-параллельном интерфейсе 2 типа "Электроника С5-2102", микроЭВМ 3 типа "Электроника С5-21М" 25 и параллельном интерфейсе 4 типа

"Электроника С5-2102", первый блок 5 постоянной памяти, первый блок 6 сумматоров по модулю два, второй блок 7 постоянной памяти и второй блок 8 сумматоров по модулю два.

МикроЭВМ 3 имеет два межмодульных шестнадцатиразрядных параллельных интерфейса МПИ! и МПИ2, предназначен- ные для подключения микроЭВМ к внешним магистралям и устройствам (фиг.2).

Внешняя магистраль, подключенная к МПИI микроЭВМ 3, называется Ml.

Внешняя магистраль, подключенная к

МПИ2 микроЭВМ 3, называется М2.

Первый двунаправленный вход-выход микроЭВМ 3 сформирован межмодульным параллельным интерфейсом МПИI, соединяющимся через разъем XTI с внешней магистралвю МП, к которой подсоединяется двунаправленный вход-выход последовательно-параллельного интерфейса 2. Интерфейс 2 содержит 12 каналов ввода-вывода параллельной 8-разрядной информации, каждый канал связан с общей внешней магистралью (в зависимости от схемы включения Мl или М2)через разъем ХТI.

Модуль "Элекчроника С5-2102" имеет шесть 8-разрядных последовательньм каналов, каждый из которых может работать в режимах преобразования последовательного кода в паралЛельный и параллельного в последовательный.

Вход последовательной информации осуществляется по одному нз каналов через контакт Б18 разъема ХТ4, а вывод информации, преобразованной в параллельную, через двунаправленный вход-выход, выходящий на контакты

А2З-А29, А19, А21, Б19, Б29, Б24, Б25, Б28-БЗО разъема XTI на магистраль Ml.

Параллельная информация, предназначенная для передачи по последовательному каналу, поступает с магистрали Ml через те же контакты разъема

ХТI двунаправленного входа-выхода модуля "Электроника С5-2102", преобразуется в последовательный код и с контакта Б4 разъема ХТЗ поступает в линию связи.

Связь параллельно-последовательного интерфейса 2 по параллельному каналу с блоком 5 памяти и блоками 6 и 8 сумматоров по модулю два осуществляется через два восьмиразрядных канала ввода-вывода КВВ7 н КВВ8.

Второй двунаправленный вход-выход микроЭВМ "Электроника С5-21М" сформирован межмодульным параллельным интерфейсом МПИ2, соединяющимся через разъем ХТ2 с внешней магистралью

М2 (фиг.2).

К внешней магистрали М2 подсоединяется двунаправленный вход-выход параллельного интерфейса 4. Через разьем ХТI второй модуль "Электроника

С5-2102" связан с магистралью М2 (фиг. 2 ). Через контакты А2З-А29, А19, А21, Б19, Б22, Б24, Б25, Б28БЗО разъема XTI интерфейс 4 получает информацию с магистрали М2 от микроЭВМ З.и через эти же контакты выдает ее на магистраль М2 в микроЭВМ 3.

Внешним потребителям интерфейс 4 выдает информацию по одному из 12 каналов через контакты А29, Б27, А26, Б25, А24, А20, Б27 разъема ХТ4 в параллельном виде, и через эти же контакты получает ее от внешних устройств.

В структуру самой микроЭВМ включена также единая внутренняя магистраль МО, к которой подключены все устройства, располо*енные на плате микроЭВМ "Электроника Ñ5-21М".

В состав платы микроЭВМ "Электроника С5-21M" входят микросхемы цнфро вого ввода-вывода, позволяющие пользователю включать микроЭВМ в устрой1418913 4 ство для кодирования и декодирования информации (фиг. 2) .

Эти микросхемы связаны с единой внутренней магистралью MO. Микросхемы цифрового ввода-вывода содержат четыре канала ввода-вывода: КВВ1, КВВ2, КВВ3, КВВ4. Ввод-вывод информации параллельный, восьмибитовый.

Устройство работает следующим образом.

Для примера рассмотрим циклический код БЧХ (16,7,6). Этот код содержит

7 информационных и 9 проверочных символов. В режиме кодирования семиразрядный информационный набор символов в параллельном коде поступает на вход интерфейса 4 и записывается в его программно-доступный регистр KBBl.

МикроЭВМ 3 анализирует поступление информации по сигналу сопровождения от источника информации и считывает данные из программно-доступного регистра KBBl интерфейса 4 со стиранием, подготавливая КВВ1 интерфейса 4 для приема следующего информационного набора (фиг. 3). Команды считывания иэ KBBl интерфейса 4 и записи н КВВ7 интерфейса 2 — это дне команды, которые интерпретируются следующим образом: считать данные из ячейки памяти (регистр KBBl интерфейса 4) по адресу В и занести н общий регистр Л84АВ, вторая команда 94АС вЂ” занести из общего регистра А в ячейку памяти по адресу С, где адрес С вЂ” адрес программно-доступного регистра КВВ7 интерфейса 2.

После записи семи бит информации н КВВ7 интерфейса 2 информация потенциальными уровнями с выхода КВВ7 поступает на адресный вход блока 5 памяти и на его выходах образуются проверочные символы кода, которые записываются в регистры КВВЗ и КВВ4 микроЭВМ 3. Следующая команда 44А8 считать из КВВЗ и логически сложить с общим регистром А. После анализа сигнала "Байт передан" или "Нет" с помощью опроса по адресу регистра

КВВ4 интерфейса 2 командой 94А7 информация.иэ общего регистра А переписывается в КВВ5. При этом тактовые импульсы передачи считывают информацию из регистра последовательной связи

РСС, входящего в состав КВВ4 интерфейса 2. После передачи байта тактовые импульсы Ти/8 переписывают информацию из КВВ5 н PCC и одновременно

55 сигнал "Байт передан" записывается в

КВВ4 интерфейса 2. МикроЭВМ 3 анализирует содержимое КВВ4 интерфейса 2, после прихода сигнала "Байт передан" переписывает второй байт командами

84А5 и 94А7 иэ КВВ4 микроЭВМ 3 и КВВ5 интерфейса 2 и переходит на анализ состояния интерфейса 4, а передача нторого байта из регистра PCC осуществляется уже независимо от работы микроЭВМ 3. Скорость поступления данных н интерфейс 4 должна быть согласована со скоростью передачи по каналу. Причем поскольку устройство выполняет операцию кодирования почти мгновенно и микроЭВМ 3 не затрачивает значительного времени, то, если необходимо, чтобы информация передавалась беэ разрывов, одно кодовое слово за другим, частота поступления информации в интерфейс 4 должна быть равна Ти/16 (фиг. 4).

Время кодиронания занимает одну операцию обращения к ПЗУ, а в извест. ном устройстве 4 цикла обращения при

16-разрядном кодовом слове, следовательно, время кодирования сокращает" ся, что дает возможность достаточно просто вести передачу в последовательном (параллельном) коде.

В режиме декодирования с помощню последовательно-параллельного интерфейса 2 кодовое слово двоичного сист тематического кода (например, кода

16,7,6), переданаемого по линии связи, преобразуется в параллельный вид.

При этом вначале информация в после-, довательном виде поступает в PCC расположенный в KBBl интерфейса 2, импульсом Ти/8 она переписывается в регистр КВВ2 интерфейса 2, PCC освобождается для приема следующего байта. Импульс Ти/8 также записывается в КВВ1 интерфейса 2. Этот сигнал анализируется в цикле микроЭВМ 3. Деле" ние Ти и перепись из PCC в регистр

КВВ2 осуществляется стандартными anпаратными средствами модуля "Электроника С5-2102". МикроЭВМ 3 по команде 84АД считывает из КВВ2 интерфейса

2 данные во входной регистр А, который является одним из общих регистров микроЭВМ 3, а следующей командой

94АС переписывает из общего регистра

А данные в КВВ7 интерфейса 2 (фиг.5).

После этого микроЭВМ 3 анализирует сигнал "Байт принят" о приходе второго байта, и после прихода этого

5 141 сигнала снова выполняет команду 84АД, а после нее команду 94 АЕ. Таким образом, принятый байт считывается из

КВВ2 в общий регистр А микроЭВМ 3 и из него записывается в КВВ8, поскольку в общем регистре Е находится адрес КВВ8 (фиг. 5). С выхода КВВ7 информационные биты (в случае кода 16

7,6) в потенциальном виде поступают на адресные входы блока 5 памяти, на выходе которого формируются проверочные биты от принятой информации (9 бит в случае кода 16,7,6). Эти биты поступают на первые входы блока 6 сумматоров, на вторые входы которого поступают проверочные биты из КВВ7 и КВВ8 интерфейса 2 (1 бит из КВВ7 и 8 бит иэ КВВ8 в случае кода 16,7,6).

На выходе блока 6 сумматоров формируется синдром, который поступает на входы блока 7 памяти, с выхода кото» рого считывается комбинация ошибок, соответствующая данному виду синдрома. С выхода блока 7 комбинация ошибок поступает на первые входы блока

8 сумматоров, на вторые входы которого поступает семь информационных бит с выхода КВВ7 интерфейса 2. Единица в комбинации ошибок соответствует символу, принятому с ошибкой, следовательно, в блоке 8 сумматоров ошибочные символы инвертируются,, а примятые беэ ошибок, которым в комбинации ошибок соответствует "О", проходят через блок 8 без изменения . Все эти операции выполняются беэ временных задержек, поэтому с выхода блока

8 сумматоров декодированная информация записывается в КВВ1 микроЭВМ 3 практически мгновенно. МикроЭВМ 3 по команде 84СГ осуществляет считывание информации иэ КВВ1, отбрасывает проверочные символы и информационная

8913 6 часть по команде У4 СВ с двунаправленного входа-выхода через параллельный интерфейс 4 выдается потребителю

5 (фиг. 2,5). При этом в полученном кодовом слове будут исправлены все ошибки, находящиеся в пределах корректирующей способности кода. Например, для кода (16,7,6) будут исправлены все ошибки кратности 1 и 2, а также 24 ошибки кратности 3. При этом реализуются все корректирующие возможности используемого циклического кода (например, кода 16,7,6 с порождающим полиномом Х +Х +Х +Х +Х +l u кодовым расстоянием d6).

Формула и э о б р е т е н и я

Устройство для кодирования и декодирования информации, содержащее блок

I ввода-вывода, последовательный входвыход и параллельные входы-выходы кот торого являются соответственными вко25 дами-выходами устройства, первый блок памяти, выходы которого соединены с одноименными первыми входами первого блока сумматоров и одноименными первыми входами блока ввода-вывода, о т3р л и ч а ю щ е е с я тем, что, с целью повьппения быстродействия устройства, в него введены второй блок сумматоров и второй блок памяти, выходы первого блока сумматоров соединены с одноименными входами второго блока памяти, выходы которого соединены с одноименными первыми входами второго блока сумматоров, выходы которого соединены с одноименными вторыми вхо4р дами блока ввода-вывода, выходы блока ввода-вывода соединены с одноименными входами первого блока памяти и одноименными вторыми входами первого и . второго блоков сумматоров.

I 4I 891 3

Моианпа necmynm ния.3аиньк 8 онмр уеас У

gpepy ррииро3а ая и храненм ю ййео слода д гюкро - ЭВМ 5

СтроЕ Ти!8

8рпи хранения 1и 2-ео Ьииюд о

ИВВ5 иняеррей са

Моменвы Мрем си Яцмо8 из EB

8 РГС дреме лежй- Вреилт Время

qg f-gy Ыяа реоочи ьере3ача

2-еа Йпйпа 1-ео оайла

Фиг.0

1418913

Составитель М. Никуленков

Редактор С. Патрушева Техред М.Моргентал Корректор. И. Эрдейи

Заказ 4167/56

Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4