Устройство для измерения достоверности передачи информации

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи . Цель изобретения - ласширение функциональных возможностей путем учета проскальзьшаний. Устр-во содержит г-р 1 тактовых импульсов, датчики 2 и 4 испытательных и эталонных сигналов, блок 3 тактовой синхронизации , блоки 5 и 6 задержки БЗ , блок 7 циклового фазирования (ВЦФ), блоки 8-11 контроля синхронизма, эл-т ИЛИ 12, блок 13 совпадения, счетчик 14 проскальзываний, блок 15 сравнения , счетчик 16 ошибок, блок 17 отображения и контролируемый ТГифровой канал 18 связи. Для обнаружения проскальзьгоаний БЗ 5 обеспечивает задержку принимаемого сигнала на три тактовых интервала, а БЗ 6 - задержку эталонного сигнала на пять тактов . При выпадении одного или двух двоичных символов цикловое фазирование обнаруживает блок 8 или 9 контроля , а при вставке этих символов - блок 10 или 11 контроля. При этом БЦФ 7 зарегистрирует сбой цикловой синхронизации и его управляющий сигнал поступает на блок 13 совпадения, на который подается также сигнал через эл-т ИЛИ 12 от одного из блоков В - П контроля, зарегистрировавших проскальзьшание двоичных символов . Появление сигнала на выходе блока 13 совпадения указьгоает на то, что произошло проскальзьшание и количество этих событий регистрируется счетчиком 14. 1 ил. С/)

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ÄÄSUÄÄ 1418919 А1 (51) 4 Н 04 В 3/46

» .»

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPGHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4226370/24-09 (22) 02.03.87 (46) 23.08.88.Бюл. У 31 (72) В.С.Иванцовский, И.Д.Линник и А.С.Родин (53) 621 .395 .664 (088 .8) (56) Авторское свидетельство СССР

11» 422111,кл. Н 04 В 3/46, 1972.

Авторское свидетельство СССР

У 1113892, кл. Н 04 В 3/46, 1982. (54) УСТРОЙСТВО ДЛЯ ИЗ11ЕРЕНИЯ ДОСТОВЕРНОСТИ ПЕРЕДАЧИ ИНФОРМАЦИИ (57) Изобретение относится к электросвязи. Цель изобретения — расширение функциональных воэможностей путем учета проскальзываний. устр-во содержит г-р 1 тактовых импульсов, датчики 2 и 4 испытательных и эталонных сигналов, блок 3 тактовой синхронизации, блоки 5 и 6 задержки БЗ, блок

7 циклового фазирования (БЦФ ), блоки

8-11 контроля синхрониэма, эл-т

ИЛИ 12, блок 13 совпадения, счетчик

14 проскальзываний» блок 15 сравнения, счетчик 16 ошибок, блок 17 отображения и контролируемый цифровой канал 18 связи. Для обнаружения проскальзываний БЗ 5 обеспечивает задержку принимаемого сигнала на три тактовых интервала, а БЗ 6 - задержку эталонного сигнала на пять тактов. При выпадении одного или двух двоичных символов цикловое фазирование обнаруживает блок 8 или 9 контроля, а при вставке этих символов блок 10 или 11 контроля. При этом

БЦФ 7 зарегистрирует сбой цикловой синхронизации и его управлякпций сигнал поступает на блок 13 совпадения, на который подается также сигнал череэ эл-т ИЛИ 12 от одного из блоков 8 — 11 контроля, зарегистрировавших проскальзывание двоичных символов. Появление сигнала на выходе блока 13 совпадения указывает на то, И что произошло проскальзывание и количество этих событий регистрируется счетчиком 14. 1 ил.

1418919

Изобретение относится к электросвязи и может использоваться для контроля состояния аппаратуры и каналов передачи дискретной информации в про5 цессе настройки, испытаний и эксплуатации.

Цель из об ре тения — расширение функциональных возможностей путем учета проскальзываний °

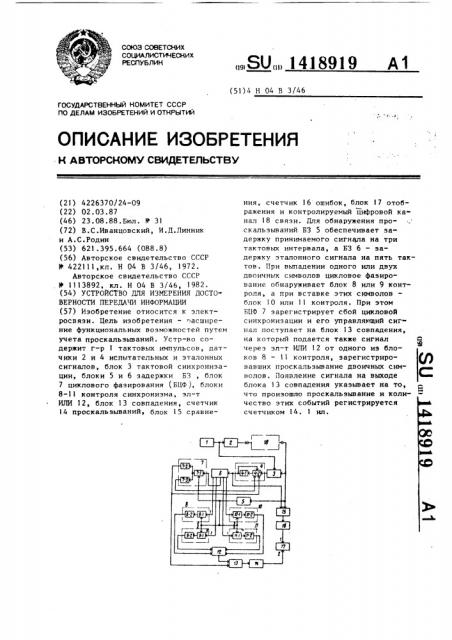

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Устройство для измерения достоверности передачи информации содержит генератор 1 тактовых импульсов, датчик 2 испытательных сигналов, блок 3 тактовой синхронизации, датчик 4 эталонных сигналов, состоящий из регистра 4-1 и блока 4-2 управления, пер- 20 вый 5 и второй 6 блоки задержки, блок 7 циклового фазироввния, состоящий иэ анализатора 7-1 ошибок, анализатора 7-2 сбоя фазы и анализатора 7-3 синфазности, первый 8, вто- 25 рой 9, третий IO и четвертый 11 блоки контроля синхронизма, каждый иэ которых состоит из анализатора 8-1, 9-1, 10-1. и 11-1 ошибок и анализатора 8-2, 9-2, 1 0-2 и 1 1-2 синфазнос- 30 ти соответственно, элемент ИЛИ 12, блок 13 совпадения, счетчик 14 проскальзываний, блок 15 сравнения, счет" чик 16 ошибок! блок 17 отображения и

35 контролируемый цифровой канал 18 свяУстройство работает следующим образом.

От датчика 2 испытательных сигналов поступает двоичная последователь- 0 ность в контролируемый цифровой канал 18, откуда испытательная последовательность сигналов поступает на вход блока 3 тактовой синхронизации, а также на вход первого блока 5 sa- 45 держки и на блок 15 сравнения.

Блок 3 тактовой синхронизации осуществляет подстройку тактовой частоты, поступающей от местного генератора тактовых импульсов, по передним фронтам двоичных сигналов из канала

18.

Датчик 4 эталонных сигналов вырабатывает такую же последовательность двоичных сигналов, как и датчик 2.

Фазирование по циклу датчиков 2 и 4

55 осуществляется по сигналам управления, поступающим с блока 7 циклового фазиронания на блок 4-2 управления.

По сигналу управления !Сбой фазы" ! поступающемУ с анализатоРа 7-2 блок

4-2 управления подключает на вход приемной рекурренты регистра 4-1 информацию, получаемую иэ канала 18.

После правильного заполнения приемной рекурренты информацией анализатор 7-3 синфаэности выдает на блок

4-2 управления сигнал,по которому рекуррентный регистр 4-1 замыкается !! !! на себя, после чего датчик 4 начинает работать автономно.

Эталонная испытательная последовательность поступает на второй вход блока 15 сравнения и на второй блок

6 задержки. В блоке 15 сравнения принятая из канала 18 испытательная последовательность сравнивается поэлементно с эталонной испытательной последовательностью. При несовпадении элементов последовательностей нв выходе блока 15 сравнения появляются импульсы ошибки, которые регистрируются счетчиком 16 ошибок.

Для обнаружения проскальзываний первый блок 5 задержки обеспечивает задержку принимаемого сигнала на три тактовых интервала! а второй блок 6 задержки — задержку эталонного сигнала 1,2,3,4 и 5 тактов.

Блок 7 циклового фазирования обеспечивает анализ установления синфаэности и анализ сбоя цикловой синхронизации по сигналам, задержанным на три такта.

При выпадении одного или двух двоичных символов обнаруживает цикловое фазироввние первый 8 или второй

9 блок контроля синхрониэма, а при вставке одного или двух символов третий 10 или четвертый 11 блок контроля синхронизма. При этом блок 7 циклового фаэирования регистрирует сбой цикловой синхронизации и управляющий сигнал с выхода анализатора

7-2 поступает на блок 13 совпадения, на второй вход которого поступает сигнал через элемент ИЛИ 12 от одного из блоков 8-11 контроля синхрониэма, зарегистрировавших проскальзывание двоичных символов.

Появление сигнала на выходе блока

13 совпадения указывает на то, что произошло проскальзывание, и количество этих событий регистрируется счетчиком 14, 18919

Составитель В.Слепаков

Редактор П.Гереши Техред М.Моргентал Корректор А.Тяско

Заказ 4167/56 Тираж 660 Подписное

ВНИИПИ Государственного комитета СССР по делам изобрегений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 з 14 формула изобретения

Устройство для измерения достоверности передачи информации, содержащее блок циклового фазирования, счетчик ошибок, блок отображения и последовательно соединенные генератор тактовых импульсов и датчик испытательных сигналов, выход которого подключен к входу контролируемого цифрового канала связи, выход которого через последовательно соединенные блок тактовой синхронизации, второй вход которого соединен с выходом генератора тактовых импульсов, и датчик эталонных сигналов, второй вход которого соединен с первым выходом блока циклового фаэирования, подключен к первому входу блока сравнения, второй вход которого соединен с первым входом блока тактовой синхронизации, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных воэможностей путем учета проскальзываний, введены первый и второй блоки задержки, первый, второй, третий и четвертый блоки контроля синхронизма и последовательно соединенные элемент ИЛИ, блок совпадения и счетчик проскальзываний, при этом выход датчика эталонных сигналов подключен к входу второго блока задержки, первый, второй, третий, четвертый и пятый выходы которого подключены к первым входам соответственно первого и второго блоков контроля синхронизма, блока циклового фазирования и с ъ третьего и четвертого блоков контроля синхронизма, второй вход блока сравнения соединен с входом первого блока задержки, выход которого под15 ключен к вторым входам первого, второго третьего и четвертого блоков контроля синхронизма и блока циклового фазирования, второй выход которого подключен к третьему входу датgp чика эталонных сигналов и к второму входу блока совпадения, выходы первого, второго, третьего и четвертого блоков контроля синхрониэма.подключены к соответствующим входам

25 элемента ИЛИ, а выход блока сравнения через счетчик ошибок" подключен к первому входу блока отображения, второй вход которого соединен с выходом счетчика проскальзываний.