Параллельный счетчик по модулю @ -дешифратор количества единиц в @ -разрядном двоичном коде

Иллюстрации

Показать всеРеферат

Изобретение, может быть использовано в процессах цифровой обработки сигналов.. Цель изобретения - расширение функциональных возможностей устройства. Счетчик содержит блок 1 упорядочивания единиц, логические ячейки 2, элемент И 3 и элементИЖ4. Введение группы 5 и 7 ключей 6, преобразователей 8 и 9 кодов, регистра 10 и образование новых функциональных связей обеспечивает возможность суммирования по модулю m с накоплением и представлением результата в по.- зиционном единичном коде. 3 ил. иг I S с сл

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU, 1420666 А.1 (дд 4 Н 03 К 23/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ. СР»"..» Н4"., РАЯ

Н ASTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4039841/24-21 (22) 17.03.86 (46) 30.08.88. Вюл. N 32 (72) В,В .Храмов, Г.И.Васильев, А.В.Лярский и Л.M.Íèêèòèíà (53) 621.394 (088.8) (56) Авторское свидетельство СССР

М 892715, кл. Н 03 К 13/24, 1979.

Патент Великобритании 1479596, кл. G 4 А, 1976. (54) ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ПО МОДУЛЮ ш — ДЕШИФРАТОР КОЛИЧЕСТВА ЕДИНИЦ В и-РАЗРЯДНОМ ДВОИЧНОМ КОДЕ (57) Изобретение может быть использовано в процессах цифровой обработки сигналов. Цель изобретения — расширение функциональных возможностей устройства . Счетчик содержит блок 1 упорядочивания единиц, логические ячейки 2, элемент И 3 и элемент ИЛИ 4.

Введение группы 5 и 7 ключей 6, преобразователей 8 и 9 кодов, регистра

10 и образование новых функциональных связей обеспечивает возможность суммирования по модулю ш с накоплением и представлением результата в позиционном единичном коде. 3 ил.

1420666

Изо бре тен ие о тно сит ся к им пуль сной технике и может быть использовано в процессорах цифровой обработки сигн алов .

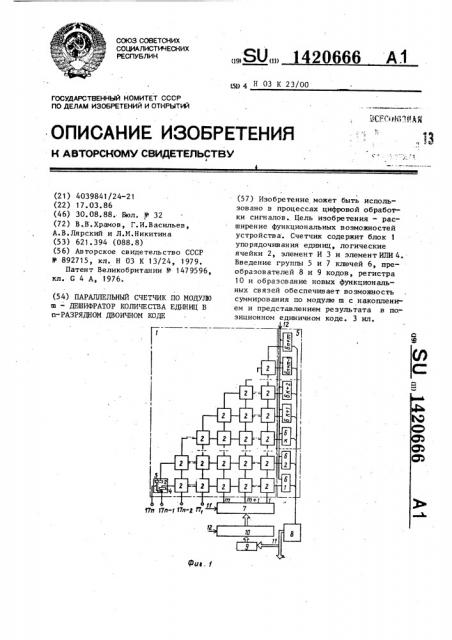

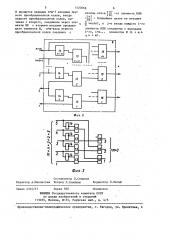

Цель изобретения — расширение функциональных возможностей в области применения устрой ств а путем обе спечения возможности суммирования по модулю m с накоплением и представлением результата в позиционном единичном коде. На фиг. 1 изображена блок-схема устройства; на фиг.2 — пример выполнения первого преобразователя кодов в общем случае; на фиг.3 - то же, для случая m = 3, п = 2.

Параллельный счетчик по модулю ш — дешифратор количества единиц в

Il-ðà3рядном двоичном коде (фиг.1) 2р содержит блок 1 упорядочивания еди,ниц, имеющий в своем составе логические ячейки 2, которые расположены в виде треугольной матрицы размерностью (m+n-1) (и+ш-1), с нумерацией строк снизу вверх и столбцов— справа налево, каждая логическая ячейка имеет два входа и два выхода и содержит элемент И 3 и элемент

ИЛИ 4, первые и вторые входы которых :30 являются соответственно первым и вто- рым входами логической ячейки, выход элемента И является первым выходом логической ячейки, а выход элемента ИЛИ вЂ” вторым ее выходом. Вторые входи всех логических ячеек первой строки и первый вход последней логиче ской яче йки первой строки являют ся входами блока 1 упорядочивания единиц, вторые .выходы первых логических

40 ячеек всех строк и первый выход логической ячейки последней строки являются выходами блока упорядочивания единиц; второй выход каждой последующей ячейки каждой строки соединен с

45 первым входом предыдущей ячейки тои же строки, первый выход каждой i-й логической ячейки, кроме последней в данной строке, соединен с вторым вхо. дом i-й логической ячейки последующей строки, выход последней логичес- 50 кой ячейки каждой предыдущей строки соединен с первым входом последней логической ячейки последующей строки.

Устройство содержит также первую группу 5 ключей 6 и вторую группу 7 клю- 55 чей, первый 8 и второй 9 преобразователи кодов, регистр 10, информационные входы регистра 10 подключены к соответствующим выходам второго преобразователя 9 кодов, а выходы соединены с информационными входами второй группы 7 ключей, управляющие входы которых подключены к первому управляющему входу 11 устройства, а выходы — к соответствующим первым ш входам блока 1 упорядочивания единиц, и остальных входов которого являются информационными входами устройства.

Выходы блока 1 упорядочивания единиц соединены с информационными входами первой группы 5 ключей 6, управляющие входы которых подключены к второму управляющему входу 12 устройства, а выходы соединены с соответствующими входами первого преобразователя 8 кода, выходы которого подключены к выходам устройства и соединены с соответствующими входами второго преобразователя 9 кодов.

Управляющий вход регистра 10 является третьим управляющим входом 12 устройства.

Первый преобразователь 8 кодов (фиг.2) имеет в своем составе n+m-1 элементов И 13, n+m-1 элементов

НЕ 14 и m элементов ИЛИ 15, выходы которых являются выходами первого преобразователя 8 кодов. Первые входы элементов И 13 являются первыми

n+m-1-входами первого преобразователя 8 кодов, входы которого, начиная с второго, соединены через элементы НЕ 14 с вторыми входами соответствующих предыдущих элементов И, n+m-вход первого преобразователя кодов соединен с входом п + ш nГ 1nà — m — -го элемента ИЛИ () — (— бли)ш ( жайшее целое, не меньшее ш число), а

j-входы каждого i-ro элемента ИЛИ 15 соединены с выходами i-го, i+m-го элементов И 13 (i+m n+m).

Устройство работает следующим образом.

Перед н ач алом р або ты н а вход "Установка 0" регистра подается импульс и в регистре 10 результата устанавливается нулевое значение. Затем на информационные входы устройства подается анализируемый код. Пусть в этом коде имеется r единиц. Через время, равное (n+m) времени: задержки элементов И, ИЛИ блока 1 упорядочивания единиц, на информационных входах первой группы 5 ключей 6 с номерами от 1 до . r появляются по1420666 тенциалы, соответствующие логической 1. После этого на вход 12 подается управляющий сигнал, разрешающий выдачу информации в первый преобразователь 8 кодов, в котором определяется граница между массивом единиц и массивом нулей, т.е. если на входы блока 8 поступило r единиц, то с выходов элементов ИЛИ 15 снимается 10 только одна логическая единица.

Таким образом, сумма единиц представлена единичным, позиционным кодом (дешифрирована) и может быть использована для дальнейшего вычислительного процесса. Одновременно с выдачей информации во внешние цепи полученная сумма записывается в регистр 10, пройдя преобразование во втором преобразователе 9 кода (тем. самым осуществляется преобразование единичного позиционного кода суммы в двоичное число, количество единиц в котором равно сумме количества единиц исходных чисел). Второй и последующие циклы отличаются от первого только тем, что во втором и последующем перед началом циклах по дается управляющий сигнал на вход 11 второй группы 7 ключей для.осуществления суммирования накопленной суммы единиц по модулю m и нового значения входного кода.

Введение новых элементов и связей позволяет расширить функциональные возможности устройства — осуществлять накопление информации о входном контролируемом коде, получить результат суммирования по модулю m в единичном позиционном коде, удобном для 40 применения в управляющих устройствах.

Формула изобретения

Параллельный. счетчик по модулю ш — дешифратор количества единиц в и-разрядном двоичном коде, содержащий блок упорядочивания единиц и имеющий в своем составе конические ячейки, которые расположены в виде треугольной матрицы размерностью (m+n-1) (и+ш-1), с нумерацией строк . снизу вверх и столбцов справа налево, каждая логическая ячейка имеет два входа и два выхода и содержит элемент ИЛИ, первые и вторые входы кото- 55 рых являются .соответственно первым и вторым входами логической ячейки, выход элемента И является первым выходом логической ячейки, а выход элемента ИЛИ является вторым выходом логической ячейки, вторые входы всех логических ячеек первой строки и первый вход последней логической ячейки первой строки являются входа— ми блока упорядочивания единиц, вторые выходы первых логических ячеек всех строк и первый выход логической ячейки последней строки являются выходами блока упорядочивания единиц, второй выход каждой последующей логической ячейки каждой строки соединен с первым входом предыдущей логической ячейки той же строки, первый выход каждой i-й логической ячейки, кроме последней в данной строке, соединен с вторым входом i-й логической ячейки последующей строки, первый выход последней логической ячейки каждой предыдущей строки соединен с первым входом последней логической ячейки последующей строки, отличающийся тем, что, с целью расширения функциональных возможностей, в устройство введены первая и вторая группы ключей, первый и второй преобразователи кодов и регистр, информационные входы которого подключены к соответствующим выходам второго преобразователя кодов, а выходы соединены с информационными входами второй группы ключей, управляющие входы которых подключены к первому управляющему входу устройства, а выходы — к соответствующим первым m входам блока упорядочивания единиц, и остальных входов которого являются информационными входами устройства, выходы блока упорядочивания единиц соединены с информационными входами первой группы ключей, управляющие входы которых подключены к второму управляющему входу устройства, а выходы соединены с соответствующими входами первого преобразователя кода, выходы которо го подключены к выходам устройства и соединены с соответствующими входами в торо ro пре о б разов ателя кодов, управляющий вход регистра является третьим управляющим входом устройства, причем первый преобразователь кодов имеет в своем составе n+m-1 элементов И, n+m-1 элементов НЕ и ш элементов ИЛИ, выходы которых являются выходами первого преобразователя кодов, первые входы элементов

1420666 6 nã входом n+m-m — -го элемента ИЛИ ! mL

1BГ () — — ближайшее целое не меньшее .1mL и — число), а j-e входы каждого i-ro элемента ИЛИ соединены с выходами

1-го, i+m... элементов И {i + m

c n + ш) ° И являются первыми n+m-1 входами первого преобразователя кодов, входы первого преобразователя кодов, начиная с второго, соединены через элементы НЕ с вторыми входами предыдущего элемента И, n+m-вход первого преобразователя кодов соединен с

ITP

Составитель П.Смирнов

Редактор А.Маковская Техред Л. 0лийнык Корректор. Л. Патай

Заказ 4334/57 Тираж 928 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4