Система для асинхронного сопряжения импульсных потоков

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи . Цель изобретения - улучшение использования пропускной способг ности канала связи. Система содержит на передающей стороне выделитель 1 тактовой частоты, временной детектор .2, блок динамической памяти (БДИ) 3, г-р 4 тактовых импульсов, логический блок 5, селектор 10 синхросигнала, блок управления (ВУ) 11 и делитель 12 частоты, а на приемной стороне приемник 6 синхросигнала, логический блок 7, блок фазовой автоподстройки 8 частоты , БДП 9, БУ 13 и делители 14 и ;15 частоты. Входной цифровой поток, -содержащий m бит, используемых для передачи циклового синхронизирующего сигнала, и п бит информационных, пос-- тупает на выделитель 1, к.оторый вьще-, ляет тактовую частоту, и на селектор 10, который входной цифровой поток задерж ивает на длительность синхронизирующей комбинации и передает его в БДП 3. Запись информации в БДП 3 осуществляется тактовой частотой вьвделителя 1, а считывание информации из БДП 3-станционной импульсной последовательностью г-ра 4. При этом на передающей стороне осуществляется введение дублирующей посыпки в пере-- даваемый сигнал, формируемый в БДП 3. Т.обр. на приемную сторону поступают сигнал с введенными в него дублирую-, щими посылками и сопровождающая его тактовая последовательность. После дешифрации квазипериодического синхросигнала и его задержки в приемнике 6 он поступает в БДП 9. При обнаружении циклов, в которые введены дублирующие посылки, эти посыпки не записьюаются в БДП 9. Считывание записанлой информации осуществляется восстановленной тактовой частотой. Цель достигаеглся введением селектора 10,БУ 11 и 13 и делителей 12, 14 и 15. Даны ил., выполнения БДП 3 и БУ 11 и 13. 4 ил. ... Ш (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (5114 Н 04 1 7 02 Н 04 J 3/06

ВСЕСОИ),"-.%А%

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCKOMY СВИДЕТЕЛЬСТВУ

1 с

1 !

Та пасу !

Фиг.f

ГОСУДАРСТВ ННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 4058689/24-09 (22) 23.04.86 (46) 30.08.88. Бюл. У 32 (72) А.Н.Журавлев, В.С.Ефремов, А.Л.Жеребцов и В.M.Mèíêèí (53) 621. 376.56 (088.8) (56), Левин Л.С. и др. Цифровые сис темы передачи информации. M.: "Связь", 1982, с.56-57 рис.3.2. (54) СИСТЕМА ДЛЯ АСИНХРОННОГО СОПРЯЖЕНИЯ ИМПУЛЬСНЫХ ПОТОКОВ (57) Изобретение относится к электросвязи. Цель изобретения — улучшение использования пропускной способ» ности канала связи. Система содержит на передающей стороне выделитель 1 тактовой частоты, временной детектор

2, блок динамической памяти (БДП) 3, r-p 4 тактовых импульсов, логи ческий блок 5, селектор 10 синхросигнала, блок управления (БУ) 11 и делитель 12 частоты, а на приемной стороне приемник 6 синхросигнала, логический блок

7, блок фазовой автоподстройки 8 частоты, БДП 9, БУ 13 и делители.14 и

15 частоты. Входной цифровой поток, содержащий m бит, используемых для передачи циклового синхронизирующего сигнала, и и бит информационных, пос-. тупает на выделитель 1, который выделяет тактовую частоту, и на селектор

10, который входной цифровой поток задерживает на длительность синхронизирующей комбинации и передает его в

БДП 3. Запись информации в БДП 3 осу" ществляется тактовой частотой выделителя 1, а считывание информации из

БДП 3-станционной импульсной последовательностью r-ра 4. При этом на передающей стороне осуществляется введение дублирующей посылки в пере": даваемый сигнал, формируемый в БДП 3, Т.обр. на приемную сторону поступают сигнал с введенными в него дублирую», щими посылками и сопровождающая его тактовая последовательность. После дешифрации квазипериодического синхросигнала и его задержки а приемнике б он поступает в БДП 9. При обнаружении циклов, в которые введены дублирующие Я посылки, эти посылки не записываются в БДП 9. Считывание записанной информации осуществляется восстановленной тактовой частотой. Цель достигаеася введением селектора 10, БУ 11 и 13 и делителей 12, 14 и 15. Даны ил.. выполнения БДП 3 и БУ 11 и 13. 4 ил.

1420670

Изобретение относится к электросвязи и может применяться на линиях связи и сетях, использующих цифровые системы передачи.

ЦелЬ изобретения — улучшение использования пропускной способности канала связи.

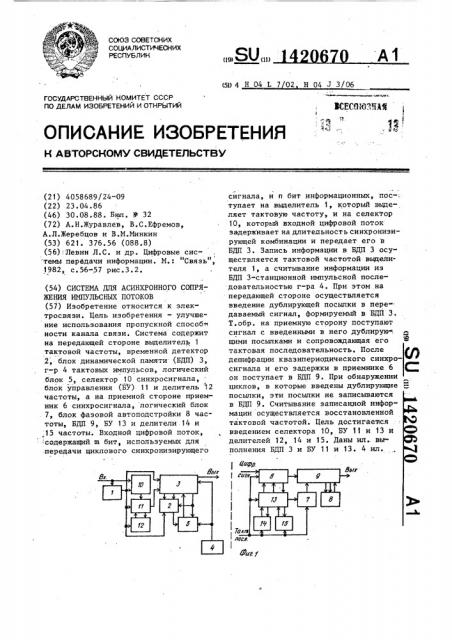

На фиг. 1 изображена структурная электрическая схема системы для асин- 10 хронного сопряжения импульсных потоков; на фиг.2 4 — примеры выполнения, соответственно, блока динамической памяти передающей стороны и блоков управления передающей и приемной сто-. 15 рон.

Система для асинхронного сопряжения импульсных потоков содержит на передающей стороне выделитель 1 тактовой частоты, временной детектор 2, блок 3 динамической памяти, генератор 4 тактовых импульсов и логический блок 5, а на приемной стороне — приемник 6 синхросигнала, логический блок 7, блок 8 фазовой автоподстройки25 частоты и блок 9 динамической памяти, а также содержит на передающей стороне селектор 10 синхросигнала, блок 11 .управления и делитель 12 частоты, а на приемной стороне - блок 13 управле" ния, первый и второй делители 14 и 15 частоты.

Блок 3 динамической памяти передающей стороны, изображенный на фиг.2, содержит первый элемент 16 И, первый регистр 17 сдвига, второй регистр 18 сдвига, второй элемент 19 И, .третий регистр 20 сдвига, первый и второй элементы 21 и 22 ИЛИ и первые и вторые ячейки 23 и 24 памяти, каждая иэ которых состоит из элемента 25 памяти

40 и элемента 26 И.

Блок 11 управления передающей стороны, изображенный на фиг.3 содержит первый и второй элементы 27 и 28 И, первый и второй регистры 29 и 30 сдвига и триггер 31.

Блок 13 управления приемной стороны, изображенный на фиг.4, содержит первый, второй и третий элементы 32, 33 и 34 И, накопитель 35 по входу в син- 50 хронизм, регистр 36 сдвига, коммутатор

37,триггер 38, первый и второй форми" рователи 39 и 40 сигнала и, элемент 41 запрета.

Система для асинхронного сопряжения импульсных потоков работает следующим образом.

Выделитель 1 тактовой частоты на передающей стороне из входного цифрового потока, содержащего w -бит, используемых для передачи циклового синхро,низирующего сигнала, и и информационных бит (составляющих в сумме один цикл), выделяет тактовую частоту, которая поступает на тактовые входы ряда блоков передающей стороны. Генератор 4 тактовых импульсов вырабатывает станционную импульсную последователь-. ность, частота которой незначительно превышает (с учетом возможных нестабильностей обоих частот) частоту, по-. лученную из входного цифрового пото" ка. На первом выходе селектора 10 синхросигнала всякий раз появляются отклики, когда во входном цифровом потоке появляется кодовая комбинация типа циклового синхронизирующего сигнала. Делитель 12 частоты, имеющий коэффициент деления h1 + и вырабатывает на своем выходе последовательность импульсов с частотой циклов входного сигнала. Блок 11 управления осуществляет фазировку делителя 12 частоты узкими управляющими импульсами, поступающими на его сигнальный вход. На третий сигнальный вход блока .

3 динамической памяти с селектора 10 синхросигнала поступает задержанный на длительность синхронизирующей комбинации входной цифровой поток. Запись информации в ячейки блока 3 дина-.. мической памяти осуществляется тактовой .частотой с выхода выделителя 1 тактовой частоты. Считывание информации из блока 3 динамическЬй памяти осуществляется станционной импульсной последовательностью,,вырабатываемой генератором 4 тактовых импульсов.

Временной детектор 2, подключенный ко вторым выходам блока 3 динамической памяти, определяет сдвиг.фаз, действующий между соответствующими импульсами записи и считывания информации.

При достижении сдвига фаз, равного тактовому интервалу станционной частоты, на третьем входе логического блока 5 появляется сигнал лог. "1" и схема переходит в режим ожидания сигнала согласования скоростей, вырабатываемого блоком 11 управления на определенной временной позиции, например, на границе цикла принимаемого сигнала. По этому сигналу логический . блок 5 исключает один тактовый импульс из стационной последовательно1420670 сти, поступающей на первый сигнальный вход блока 3 динамической памяти.

Благодаря этому осуществляется введение "дублирующей" посылки в передава5 емый сигнал, формируемый в блок 3 динамической памяти.

На входах приемной стороны дей-. ствует сигнал с введенными в него

"дублирующими" посылками и сопровож. дающая его тактовая последовательность, формируемые обычным регенератором (не показан) °

Приемник 6 синхросигнала осуществ ляет дешифрацию квазипериодического 1Б синхросигнала и соответствующую задержку принимаемого сигнала, подаваемого на третий вход блока 9 динамической памяти. Первый и второй делители 14 и 15 частоты имеют коэффи" циент деления, равный rn +n и выраба- тывают импульсы с частотой циклов импульсного потока, подаваемые, соответственно, на второй и третий сигнальные входы блока 13 управления. 25

Блок 13 управления формирует импульсы установки делителей 14 и 15 частоты и обнаруживает циклы, в которые введену "дублирующие" вставки, выра батывая при этом на своем втором вы 30 ходе сигнал исключения одного тактового импульса из тактовой последовательности. Исключение одного импульса осуществляется в логическом блоке

7 в момент поступления на третий вход З блока- 9 динамической памяти "дублирующей посылки т.е. эта посылка не записывается в блок динамической памяти. Считывание записанной информации осуществляется тактовой частотой 40 переданного сигнала, восстановленной блоком 8 фазовой автоподстройки частоты. На фиг.2 приведен пример выполнения блока 3 динамической памяти передающей стороны. Распределитель 4> записи, состоящий из первого регистра

17 сдвига и первого элемента 16 И из тактовой частоты подлежащего передаче сигнала формирует ряд сдвинутых во времени импульсных последовательнос- 5О тей, управляющих, записью информации ,в элементы 25 памяти первых ячеек 23 памяти. Частота каждой из сдвинутых по-. следовательностей меньше тактовой частоты в число раз, равное -числу первых или вторых ячеек памяти (E).

Информация, подлежащая записи, поступает..через третий сигнальный вход от селектора 10 синхросигнала, Тактовая последовательность считывания от логического блока 5 поступает на первый сигнальный вход. Второй регистр

18 сдвига и второй элемент 19 И образуют распределитель считывания, создающий импульсные последавательности, аналогичные импульсным последовательностям распределителя записи.

Считывание информации иэ элементов

25 памяти осуществляется через элементы 26 И. В первом элементе 21 ИЛИ. осуществляется сборка полного сигна. — . ла, включающего "дублирующие" посылки. Сигналы с одноименных ячеек первого и второго регистрав 17 и 18 сдвига через вторые выходы поступают на соответствующие входы временного детектора 2. Сигнал разрешения согла» сования скоростей, формируемый блоком

11 управления, через 4 сигнальный вход записывается во вторые ячейки 24 памяти и считывается импульсами, вырабатываемыми третьим регистром сдви га, на тактовый вход которого через второй сигнальный вход поступает тактовая последовательность непосредственно от генератора 4 тактовых импульсов. На выходе второго элемента 22

ИЛИ формируется сигнал управления работой логического блока 5.

На фиг,3 представлен пример выполнения блока 11 управления передающей стороны. В режиме установления син с хронизма отклики селектора 10 синхросигнала и импульсы с делителя 12 частоты, поступающие соответственно че-. рез первый и второй сигнальные входи, не совпадают во времени. Текущий импульс с делителя 12 частоты устанавливает триггер 31 в состояние "1", при котором первый .элемент 27 И открыт для прохождения отклика (от истинного синхросигнала или ложного).

Этот отклик, проходя через первыйрегистр 29 сдвига, вызывает сброс триггера 31 в состояние "0" и установку в начальное состояние делителя 12 частоты.В случае отклика,вызванноголожным синхросигналом, второй элемент 28 И не срабатывает, и импульс разрешения согласования скоростей не появится на первом выходе. Однако новая,фазировка делителя 12 частоты приводит к смещению импульса на втором сигнальном входе ближе к временному положению истинного синхросигнала. В процессе такого смещения наступает момент ; синхрониэм, когда импульсы на обоих

5 14206 входах второго элемента 28 И совпадут во времени, и на первом выходе блока управления начнет регулярно появлять . ся сигнал разрешения согласования скоростей.

Блок 13 управления приемной стороны, изображенный на фиг.4, служит для формирования импульсов согласования скоростей (исключение "дублирующих" посылок) на приеме. В режиме установления синхронизма на выходе накопителя 35 по входу в синхронизм — состояние лог. "О". При этом импульсы с вы-. хода второго делителя 15 частоты, по- 16 ступающие на третий сигнальный вход, проходят регистр 36 сдвига и комму- татор 37 и через четвертый выход по". ступают на сигнальный вход второго .делителя 15 частоты, который работает 2р . при этом в автономном режиме,,Импульсы, поступающие от первого делителя 14 частоты через второй сигнальный, вход (не сфазированные с синхронизирующим б сигналом)> устанавливают в состояние 25 лог. "1" триггер 38, при катарам на первый сигнальный вход разрешается поступление всех откликов от приемни" ка 6 синхросигнала (как от истинных синхросигналов, так и ложных) ..

При поступлении отклика от ложного. синхросигнала импульс со второго формирователя 40 импульсов вызывает переброс триггера 38 в состояние лог.

"Q При этом совпадение во времени . импульсов на входах третьего элемента 34 И не происходит и на втором выходе блока 13 управления импульса согласо" вания скоростей не появляется. Первый 4р делитель 14 частоты фазируется в этом цикле ложным импульсом, вследствии чего на выходе элемента 41 запрета появляется управляющий импульс, вызывающий сброс в нулевое состояние на- 45 капителя 35 по входу в синхронизм. ,От цикла к циклу происходит смещение

:фазирующего импульса к положению сии .хронизирующего сигнала до их совпадения, В последующих циклах элемент бр

41 .запрета срабатывать не будет, а будет появляться импульс на выходе первого элемента 32 И, вызывающий заполнение накопителя 35 по входу в синхронизм. Процесс оканчивается изменением сигнала на выходе накопителя

It

35 по входу в синхронизм на лог. 1 при котором коммутатор 37 пропускает на свой выход импульсы со второго °

70 6 элемента 33 И, вызывающие перефазировку второго делителя 15 частоты и затем появление импульсов разрешения согласования скоростей на выходе третьего элемента 34 И.

Одновременно с этим, через первые выходы блока 13 осуществляется подача управляющих сигналов на третьи входы приемника 6 синхросигнала, по которым разрешается формирование при наличии одиночных ошибок в истинном синхросигнале.

Импульсы на выходах первогои второго формирователей 39 и 40 имеют длительность в два.тактовых интервала с тем, чтобы не нарушалось совпадение импульсов при наличии "дублирующей" посылки.

При срыве синхронизма на выходе элемента 41 запрета-появляется импульс, устанавливающий накопитель 35 по входу в синхронизм в нулевое состояние, после чего повторяется процесс установления синхронизма, описанный вьппе.

Использование данного изобретения, по сравнению с прототипом, позволяет снизить требуемую пропускную способ-: ность канала связи за счет отсутствия дополнительного канала связи, в котором необходимо передавать помехозащищенные команды согласования скоростей и дополнительный синхронизирующий сигнал. Кроме этого, достигается-также некоторое упрощение устройства и связанное с ним повьппение надежности.

Формула из обр ет ения

Система для асинхронного сопряже ния импульсных потоков, содержащая на передающей стороне вьщелитель так.. товой частоты, выход которого соединен с тактовыми входами временного детектора и блока динамической памяти,генератор тактовыхимпульсов илогический блок, выход которого и выход генератора тактовыхимпульсов соединены соответственно с первым и вторым сигнальными входами блока динамической памяти, первый выход которого является выходом передающей стоРоны, информационным входом которой является вход вьщелителя тактовой частоты, а на приемной старане приемник синхросигнала, логический блок и блок фазовой автоподстройки частоты, выход которого соединен с первым входом й

ll«,J-й (9

Ух. ий

bM.

ыйых.

1-и

СУ

Ух

U гх.

Ф02 Я

7 14206 блока динамической памяти, второй и первый выход которого подключены соответственно к выходу логического блока и первому входу блока фазовой автоподстройки частоты, причем инфор. мационным выходом системы, сигнальным и тактовым входами приемной стороны .являются соответственно второй выход блока динамической памяти и первый и 10 второй входы приемника синхросигнала, отличающаяся тем, что с целью улучшения использования пропускной способности канала связи, введены на передающей стороне селектор 15 синхросигнала, блок управления и делитель частоты, тактовый вход которого объединен с выходом выделителя тактовой частоты и тактовыми входами блока управления и селектора синхро- 2р сигнала, сигнальный вход, первый и второй выходы которого подключены соответственно к входу вьделителя тактовой частоты, перому сигнальному

,входу блока управления и третьему 25 сигнальному входу блока динамической памяти, четвертый сигнальный вход, вторые и третьи выходы которого соединены соответственно с первым выхоpом блока управления, первыми сигналь- 3p ,ными входами временного детектора и

70 8 первым входом логического блока, второй и третий входы которого подключе» ны соответственно к выходу генератора тактовых импульсов и выходу времен» . ного детектора, причем вторрй выход и второй сигнальный вход блоКа управ ления соединены соответственно с сиг1

I нальнь м входом H выходом делителя ча" стоты, а второй сигнальный вход вре-: менного детектора подключен к третьему выходу блока динамической памяти, а на приемной стороне введены блок; управления, первый и второй делители частоты, тактовые входы которых и тактовый вход логического блока объединены с тактовым входом приемника синхросигнала, первый и второй .выходы и третьи входы которого соединены со» ответственно с третьим входом блока динамической памяти, первым сигнальным входом и первыми выходами блока управления, второй и третий сигнальные входы и второй, третий и четвертый высоды которого подключены соответственно к выходу первого делителя частоты, выходу второго делителя частоты, сигнальному входу логическо.го блока и сигнальным входам

I первого и второго делителей частоты.

&p

С оста вит ель В . Зенкин

Редактор А.Долинич Техред М. Ходанич Корректор М.Пожо

Заказ 4334/57 Тираж 660 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4