Устройство для обмена информацией

Иллюстрации

Показать всеРеферат

Изобретение относится к оГласти автоматики и вычислительной техники и может быть использовано в устройствах , обеспечивающих информационный обмен с ЭВМ по двухпроводному интерфейсу ввода-вывода. Цель изобретения - повьшение надежности работы устройства за счет уменьшения количества оборудования и линий связи между блоками устройства. Устройство для обмена информацией содержит элемент ИЛИ 1, блок формирования сдвигающих импульсов 2, регистр сдвига 3, блок формирования флагов 4, два блока памяти 3, 6, шинный формирователь данных 7, элемент НЕ-ИЛИ-НЕ 8, блок формирования управляющих сигналов 9, элемент И 10, три инвертора 11,12,13, 5 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 С 06 F 3/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4 173538/24-24 (22) 14.11.86 (46) 15.09.88. Бюл. У 34 (72) А.В.Стеняев, Г.С.Степанов, Г.В.Майзель и Т.М.Ермолаева (53) 681.327.21(088.8) (56) Устройство для обмена информацией РИМ-602 620.101.ТО.

Устройство для обмена информацией

РИН-608С 6 20. 1 36-09T03 . (54) УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМА"

ЦИЕЙ (57) Изобретение относится к осласти автоматики и вычислительной техники и может быть использовано в устрой„„SU„„1424001 A1 ствах, обеспечивающих информационный обмен с ЭВМ по двухпроводному интерфейсу ввода-вывода. Цель изобретения — повышение надежности работы устройства эа счет уменьшения количества оборудования и линий связи между блоками устройства. Устройство для обмена информацией содержит элемент ИЛИ 1, блок формирования сдви гающпк импульсов 2, регистр сдвига 3, блок формирования флагов 4, два блока памяти 5, 6, шинный формирователь данных 7, элемент НЕ-ИЛИ-НЕ 8, блок формирования управляющих сигналов 9, элемент И 10, чри инвертора 11, 12, 13.

5 ил.

Изобр< теltlfF о г>1<>сtfT< Я к лн . < мати ке и вьгчислит льн< и техн>гке и ttn>f < т быть использован, в устрогиствлх, обеспечивающих инфо,>мационный обмен с >ВМ по двухпров<>дному интерфей .у ввода — вывода.

Целью изобрет гния является п<>вь<шение надежности рлботь> устройства путем уменьшения к<>личества <>боруловл- 10 ния и линий свя 3tt м< жду блоками устройства.

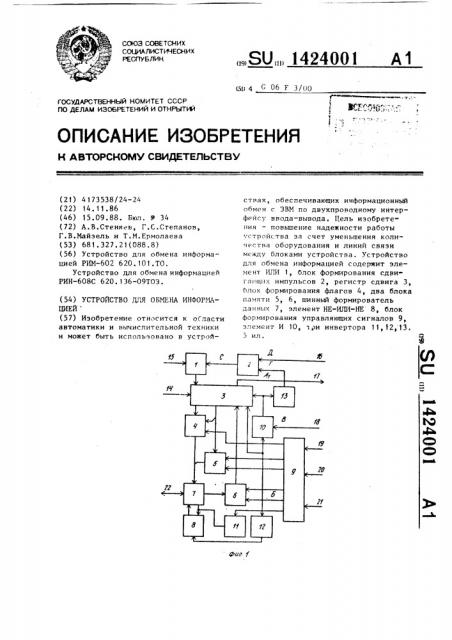

На фиг. 1 при> едена блок-схемл устройства лля обмена информлцией; нл фиг. 2 — функционлльная схема блока 15 формирования сдвигаюших импульсов; на фиг. 3 — то же, блока формировлния флагов; на фиг. 4 — временные дилграммы, иллюстрирующие работу предлагаемого устройства при приеме ин- 20 формации; на фиг. 5 — то же, при передаче информации.

Устройство для обмена информацией (фиг. 1) содержит элемент И 1И 1, блок

2 формирования сдвигающих импульсов, 25 регистр 3 сдвига, блок 4 формирования флагов, два блока 5,6 плмяти, шг<нньггt формирователь 7 длнных, элемент НЕИЛИ- Е 8, блок 9 фор;пгроваггия управляющих сигналов, клемент И 10 и три 30 инвертора 11 — 13. Вход 14 регистра 3 сдвига соединен с выходом внешнего устройства (не поклзлно). Выход элемента 11г)И 1 соединен с вг.>рым входом регистра 3 <.д:>гггл. Выход б><окл 2

35 формирования сдвиглющих импульсов соединен с входом элемента ИЧИ 1, другой вход которого является входо>ч 15 устройства. Тактовый вход 16

40 пульсов соединен с выходом внешнего устройства (не показано) микроЗВМ для приема высокочастотных тактовых импульсов. Первый выход регистра 3 сдвига соединен с первым входом бло45 ка 4 формирования флагов и вторым входом первого блока 5 памяти, первый вход которого соединен с третьим выходом блока 9 формирования управляющих сигналов. Первый выход блока 9

Ф

50 формирования управляющих сигналов соединен с входом первого инвертора 11, выход которого соединен с первым входом элемента НЕ-KM-ÍE 8 и вторым входом шинного формирователя 7 данных, первый вход которого соединен с выходом как блока 4 формирования флагов, так и первого блока 5 памяти.

Пятый выход блока 9 формирования упрл I>Itге>< с первым г<х< дом . л< мс нта И 10, третг,>гм входом

Г>е I lf< тра 3 сдвига, третьи : входом . тсрог< блока б плмяти и входом второе<. инвврторл 12, выход которого .negtfIfeIf с вторым входом элемента НЕННИ-НF 8, выход KoTop<>t соединен с третьг<м входом шинного формирователя 7 дл >ных, t

<- tfTopIIM входом второ"о блока 6 памяти, первый вход которого соединен с ше<-тым выходом блока 9 формирования упрлвляющих сигналов. Второй выход блока 9 формирования управляющих сигнал»в соединен с вторым входом блока

4 формирования флагов, третий вход к< торогс соединен с третьим вьгходом регистра 3 сдвига, выход 17 регистра 3 сдвига является выходом устройства и соединен с входом внешнего устройства (не показано). Четвертый выход блока 9 формирования управляюIIttfx сигналов соединен с третьим входом первого блока 5 памяти. Второй вход 18 элемента И 10 является четверты . входом у< тройства для приема тлкт<>вых импульсов. Вьгход элемента

И 10 соединен с входом третьего инве1>горл 13 и пятым входом регистра 3

<дви"л, четвертый вход которого соединен с вг>гходом второго блока 6 памяти. Выход третьего инвертора 13 соединеч с вторым входом блока 2 формирования сдвигающих импульсов. Первый, второй и третий входы 19 — 21 блока 9 формирования управляющих сигналов соелинеtttl с соответствующими выходами мик;>оЭВМ (не показана), л вход-выход

22 t o формирователя 7 данных соединен с соответствующим входомвыходом микроЭВМ, которая не входит в состав устройства.

".,ñëè учесть, что входная.информация содержит одиннадцатиразрядный последовательный код, то регистр 3 сдвига может быть выполнен на базе трех микросхем 133ИР1, соединенных последовательно, причем входная информлция поступает на информационный вход первой микросхемы (первый вход

14 регистра 3 сдвига), а выходная информация должна передаваться с третьего вьгхода третьей микросхемы (второй выход 17 регистра 3 сдвига).

Блок 2 формирования сдвигающих импульсов можно представить в виде совокупности элементов: трех триггеров 23 — 25, элемента И-HE 26, эле142 iin01 мента И 27 и счетчика ЗЯ импульсон (фиг. 2), где С-вхол "1" первого триггера 23 соединен с. вьгходсм Тре тьего инвертора 13 (на D-вход этого триггера поступает пс ствянный уровень И ло5 гической единицы), перный (прямой) выход первого триггера 23 соединен с К-входами второго 24 и третьего 25 триггеров и вторым входом элемента

И-НЕ 26, на первый D-вход которого от микроЭВИ поступают нысокочастотные импульсы (фиг. 1, первый вход 16 блока 2 формирования сдвиговых импульсов) . Выход Е элемента И-HF. ", 6 соеди15 нен с С-входами втор го 24 и третьего 25 триггеров, первый (прямой) выход второго триггера 24 соединен с D-входом третьего триггера 25, первый (прямой) выход 3 которого соеди20 нен с первым входом элемента И 27, второй вход которого соединен с вторым (инверсным) выходом Ж второго триггера 24. Вт рой (инверсный) выход третьего триггера 25 соединен с

D-входом второго тригг ера 24, выход

С элемента И 27 соединен с первым входом элемента ИЛИ 1 и первым входом счетчика 28 импульсов, коэффициент пересчета которого ввиду того, что выходная информация по количеству входящих в нее бит соответствует входной, равен одиннадцати. Второй (инверсный) выход первого триггера 23 соединен с вторым входом счетчика 28 импульсон, ныход которого в свою очередь соединен с R-входом первого триггера 23.

Блок 4 формирования флагов может быть реалиэонан аналогично функцио40 нальной схеме, привелг иной на фиг. 3, и в соотнетствии с этой схемой состоять иэ элемента 29 контроля, дешифратора 30 управляющих слов (приказов), инвертора 31 и шинного формирователя

32 флагов, которь.й имеет в рассматриl5 наемом случае только три выхода, где на первом выходе 33 формируется потенциальный сигнал, уровень которого соответствует уровню логического нуля в случае, если поступившая инфор50 мация не содержит (к примеру) нечетного количества двоичных (логических) единиц; на втором выходе 34 формируется потенциальный сигнал, уровень которого coOTRf тствует уровню логи55 ческого нуля в случае, если поступиншая информация содержит в c лужсбной части признак команды (указания), на тр ° тьем выходе 35 формируется потенциачьный сигнал, уровень которого соотнетствуct уровню логическогo Hv ля и случ . е, если поступившая информация содержит код управляющего слона (приказа). Входы элемента 29 контроця и леши "затора 30 прнказон, сгмеленные а фиг, 3 буквой "d", соединены с соотнетствующими разрядами перв го выхода сдвигоного регистра 3, остальные два разряда которого соответственно соединены с входами эле 1ента 29 контроля, отмеченными на фиг. 3 буквами "К" и "1 ". Третий вход блока 4 формирования флагов отМс ÷åн на фиг. 3 буквой и однонременно янляется входом элемента 29 контроля, иннертора 31 и управляющим входом дешифратора 30 приказов. Выход элемента 29 контроля соединен с первым входом шинного формирогателя 32 флагов, второй вход которого соединен с ньнодом инвертора 31. Выход лешифратора 30 приказов соединен с третьим входом шинного формирователя 32 флагов; четвертый вход которого соединен с третьим выходом блока 9 формирования управляющих сигналов. Выходы шинного формирователя 32 флагов (выход блока 4 формирования флагов) соединены с соответствующими разрядами первого входа шинного формирователя 7 данных.

Элемент 29 контроля может быть выполнен на микросхемах 133ИП2 и 133ЛП5.

Шин .ый формирователь 32 флагов может быть выполнен с использованием буфера данных 585АП26. блинный формирователь 7 данных ввиду того, что информационная часть слова содержит восемь значащих разрядов, может быть реализован на двух буферах данных 585АП26.

Первый 5 и второй 6 блоки памяти могут быть выполнены на программируемых ПЗУ 556FT5

Устройство для обмена информацией работает в двух режимах: в режиме приема осуществляется прием информации, ее преобразование, а если это необходимо, перекодирование и передача информации для дальнейшей обработки в микроЭВИ; н режиме передачи осущестнляется прием информации из микроЭВМ в параллельном коде, при необходимости перекодирование и выдача этой информации с одновременным пре142 001 образованием параллельного ксд,. г последовательный.

Извес1но, что информация, ко орая поступает от ЭРМ пг линиям связи двухпроводного двунаправленного интерфейса, кодируется в соответ(твии с табл. 1 ГОСТ 19768-74 (код ДКОИ).

Известно и то, что микроЭВМ осущсствляет обработку алфавитно †цифров ин- lO формации, закодированной в соответствии с табл. 2 ГОСТ 19768-74 (код

КОИ-8). Таким образом говоря о переУ кодировании в режиме приема, которое производится на первом блоке 5 памя- 15 ти, следует иметь в виду перекодирование из ДКОИ в КОИ вЂ, а говоря о перекодировании в режиме передачи, которое производится на втором блоке Ь памяти, следует иметь в виду переко- 2О дирование из КОИ-8 в ДКОИ.

В режиме приема устройство для обмена информаш ей работает следующим образом (иллюстрация (работу устройства в этом режиме иллюстрирует 25 фиг. 4) .

В регистр 3 по входу 14 поступает информация трех видов — команды (указания) управляющие слова (приказы) и алфавитно-цифровая инфс.рмация (дан- 30 ные). Ec: и первый вид отличается от двух последующих присутствием логической единицы вс втором бите информационного слова, то отличие прика-а от данных определяется непосредственно информационной частью этого слова, т.е. только кодом (гм. табл. 1 ГОСТ

19768-74), В связи с этим в блок 4 формирования A rar ов входит дешифратор 30 приказов, который осуществляет 4п в предлагаемом устройстве разделение приказов и данных.

Первоначально в регистр 3 поступает указание. На фиг. 4 (диаграмма А) приведен последовательный код, кото- „45 рый поступает на вход 14 регистра 3.

Одновременно на второй вход регистра .3 через элемент ИЛИ 1 с входа 15 поступают сдвигающие импульсы (фиг.4, диаграмма Б). В момент времени Т1 на вход 14 регистра 3 поступает первый импульс информационного слова, а в момент Т2 Kðî3ÂÌ имеет возможность осуществить прием (чтение) этого слова. На диаграммах В1...В11 (фиг.4) показаны изменения сигналов на каждом из одиннадцати разрядов первого выхода регистра 3 по мере поступления информации. На фиг, 3 соответствующи: разряды этого выхода отмечены г у,.ими К (контрольный разряд), P (сзужебьп и — наличие слова) и d (воvc",и,, разрядов, составляющих код

ДК И), а буквой l (служебный — наличи . указания) отмечен третий выход регистра 3. На фиг. 4 (диаграммы

В1...В11) теми же буквами отмечены состояпия соответствующих разрядов регистра 3. Таким образом, в регистре 3 производится преобразование посл довательного двоичного кода (диаграмма А фиг. 4) в последовательный код (диаграммы В1...В11 фиг. 4), котсрый можно представить в виде двоичного числа " 1 1 И О И И О 1 И 1 1".

В- rräó того, что количество логических единиц в этом коде (числе) нечетное

Градно пяти), на выходе элемента 29 контроля формируется потенциальный сигнал, уровень которого соответстнус т уровню логической единицы, и поступает на первый вход шинного формирователя 32 флагов; на втором бите информационного слова присутствует бит, содержащий информацию о логической единице. На третий вход шинного формирователя 32 флагов поступает потенциал логического нуля, так как сигнал, поступающий на управляющий вход цешифратора 30 приказов, своим потенциалом закрывает выход этого деи:ифратора.

При передаче информации устройстьом для обмена информацией происходит следующее.

На первый вход 19 блока формирования управляющих сигналов поступает код адреса, затем на второй вход 20 блока 9 формирования управляющих сигналов поступает сигнал управления, который в совокупности с поступившим ранее кодом адреса вызывает на первом и третьем выходах блока 9 формирование сигналов, длительность которых определяется длительностью сигнала, поступающего на второй вход 20 этого блока, причем на первом выходе формируется сигнал, уровень которого соот- 1 ветствует уровню логической единицы, а на третьем — уровню логического нуля. Сигнал, поступающий с второго выхода блока 9 формирования управляющих сигналов на второй вход блока 4 формирования флагов, разрешает формирование на выходе блока 4 (на выхс дах 33, 34 и 35) соответствующих потенциалов . Вниду того, что на выходе

1 . <, i11> 1 блока 4 Фор.»и1», il..lиия <1!.i, 1. !i t i.,<1- и на выходах обоих fijl<>f (>H » б и IMFI ги и выходе ши и и<> гс <>»p,"lit pi >F<;1 1 < ля 7 дл><в ных) информация ф(р lift>",< т<" í н IIHF>< рс—

Hok» коде, на перв< м нх<>цс шинн< г< формирователя 7 длин >х п ннпяс ГГH двоичный Bocf>MI»t!IITHI fit код "Х 1 0 1

Х X Х Х (симво1 Х (<нлчает, чт(> разряды, отмеченнь>е этим знаком, могут быть прс>и >вольными) . 1!а второй и третий входы шинного QopwHpoBcfr«ля 7 данных с первого выхода блока 9 формирования упрлвпян-ц(их сигналов и рез первый инвертор 11 и элемент НЕИЛИ-HE 8 (фиг. 1) постчплн>т сигнллы, уровень которых cooTB(. гст«уеf урон— ню логического нуля. Таким образом создаются условия, когда »1+cрмация, поступающая ил пс рный нхоц шинного формирователя 7 данных, передается на вход-выход 22 этого шин«с го формиронателя, но при этом предварительно иннертируется. Эта информация (в рассматриваемом случас двоичный код "Х 0 1 0 Х Х Х Х") поступает на соответствующий вход-ныхоц микроЭВГ1.

После анализа полученного кода микроЭВГ! определяет, что в регистр 3 поступило указание (третий по старшинству бит содержит "1") с прлнильнси четнбстью (второй по старшинству б1»7 содержит 0"), следовательно, необходимо считать информацию, находящуюся в сдвиговом регистре, т.е. непосредственно код ука.>ан1»я. Так клк кодов указаний в табл. 1 ГОСТ 19766-74 нет, то производить операцию перекодирования не следует.. .1икроЭВГ1 выдает на первый вход 19 блока 9 формирования управляющих сигналов соответствующий код адреса, который сопровождается сигналом управления, поступающим на второй вход 30 этого блока 9. На первом и четвертом выходах блока 9 формирования управляющих сигналов формируются сигналы, длительность которых равна длительности сигнала управления на втором входе 20 блока 9, а полярность соответствует уровню логической единицы. Сигнал, формируемый на четне! том выходе блоа 9 формирования управляющих сигналов, поступая на третий вход первого блока 6 памяти, открывает выход этого блока. Ка второй нход блока 6 памяти с первого выхода регистра 3 поступает двоичный восьмибитный код (диаграммы В2...В9 на фиг.4), а на первый вход — потенциал логической единицы,,«г.; .<и ф р 1 11>V< те я нл тр г. < м Г<ых<>Г 1. 1,;1 9 ф<>р; »роfi;1!Ii! H vHГ>а<лян щих (11.!<.1 i >B, В .>т(м с:>учло нл I>f"х, це

«рн< 1 бл<>1 л 5 плмя Т11 А«рмilp; Bтся

1,> Г >не fi д, »то и нл Ico fill(;>и:1(>МУ IIPO цех: >1и Г oTHpkiBлние н сцH

<1>; р <ир;1<лт(ilH 7 длн — 1<ЫХ(ЦЛ ШИН— иых, и и нфо рЭБГ1, Л1»ало10 Н!Л Illÿ Ili p(Дсlн ГС>» и МИКрс г <ч иым об>рлзом ос 111(ств:1

;<;>и:1 1> f»f(poЭВГ! IIIIOp!»BII лян<ш«м слоне (приказе). яется переии об упрлн-!

lри передаче жс . Един > > ННЬ1Х BC<+ !1РОИСХОДИ Г тсl

BilTf H ItIoc тнлццатиричнсм ниде

30 что соответствует строчной б уп:,ii рус. кого лпфлнитл P. Тогда нл

>ыход< первого Gjlof« 5 илмяти формир;егся на время присутствия на треть<.".I i г нхо,(е потец>»иллл логической

<;(ин>1>п,< цноичнь<й коц "2!1< " (что так35 ж(<сот« тстнует f!vKBc <, Ho уже в

l i де !»О1! 8) Э Гот ко7 HB ВхОд(. ныхo д" 22 цг»нного формирснателя 7 даншпс ин»<ерт> руется ("D2 ") и пс редается н м>»к р о Э В!1.

40 Б режиме передачи устройство работле> следующим образом. а

l!íf1циаToром взаимодействия в этом режиме работы является микроЭВГ1, которля, переданая на первый вход 19

45 блока " формирона»ия управляющих сигнл IBB coOTBEтствс>ю»ций код адреса, а

Г»л трети»» вход 21 этого блока — второ 1 управляющий сигнал, одновременно выдает на вход-ныхoп 22 ц»»»нного формирователя 7 данных информацию, B основном закодиронанн<7Yl B соотB=тстнии с табл. 2 ГОСТ 19768-74 (ЕО1! — 8).

При поступлении на перньп» 19 и

55 трет и 21 входы блока 9 формирования у..:ранляющих сигналов соответствующих, с:»гиалов, а именно кода адреса и упраг>Г<яющего сигнала, на его пятом и !c cTow выходах появляются сигна15 i т«i ни >е от<и:чие — нл третьем выходе блс кл 9 формирования;.и;лг<пян><цих еиг <алов формируетс я Гигнлп, пслярF»<>c Tf> к >торого сост«ет<-т»>у(. т IloHHp

)loc ги логич< скогс нуiтом слу>л< г первый ».пок 5 плмяти г»ро>»з водит и(рек >;»ировлние кода д;»нных, поступающс го нл его первый нхсд, который, клк отме »л.пос». г>лнее, должс»< соотнетствоН 1 1 Ь (>ли < МУ I i 1 ДЕЙС 1 Flit T(Л Ь fll!Х Н ОД(>Н

i.of> 1. 1 Ë,Т 19768- ч. 11, грим< р, нл пс !>1«,, и 1>х(>д f1<.pk памяти и<>стуll;l(т коц (н IIHB(pell< .1 1:»це), н<>т рый цля удобстнл и; жн< предста1-4 .<()n!

ЛК(,, (Il!T<<ЛЬНО< ТF 4 ) l < Р<ГХ )(Г;,:,-Г< т—

СЯ ДЛИТ Е:(ЬН() (T I h) . »1Р Л <3 »Л. 0Г<с l i»: l 3 лл, поступлнхпс г(»1<3 1()х ). им )

IIf PE I(0ДГ»РОВЛ Т < П<",) Е<т 3 ВЛ Г «») Ю гlвф<)P f i

Цию нл tfIE c том вl гхол(<г)о !>м»»Р с г Я сигнал, ур<эвснь к< т< р<>го с оот в:-гс твует уровнк> логit

TI»I)HOB СЛУЧаЕ Í l .)тоМ ВЬГ(С<Де УP; »И fif сигнллл oc THE тся «»с,1:)мен«гым) . l!3»гя— том выходе блока 9 в )то <<р< tlH форм«»руется сигна", урс)в-нь ко" Ор<>гс < оответствует уровню логиче(кой е;п»вЂ” нины. Этот г tf1-t»a..t чер» s второй l!!t— нертор 12 и эле"..«Ftx !11.-И Ilt-1Н. 8 ffcc—

10 туплет в инв .р< I!<» видс нл Tt)còttt» вход пн»нного форгн»ровлтел» 7 данг, х, на второй гхо 1 кс торогс) в эт;>и время

Г!Ос. тУпле т с «

ЧЕСКОй ЕДИНИЦЫ, ПРС Де»(Я T условия пр эхождег»!t«I 1»1»фор)»лц(»и через шинн(<й формировлтсль 7 данных. В этом 25 с гучае информлция, поступг(ю(<(-тя нл нхоц-выход форм(.p(овлтеля 7 после 1(нВЕРТНРОНЛ Нl»Я > IIE P ЕД »ЕТСЯ f!Il Г О 1 ЫХОД .

Итак, если микроЭВ!! передает i113« i»1(нгй код "59,, " нл вх<-ц-в((ход ши:1 1< r <) iPopмиронлтеля 7 данных, то на (этором входе второго эл(мента 6 плмяти на время нахожде:гия сигнллл и (третьем его входе, уроне(ь котoporo co<)тв-тствует уровню лога ческой e731!Flit<(It, буC дет присутствовлть код "Аг> ". Тлк как второй блок 6 плмя ги о<-ущсствляет перекодирова»п(е информации из кода КОИ-8 В КОд Д1.1)И (В СпуЧав 1(а<(Ичия на третьем еl c входе ур )ння логического нуля), тс на его вьгходе появляется код "171 ", инверсия которого ("Е8 г ") в соответствии с тлбл.

ГОСТ 19768-77(опислнг(прописной буквой латинского алфавита " (код нл

45 выходе второго блока 6 памяти формируется в инверсном виде). Этот код поступает на четвертый нход регистра 3. В момент времени t, (фиг. 5) происходит параллельная запись этого кода (диаграммы А9...А?) н рег.истр 3.

Одновременно с записью эт(эго кодл в соответстнующис разряды реги<.трл 3 в два его, старпп(х разряда (диаграммы

А11 и Л10) и в младший (диаграмма Л1)

55 соответственно автоматически злгись(ваются два служебных признака (иервьги из которых содержит инверсную информацию о логической единице, а

F3 t пои —:<нв рсг<у(() ин(1)ормг»цг»н) о логи(=ск м нул(:) и контрольньп» рлзряп, < к<)е < o1((pro«ft»e кот<)рог о опре1l(.< л(3 гся к э »и геством логических еди-!! «1<,><)р. »лция о которых содержится н - с-тл.l!,«11»х десят(» разрядах (суммлр1(ос .; э 11» гествo разрядов — бит информлг)и .нного слова — должно составлять н<,i тно< число, поэтому, как видно из фиг. 5 (диаграмма Аl), этот разря,, содержит I»HBcpc!lóþ информацию о t,)ãè÷(ско(» единице) . Иа фиг. 1 не пог<лзлн блок, который осуществляет лг»томлтг»ческое приформиронание служ(рных и контрол»,ного разрядов. Им11 <,,с, формируемый «(л пятом вьгходе б.;1;л 9 формирования управляющих сиг«гл:.<:13 (фиг. 5, диаграмма Б), поступает нл третий вход регистра 3 и пер13«пй вход элемента И 10. В момент с гриходом очередного тактового импул(,сл на второй вход В (или 18) элементл И !О на его выходе формируется

Одиночный импульс, передний фронт кот< р;гo осуществляет операцию записи информлц(»и н регистр 3, которая формируется прг» этом на всех одиг»гглдцати выходах этого регг»стра (фиг. 5, дилгрлммы А1...А11). Одиночный импульс, формируемый на выходе элемента И 10, поступает также на вход тре" l сго иннертора 13. Импульс, формирус)1(,п(нл его выходе Г (фиг. 5, диа:-рлммл Г), поступая на второй вход б.(окл 2 формирования сдниглющих импульсов (фиг. 1 и 2), осуществляет перевод первого триггера 23 в "едиI3«(«IIОе состояние (это происходит

IIo заднему фронту импульса Г в Мо мент времени tz), что приводит к поянлс нию на пергом (прямом) выходе триггера 23 уровня логической единицы. Тлким образом, создаются условия прохождения" высокочастотных импульсов (фиг. 5, диаграмма Д), поступающих нл первьп вход 16 блока 2 формирования сдвигающих импульсов, через элемент И-НЕ 26. На выходе Е элемента 26 с этого момента времени формиру«стся импульсы (фиг. 5, диаграмма F), первый из которых своим задним фронтом переводит второй триггер 24 в

"единичное состояние, что приводит к появлению на его нтором (инверсном) выходе уровня логического нуля (,фиг. 5, диаграмма Ж), а второй — в единичное состояние третий триггt. р 25,,что приводит к появлению на

11 1-4 240 его первом (прямом) E»l,l,î Ie ург ння I»l гической единицы (фиг. 5, д»»аграмма 3). Третий импульс., фсрмирусмы;» на выходе Е элемента И вЂ” НЕ 26, вновь

5 приводит к появлению на втором в»,»ходе второго триг.гс ра 24 уровня логического нуля, что г: «Во»о ач .ре дь приводит к появл«сп»ю !»а выходе С элемента И 27 переднего фронта сдн»»гового 1о импульса (фиг. 5, диаграмма С), который формируется на выходе блока 2 формирования сдвигаюшн импульсов и через элемент ИЛИ 1 поступает »»а второй (сдвиговый) вход регистра 3. Чет- 15 верть»й импульс, формируемый »»а выходе Е элемента И-НЕ 26, вновь устанавливает третий триггер 25 в "нулевое" состояние, которое характеризуется тем, что на первом (прямом) выходе этого триггера появляется уровень логического нуля (диаграмма 3 на фиг.5), который способствует тому, что в мо1мент времени t на выходе С элемен3 та И 27 формируется задний фронт 25 сдвигающего импульса (фиг. 5, диаграмма С), которь»й, во-первых, поступая на второй вход регистра 3, осуществляет сдвиг информации (направление сдвига от младшего разряда Af к стар- 3< шему А11), хранящейся в этом регистре, во-вторых, поступая на счетный вход счетчика ?8 импульсов, осуществляет увеличение его содержимого на единицу (до этого момента все раз35 ряды этого счетчика быпи в нулевом состоянии). Таким образом, на выходе

17 (А11) регистра 3 происходит изменение информации, то есть осуществляется передача первого бита информа- „ ционного слова. Следовательно, четыре импульса, формируемых на выходе Е элемента И-НЕ 26, осуществляют передачу одного бита информационного слова. Поэтому для передачи одиннад45 цати бит, составляющих информационное слово, требуется 44 подобных импульса (фиг. 5, диаграмма Е). Диаграмма А 11 (фиг. 5) иллюстрирует таким образом характер изменения на

50 втором выходе 17 сдвигового регистра 3 (цифрами "1" и "О" показано логическое содержание каждого бита передаваемой информации). В момент времени t, когда на счетный вход счетчика 28 импульсов поступает один55 надцатый сдвиговь»й импульс, по заднему фронту которого содержимое счетчика 28 импульсов принимает значение

12

11,: тг прин»лит к форм»»1п»ва»»»»ю на с г с в» »холе сигнала, уровень которогс соо гнс тствует уро»»ню логи « ского нуля, котор» г»», поступ»»в»»а с -вход и«»JE»oi Tpl»I г«ра 23, переводит по1! II

«", ..IEEE»E» Г» НУЛ«ВО«(ИСХОЛ»»г «! СОС— тоянпс, что в.дст к созданию условия нс п» e!хожлс гп»я высокочастот»пгх импульсон »фнг, 5, диаграмма Л), которые пссгупают на первый вход 16 блока 2 фор. п»рования сдвигающих им»»ульсов черо l элемент И-НЕ 26. Потенциал, фг рм»груемый на втором (инвс рсном)

»birnam«пс рвого триггера 23, производит установку содержимого счетчика

?8 импульсов в нулевое состояние.

Ф о р м у л а и з о б р е т е н и я

Устройство для обмена информацией, содержащее элем«нт ИЛИ, один вход которого является первым тактовым входом устройства, а другой сослинен с выходом блока формировагп»я сдг»игаю:ilI»x импульсов, первый вход которо гo является вторым тактовым входом устройства,выход элемента ИЛИ соединен с тактовым входом регистра сдвига, вход последовательного ввода которого является посл«дAâàT«Jlü»»û»» информационным входом устройсTBë, первый информационный выход регистра сдвига со«динен с первым информационным входом блока формпр вания флагов, и с информационным входом первого блока памяти, второй информационный регистр сдвига соединен с вторым информационным входом блока формирования флагов, выходы которого соединеHEE с выходами первого блока памяти и с параллельным входом IIII»E»s»oi n формирователя данных, вход-вь»ход которого является последовательным и »формационным входом-выходом устройства, вход управления выдачей информации шинного

\ формирователя данных соединен с выходом первого инвертора и с первым входом элемента НЕ-ИЛИ-НЕ, вход выборки кристалла шинного формирователя данных соединен с выходом элемента НЕИЛИ-НЕ, второй вход которого соединен с выходом второго инвертора, вход первого инвертора соединен с первым вьгходом блока формирования управляющих сигналов, второй выхо;» которого соединен с входом выборки кристалла блока формирования флагов, третий и четвертый выходы — сос твс тственно!

3 14240 с первым и вторым входами выборки с входом второго инвертора и входом разрешения параллельного ввода информации регистра сдвига, первый вход блока формирования управляющих сигналов является входом кода адреса устройства, второй вход — первым входом синхронизации устройства, третий вход — вторым входом синхронизации устройства, выход третьего инвертора соединен с вторым входом блока формирования сдвигающих импульсов, а вход четвертого — с входом параллельной записи регистра сдвига, третий информационный выход регистра сдвига является последовательным информационным выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устрой01

14 ства за счет уменьшения количества оборудования и линий связи между блоками устройства, в него введены дополнительно элемент И и второй блок памяти, первый и второй входы выборки кристалла которого соединены соответственно с пятым и шестым выходами блока формирования управляющих сигналов, информационные входы — с выходами шинного формирователя дан" ньгх, выходы — с входами параллельной записи регистра сдвига, один вход элемента И соединен с пятым выходом блока формирования управляющих сигналов, другой вход является третьим тактовым входом устройства, а выход элемента И соединен с входом параллельной записи регистра сдвига.

8l

82

Ю

84

86

87 вв

89

8/О ви

ri

ФигС

14240О1

A f — 1- -1 — (- - - - +—

А2 — 1 — - 1 — ф — — 1ду

А4

А5

Аб

47

49

Af0 г

Г !

I I д JJ4lUJlllliJJIIJIJ !

E 1тпттп р 7ПТПТПП ТГП

Ж

С (1

Составитель С. Кулиш

Редактор Л.11а инская Техред Л,Олийнык Корректор П.Пилипенко

Заказ 4687/50 Тираж ".04 Подписи.эе

В11ИИПИ Государственного комитета СССР н,п. лал изб Г1ретений и открытий

1!";935, Москва, Ж-35, Раушская пао., д. 4/5

Прои «с дст енно-:н .1игpлфиче -кое предпри ятие, г. Ужгор. д, ул.. 1роектная, 4